【RX62N自学系列】网卡驱动开发

最近在捣鼓瑞萨的RX62N开发板,学习了一些网络方面的知识。我的计划是先学习网卡驱动开发,然后学习协议栈的移植,进而学习协议栈的裁剪等高级内容,首先还是驱动开发吧。

我使用的是RX62N开发板,瑞萨造,加强了网络能力,比较适合通信类的开发。板子上集成了LAN8700i网卡芯片,非常小,肉眼不容易看清楚啊。本次学习的所有资料都是日语和英语,截图也都是日语文书中的原图。

第一部分:梳理概念。

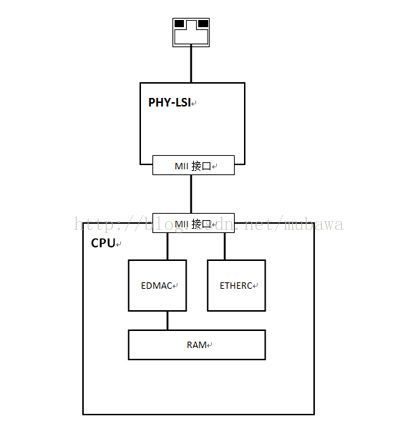

大学学习了TCP/IP协议的大体框架,觉得物理层,链路层等都是很遥远的,或者说根本不需要自己去思考,拿着用就行了,但是现在就必须深入的去了解,悲剧啊。在RX62N的开发板上,LAN8700i承担了物理层的部分,代号PHY-LSI,也就是物理层芯片的意思,它负责网络通信的物理层。在RX62N的主芯片上有一个ETHERC的模块,负责链路层,也就是MAC地址层。它负责将链路方面的协议包生成和转发。

第二部分:MII究竟是个啥

关于这部分,都是网络上抄来,整理一下就成的。MII,media independent interface,媒体独立接口。它的一头是MAC链路层芯片,另一头是物理层芯片。也就是一头是是数据源或者说是控制器,另一头是与介质相关的Tranceiver。

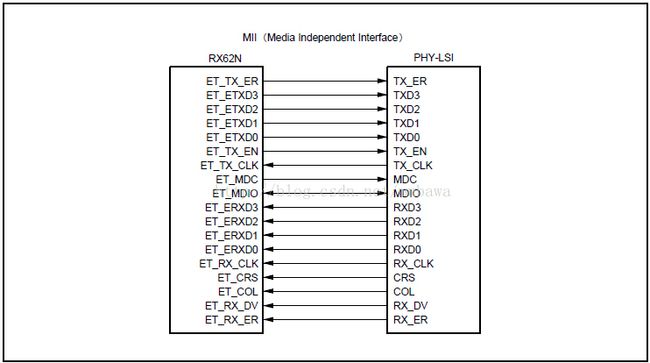

MII一共有16根线:

Tx_CLK/Rx_CLK:分别是Tx和Rx的时钟信号。他们都是由PHY驱动的。

TxD[0...3]/RxD[0...3]:分别是Tx和Rx的数据传输线。TxD是控制器驱动,RxD是PHY驱动。

Tx_EN/RX_DV:分别是Tx和Rx的开关。这两根线都是PHY驱动。(事实上,虽然很多文档都讲Tx_EN是PHY驱动的;但在实现时,Tx_EN是由控制器来设定的,也就是控制器驱动的)。只有在Tx_EN有效时,TxD才会被PHY接收;只有在Rx_DV有效时,RxD才会被控制器接收。

Tx_ER/Rx_ER:分别是Tx和Rx的报错线。这两根线都是PHY驱动。即使是在Tx_EN或Rx_DV期间,只要此两根线有效,则出错的那个周期所传数据无效。10Mb以太网传输时,ER信号不影响正常传输,若不使用ER线,需将其接地。

CRS/COL:监听介质是否空闲/监听是否有冲突发生。这两根线都是由PHY驱动,并且只在半双工模式下有效。

按理来说有这些接口就可以完成通信了,但是MII本身也是一个复杂的逻辑电路,他也需要控制信息的写入和读出,在IEEE中,MII还有两个接口来专门控制MII。他们是MII接口的Management Interface:MDC和MDIO。通过它,控制芯片可以访问PHY的寄存器,并通过这些寄存器来对物理层芯片进行控制和管理。

MDC:管理接口的时钟。它是由控制器驱动,与TX_CLK和RX_CLK无任何关系。简单的说这个时钟就是个开关,你把数据准备好了,就上拉一下开关,然后再下来一下,

产生一个波形来驱动MII内部的逻辑来接受你在MDIO端口上设置的数据,同理,读取MII时也是一样。

MDIO:用来传送MAC层的控制信息和物理层的状态信息。它是一根双向的数据线。因MDIO在某个时钟周期内会空闲,呈高阻状态,故使用时须将其上拉。在CPU芯片里

我使用的是RX62N开发板,瑞萨造,加强了网络能力,比较适合通信类的开发。板子上集成了LAN8700i网卡芯片,非常小,肉眼不容易看清楚啊。本次学习的所有资料都是日语和英语,截图也都是日语文书中的原图。

第一部分:梳理概念。

大学学习了TCP/IP协议的大体框架,觉得物理层,链路层等都是很遥远的,或者说根本不需要自己去思考,拿着用就行了,但是现在就必须深入的去了解,悲剧啊。在RX62N的开发板上,LAN8700i承担了物理层的部分,代号PHY-LSI,也就是物理层芯片的意思,它负责网络通信的物理层。在RX62N的主芯片上有一个ETHERC的模块,负责链路层,也就是MAC地址层。它负责将链路方面的协议包生成和转发。

不在同一块芯片上,自然使用起来就不那么简单。为了解决这个问题,物理层的芯片和链路层的芯片都支持MII通信标准,。MII是一种IEEE的电气协议,引脚的定义和物理特性都有规定。这样来说,我们就应该在RX62N上编写程序,使用MII接口的特性来读取,发送数据包了,但如果是这样的话,代码似乎就会比较复杂,而且CPU需要不断的查询端口导致实时性能不会太好。RX62N给我们提供了一个EDMAC模块,使用DMA方式来存取网络数据,使得我们不需要直接访问MII来获取,发送数据,相当简便。网络通信口,PHY-LSI,MII,ETHERC,EDMAC的关系如1-1所示。

图1-1 通信设备的关系

第二部分:MII究竟是个啥

关于这部分,都是网络上抄来,整理一下就成的。MII,media independent interface,媒体独立接口。它的一头是MAC链路层芯片,另一头是物理层芯片。也就是一头是是数据源或者说是控制器,另一头是与介质相关的Tranceiver。

MII一共有16根线:

Tx_CLK/Rx_CLK:分别是Tx和Rx的时钟信号。他们都是由PHY驱动的。

TxD[0...3]/RxD[0...3]:分别是Tx和Rx的数据传输线。TxD是控制器驱动,RxD是PHY驱动。

Tx_EN/RX_DV:分别是Tx和Rx的开关。这两根线都是PHY驱动。(事实上,虽然很多文档都讲Tx_EN是PHY驱动的;但在实现时,Tx_EN是由控制器来设定的,也就是控制器驱动的)。只有在Tx_EN有效时,TxD才会被PHY接收;只有在Rx_DV有效时,RxD才会被控制器接收。

Tx_ER/Rx_ER:分别是Tx和Rx的报错线。这两根线都是PHY驱动。即使是在Tx_EN或Rx_DV期间,只要此两根线有效,则出错的那个周期所传数据无效。10Mb以太网传输时,ER信号不影响正常传输,若不使用ER线,需将其接地。

CRS/COL:监听介质是否空闲/监听是否有冲突发生。这两根线都是由PHY驱动,并且只在半双工模式下有效。

按理来说有这些接口就可以完成通信了,但是MII本身也是一个复杂的逻辑电路,他也需要控制信息的写入和读出,在IEEE中,MII还有两个接口来专门控制MII。他们是MII接口的Management Interface:MDC和MDIO。通过它,控制芯片可以访问PHY的寄存器,并通过这些寄存器来对物理层芯片进行控制和管理。

MDC:管理接口的时钟。它是由控制器驱动,与TX_CLK和RX_CLK无任何关系。简单的说这个时钟就是个开关,你把数据准备好了,就上拉一下开关,然后再下来一下,

产生一个波形来驱动MII内部的逻辑来接受你在MDIO端口上设置的数据,同理,读取MII时也是一样。

MDIO:用来传送MAC层的控制信息和物理层的状态信息。它是一根双向的数据线。因MDIO在某个时钟周期内会空闲,呈高阻状态,故使用时须将其上拉。在CPU芯片里

我们通常看到读取或写入MDIO后释放总线,这就是上拉。

图1-2 MII和CPU的连接关系

MII有很多简化版本和Extent版本,如GMII,RGMII,RMII,SMII,SSMII,TBI,RTBI等。