ARM Cortex系列(A8/A9/A15/A7) NEON多媒体处理SIMD引擎优化

出处: http://houh-1984.blog.163.com/blog/static/31127834201211275111378/

Cortex-A9的NEON多媒体处理器是基于ARMv7的SIMD(Single Instruction Multiple Data)和向量浮点VFPv3(Vector Floating-Point)指令集的,在具体的芯片设计中NEON组件是可选的,NEON处理器是面向音频、视频编解码器、图像处理和语音信号处理以及其他的基带等信息处理领域的。 本文介绍了NEON处理器的基本架构、NEON处理器的并发情况下Cortex-A8和Cortex-A9的区别、NEON的寄存器组和数据类型、NEON编程的针对编译器、汇编器的优化方法以及其他的提高性能的并行方法。

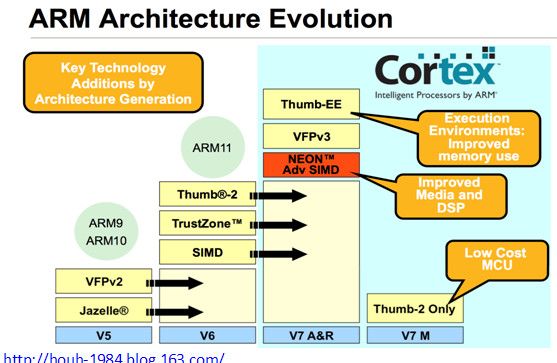

图1. ARM体系结构的演进

Cortex-A9 处理器简介

图2. Coretex-A9处理器的架构框图(View Larger Cortex-A9 处理器 Image)

Cortex-A9 是性能最高的 ARM 处理器,可实现受到广泛支持的 ARMv7 体系结构的丰富功能。Cortex-A9 处理器的设计旨在打造最先进的、高效率的、长度动态可变的、多指令执行超标量体系结构,提供采用乱序猜测方式执行的 8 阶段管道处理器,凭借范围广泛的消费类、网络、企业和移动应用中的前沿产品所需的功能,它可以提供史无前例的高性能和高能效。ARM Cortex?-A9 处理器提供了史无前例的高性能和高能效,从而使其成为需要在低功耗或散热受限的成本敏感型设备中提供高性能的设计的理想解决方案。它既可用作单核处理器,也可用作可配置的多核处理器,同时可提供可合成或硬宏实现。该处理器适用于各种应用领域,从而能够对多个市场进行稳定的软件投资。

Cortex-A9 微体系结构既可用于可伸缩的多核处理器(Cortex-A9 MPCore? 多核处理器),也可用于更传统的处理器(Cortex-A9 单核处理器)。可伸缩的多核处理器和单核处理器支持 16、32 或 64KB 4 路关联的 L1 高速缓存配置,对于可选的 L2 高速缓存控制器,最多支持 8MB 的 L2 高速缓存配置,它们具有极高的灵活性,均适用于特定应用领域和市场。

下载 Cortex-A9 白皮书

窗体顶端

与高性能计算平台消耗的功率相比,ARM Cortex-A9 处理器可提供功率更低的卓越功能,其中包括:

-

无与伦比的性能,2GHz 标准操作可提供 TSMC 40G 硬宏实现

-

以低功耗为目标的单核实现,面向成本敏感型设备

-

利用高级 MPCore 技术,最多可扩展为 4 个一致的内核

-

可选 NEON? 媒体和/或浮点处理引擎

通过共享以下常见需求,Cortex-A9 处理器可提供满足各种不同市场应用需求的可扩展解决方案,包括移动手机以及高性能的消费类产品和企业产品:

-

通过提高性能、降低功耗来提高能效;

-

提高最高性能,满足要求更高的应用需求;

-

能够在多个设备之间共享软件和工具投资;

Cortex-A9 MPCore 多核处理器集成了经验证非常成功的 ARM MPCore 技术以及更多增强功能,以此简化了多核解决方案,并使其应用范围得到扩展。Cortex-A9 MPCore 处理器可提供史无前例的可扩展的最高性能,同时还支持灵活设计和新功能,从而进一步降低和控制处理器和系统级的能耗。借助 Cortex-A9 MPCore 处理器的定向实现,移动设备的最高性能还可在现在的解决方案的基础上不断提高,具体方法是:利用设计灵活性和 ARM MPCore 技术提供的高级功率管理技术,在散热受限以及移动电源预算紧张的情况下维持运行。使用可伸缩的最高性能,该处理器可超过现今类似的高性能嵌入式设备的性能,并可在拓宽市场的基础上进行稳定的软件投资。

Cortex-A9多核处理器是首款结合了Cortex应用级架构以及用于可扩展性能的多处理能力的ARM处理器,提供了下列增强的多核技术:

*加速器一致性端口(ACP),用于提高系统性能和降低系统能耗

*先进总线接口单元(Advanced Bus Interface Unit),用于在高带宽设备中实现低延迟时间

*多核TrustZone® 技术,结合中断虚拟,允许基于硬件的安全和加强的类虚拟(paravirtualization)解决方案

*通用中断控制器(GIC),用于软件移植和优化的多核通信

Cortex-A9 NEON 媒体处理引擎 (MPE)

Cortex-A9 MPE 可用于任一 Cortex-A9 处理器,并可提供一个具有 Cortex-A9 浮点单元的性能和功能以及 NEON 高级 SIMD 指令集实现的引擎,以便进一步提高媒体和信号处理功能的速度。MPE 可扩展 Cortex-A9 处理器的浮点单元 (FPU),提供一个 quad-MAC 以及附加的 64 位和 128 位寄存器集,在每个周期 8 位、16 位和 32 位整型以及 32 位浮点数据量的基础上支持一组丰富的 SIMD 操作。

Cortex-A9 浮点单元 (FPU)

在与任一 Cortex-A9 处理器一起实现时,FPU 可提供与 ARM VFPv3 体系结构兼容的高性能的单双精度浮点指令,该体系结构是与上一代 ARM 浮点协处理器兼容的软件。

物理IP:提供在Cortex-A9处理器上实现低功耗、高性能应用所需的众多标准单元库和存储器。标准单元包括功耗管理工具包,可实现动态和漏泄功耗节省技术,例如时钟门控、多电压岛和功率门控。还提供具有先进的功耗节省功能的存储编译器。

· Fabric IP:Cortex-A9处理器得到广泛的PrimeCell® fabric IP元件的支持。这些元件包括:一个动态存储控制器、一个静态存储控制器、一个AMBA® 3 AXI可配置的内部互连及一个优化的L2 Cache 控制器,用于匹配Cortex-A9处理器在高频设计中的性能和吞吐能力。

· 图形加速: ARM Mali? 图形处理单元及Cortex-A9处理器的组合,将使得SoC合作活动能够创造高度整合的系统级解决方案,带来最佳的尺寸、性能和系统带宽优势。

· 系统设计:ARM RealView® SoC Designer工具提供快速的架构优化和性能分析,并允许在硬件完成以前很长时间即可进行软件驱动程序和对时间要求很严格的代码的早期开发。RealView系统发生器(RealView System Generator)工具为基于Cortex-A9处理器的虚拟平台的采用提供超快建模能力。Realview工具中关于Cortex-A9处理器的基于周期的(cycle based)及程序员视角的模型将于2008年第二季度上市。

· 调试: ARM CoreSight?片上技术加速了复杂调试的时间,缩短了上市时间。程序追踪宏单元技术(Program Trace Macrocell technology)具有程序流追踪能力,能够将处理器的指令流完全可视化,同时配置与ARMv7架构兼容的调试接口,实现工具标准化和更高的调试性能。用于Cortex-A9处理器的CoreSight设计工具包扩展了其调试和追踪能力,以涵盖整个片上系统,包括多个ARM处理器、DSP以及智能外设。

· 软件开发:ARM RealView开发套件(ARM RealView Development Suite)包括先进的代码生成工具,为Cortex-A9处理器提供卓越的性能和无以比拟的代码密度。这套工具还支持矢量编译,用于NEON媒体和信号处理扩展集,使得开发者无需使用独立的DSP,从而降低产品和项目成本。包括先进的交叉触发在内的Cortex-A9 MPCore多核处理器调试得到RealView ICE和Trace产品的支持,同时也得到一系列硬件开发板的支持,用于FPGA系统原型设计和软件开发。

作为许多下一代设备的核心,Cortex-A9 处理器通常与许多其他 IP 块集成。

系统 IP

系统 IP 组件对于在芯片上构建复杂的系统至关重要,通过利用系统 IP 组件,开发人员可以显著缩短开发和验证周期,从而节约成本并缩短产品的上市时间。

工具支持

所有 ARM 处理器均受 ARM RealView? 系列开发工具以及各种第三方工具、操作系统和 EDA 供应商的支持。ARM RealView 工具独一无二,所提供的解决方案涉及从概念到最终产品部署的整个开发过程。

图3. 基于Coretex-A9核的主要芯片

NEON 多媒体SIMD引擎简介

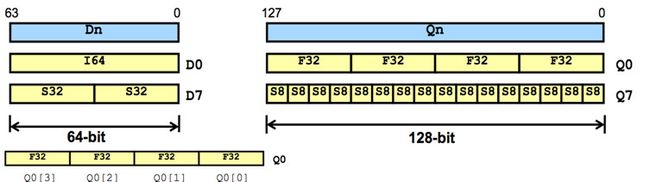

NEON是一个SIMD数据处理架构,256字节的寄存器堆包含32个64-bit位宽的寄存器或者16个128-bit位宽的寄存器。所有的寄存器都被视为具有相同数据类型的一个向量,支持的数据类型包括有符号或者无符号的8-bit、16-bit、32-bit和64-bit的整型数据或者单精度浮点数据。NEON指令都是针对相同数据类型的通道处理的,即所有通道执行相同的指令操作。如下图4所示。

图4. ARM NEON处理器的SIMD操作

NEON的寄存器组:NEON和VFPv3 浮点协处理器共享寄存器组,这些寄存器和ARM核的寄存器截然不同,NEON还会采用ARM的寄存器作为地址寄存器间接寻址。图5是NEON寄存器的视图,16个128-bit的4字节寄存器Q0~Q15,或者32个64bit的双字寄存器D0~D31,VFPv3的寄存器堆还有32个32-bit的寄存器S0~S31.

图5. NEON和VFPv3协处理器的寄存器堆视图

NEON指令支持的操作数类型包括:有符号或者无符号的8-bit、16-bit、32-bit和64-bit的整型数据(I8、S8、U8、I16、S16、U16、I32、S32、U32、I64、S64、U64)或者单精度浮点数据(F32)。

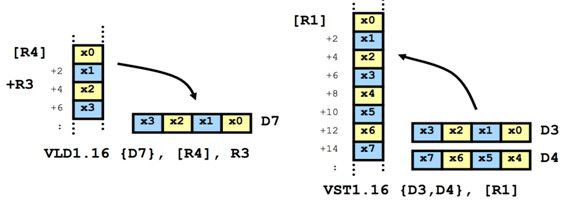

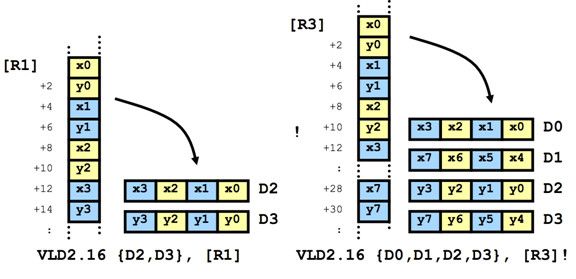

图6. 单个寄存器组的元素分配

NEON支持的一些数据访问:支持非对齐访问但对齐的访问速度更快,可以通过访问@bits来指定地址对齐的位数,如@32、@64、@128等。加载和存储支持打包的数据类型,即可以有2、3、4个通道的interleave的数据加载和存储,还能在标量和向量间进行数据的移动,但是速度比较慢、还能支持单精度浮点的数据运算。

NEON 指令集

图7. NEON的线性加载和存储指令

图8. 交织的数据加载和存储指令

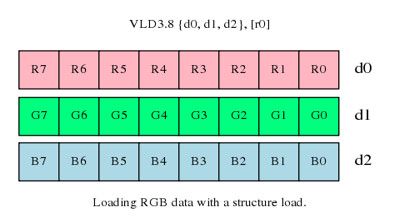

图9. 使用结构化的加载指令加载RGB数据

vld1.32 {d16-d19}, [r1]!

vmul.f32 q12, q8, d0[0]

vmla.f32 q12, q9, d0[1]

vst1.32 {d24-d27}, [r0]!

NEON的并行优化方法

ARM编译器优化方法

NEON并行化和向量化的编译选项:ARM RVDS 3.0以上版本或者DS-5使用编译选项armcc --vectorize或者Codesourcery 2007q3之后的gcc版本使用如下编译选项使能vfp:-mcpu=cortex-a8 -mtune=cortex-a8 -O3 -mfloat-abi=softfp -mfpu=vfp 或者使用-mcpu=cortex-a8 -mtune=cortex-a8 -O3 -mfloat-abi=softfp -mfpu=neon -ftree-vectorize来使能NEON的并行处理。一般认为RVDS或者DS-5编译器的armcc针对并行处理性能很差,即使调整算法的结构以适合编译器进行NEON指令的优化,但是生成的代码还是难以让人满意。而GCC的自动并行化处理的结果性能更差,针对Android开发,只能采用Google提供的NDK的GCC工具链可以用来开发。但ARM EABI提供了编译器支持的C内联intrinsics。可以参考ARM V7-A的 ABI手册以及arm_neon.h文件。

ARM汇编器的优化方法

使用NEON的intrinsic指令进行优化需要对NEON的指令集非常熟悉,而且使用intrinsics没法控制寄存器分配和内存对齐等,因而很多的NEON的优化还是基于汇编代码。当然手工写汇编代码总是需要很多的额外开销的,而且还要了解ARM EABI编程规范。

NEON编程优化的基本方法

一般NEON优化是针对需要大量数据处理的函数,而函数的基本操作都是先加载数据,然后进行数据处理,最后把计算的结果保存到内存。首先针对NEON数据的加载和存储,可以参考http://houh-1984.blog.163.com/blog/static/3112783420111159169507/,即适当考虑结构化的加载/存储以有效的进行数据加载成为有利于并行处理的方式,当然除了数据加载有利于并行处理,还要考虑数据加载有利于cache性能的优化。然后采用NEON指令进行计算,针对数据访问,可以考虑使用Q0~Q3的参数寄存器以及Q8~Q15寄存器,而对于Q4~Q7寄存器则必须根据EABI的规范在函数调用内保存。

另外就是关需数据的加载类型,一个是数据的对齐,虽然NEON完全支持非对齐访问,但是对齐数据一个是有利于加载、存储,另外一个是也更cache友好,非对齐的数据访问要消耗更多的时钟周期尤其是在非对齐还要跨越cache行的情况下,数据对齐方式可以采用[<Rn>,:<align>],其中align可以为32、64、128、256位。软件流水是非常重要的优化工具,因为现在的ARM基于RISC的处理器,流水线是必须的,因而针对流水线需要更好的优化方法,虽然NEON的流水线在Coretex-A8和Cortex-A9的处理器上不同,NEON的指令一般都是在一个周期内发出,但是执行结果可能若干个周期才能有效,只有简单的如VSUB、VADD和VMOV指令才能在下一个周期可以用。并发的指令发出也是需要提到的。另外从NEON的寄存器把数据保存到ARM寄存器非常耗时,需要至少20个周期的延时,因而尽量避免这类操作,NEON没有提供除法和求平方根的操作,而VFPv3则存在这些指令。但是由于NEON处理器和VFP单元共用硬件,因而不要混合使用NEON和VFP指令。最后是尽量避免ARM和NEON处理器访问相同的数据区域。

Vld1.8 {D0}, [R1:64]

Vld1.8 {D0,D1}, [R1:128]!

Vld1.8 {D0,D1,D2,D3}, [R2:256]!,R3

Cortex-A8和Cortex-A9的多指令并发有所不同,A8是每次并发两次fetch,而A9除了多次并发外,还能乱序执行,因而指令重排的优化非常重要。一般而言NEON的SIMD优化能提高至少2倍的系统性能,取决于实际处理的位宽。

http://houh-1984.blog.163.com/

http://baike.baidu.com/view/2937500.htm

http://www.arm.com/zh/products/processors/cortex-a/cortex-a9.php

Cortex-A9的NEON多媒体处理器是基于ARMv7的SIMD(Single Instruction Multiple Data)和向量浮点VFPv3(Vector Floating-Point)指令集的,在具体的芯片设计中NEON组件是可选的,NEON处理器是面向音频、视频编解码器、图像处理和语音信号处理以及其他的基带等信息处理领域的。 本文介绍了NEON处理器的基本架构、NEON处理器的并发情况下Cortex-A8和Cortex-A9的区别、NEON的寄存器组和数据类型、NEON编程的针对编译器、汇编器的优化方法以及其他的提高性能的并行方法。