ddr sdram self-refresh & auto-refresh

以下是EDD5116AFTA数据手册的摘录。不过看过了还是不太明白二者的区别。

self-refresh:

Self-refresh entry [SELF]

This command starts self-refresh. The self-refresh operation continues as long as CKE is held low. 只要CKE为低就开始自刷新/

During the selfrefresh operation, all ROW addresses are repeated refreshing by the internal refresh controller. 由内部的刷新控制器给出行地址重复刷新

A self-refresh is terminated by a self-refresh exit command.

Self-Refresh

The self-refresh command can be used to retain data in the DDR SDRAM, even if the rest of the system is powered down. 用来保存数据,即使系统的其他部分已经待机。

When in the self-refresh mode, the DDR SDRAM retains data without external clocking.

保存数据,可以不需要外部的时钟。

The self-refresh command is initiated like an auto-refresh command except CKE is disabled (low). 开始方式和自动刷新很像,只是CKE是低。

The DLL is automatically disabled upon entering self-refresh, and is automatically enabled upon exiting self-refresh. 进入自刷新后,DLL自动无效, 退出后又有效。

Any time the DLL is enabled a DLL reset must follow and 200 clock cycles should occur before a read command can be issued. DLL有效后,至少要等200时钟才能有其他命令。

Input signals except CKE are “Don’t care” during self-refresh. Since CKE is an SSTL2 input, VREF must be maintained during self-refresh.除CKE外,其他信号都不关心

auto-refresh:

Auto-refresh command [REF]

This command executes auto-refresh. The banks and the ROW addresses to be refreshed are internally determined by the internal refresh controller。

要刷新的行地址和bank都由内部刷新控制器决定。

The average refresh cycle is 7.8 μs. The output buffer becomes high-Z after autorefresh start. Precharge has been completed automatically after the auto-refresh.

进入自动刷新后,输出端高阻,结束后自动执行一次precharge/预充电。

The ACT or MRS command can be issued tRFC after the last auto-refresh command

感觉二者的唯一区别就是 自刷新时CKE为低,自动刷新时CKE为高。

还有就是自动刷新可以不需要外部时钟?这可能么?还是我理解错了?

还有按理说自动刷新应该全自动,自刷新至少要有一部分是由host控制的,即要从host得到部分信息,像要刷新的bank ,起始ROW等。不过手册没说,我在查查。

更新:

首先赞叹以下google的搜索能力。我只是打了“自动刷新 自刷新”。结果把人家清华的一本书收出来了。上面有一段。还选中了。由于版权保护,只能看不能复制,么办法,截图了。对不起了。

看来人家自刷新就是不要时钟,不过我就是不明白,同步电路没有时钟怎么让计数器加1。怎么实现刷新?

不过看来这个刷新并不是个简单的事情,还需要再接着看了。

自动刷新实现较为简单,而自刷新功耗更小。

更新:一个网站上关于刷新的文章:讲的差不多明白了。

这是个系列文章,对sdram进行了系统的介绍,不错不错。哈哈

http://soft.zdnet.com.cn/stor-age/2004/0218/399654.shtml

高手进阶,终极内存技术指南——完整/进阶版

ZDNet 频道 更新时间:2004-02-18 作者:存储时代 赵效民 来源:

本文关键词:

第1页:序:不得不说的话第2页:SDRAM内存模组的物理Bank与芯片位宽第3页:SDRAM的逻辑Bank与芯片容量表示方法第4页:SDRAM的引脚与封装第5页:SDRAM芯片初始化、行有效、列读写时序第6页:SDRAM的读/写时序与突发长度第7页:SDRAM芯片的预充电与刷新操作第8页:图解SDRAM工作流程:仓库物语第9页:SDRAM的结构、时序与性能的关系(上)第10页:SDRAM的结构、时序与性能的关系(下)第11页:如日中天——DDR SDRAM(上)第12页:如日中天——DDR SDRAM(下)第13页:昔日贵族——Rambus DRAM(一)第14页:昔日贵族——Rambus DRAM(二)第15页:昔日贵族——Rambus DRAM(三)第16页:昔日贵族——Rambus DRAM(四)第17页:明日之星——DDR-Ⅱ与DDR-Ⅲ(一)第18页:明日之星——DDR-Ⅱ与DDR-Ⅲ(二)第19页:明日之星——DDR-Ⅱ与DDR-Ⅲ(三)第20页:没有我不行——内存模组(上)第21页:没有我不行——内存模组(下)

SDRAM芯片的预充电与刷新操作

预充电

由于SDRAM的寻址具体独占性,所以在进行完读写操作后,如果要对同一L-Bank的另一行进行寻址,就要将原来有效(工作)的行关闭,重新发送行/列地址。L-Bank关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。预充电可以通过命令控制,也可以通过辅助设定让芯片在每次读写操作之后自动进行预充电。实际上,预充电是一种对工作行中所有存储体进行数据重写,并对行地址进行复位,同时释放S-AMP(重新加入比较电压,一般是电容电压的1/2,以帮助判断读取数据的逻辑电平,因为S-AMP是通过一个参考电压与存储体位线电压的比较来判断逻辑值的),以准备新行的工作。具体而言,就是将S-AMP中的数据回写,即使是没有工作过的存储体也会因行选通而使存储电容受到干扰,所以也需要S-AMP进行读后重写。此时,电容的电量(或者说其产生的电压)将是判断逻辑状态的依据(读取时也需要),为此要设定一个临界值,一般为电容电量的1/2,超过它的为逻辑1,进行重写,否则为逻辑0,不进行重写(等于放电)。为此,现在基本都将电容的另一端接入一个指定的电压(即1/2电容电压),而不是接地,以帮助重写时的比较与判断。

现在我们再回过头看看读写操作时的命令时序图,从中可以发现地址线A10控制着是否进行在读写之后当前L-Bank自动进行预充电,这就是上文所说的“辅助设定”。而在单独的预充电命令中,A10则控制着是对指定的L-Bank还是所有的L-Bank(当有多个L-Bank处于有效/活动状态时)进行预充电,前者需要提供L-Bank的地址,后者只需将A10信号置于高电平。

在发出预充电命令之后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行,这个间隔被称为tRP(Precharge command Period,预充电有效周期)。和tRCD、CL一样,tRP的单位也是时钟周期数,具体值视时钟频率而定。

读取时预充电时序图(上图可点击放大):图中设定:CL=2、BL=4、tRP=2。自动预充电时的开始时间与此图一样,只是没有了单独的预充电命令,并在发出读取命令时,A10地址线要设为高电平(允许自动预充电)。可见控制好预充电启动时间很重要,它可以在读取操作结束后立刻进入新行的寻址,保证运行效率。

| 误区:读写情况下都要考虑写回延迟 |

| 有些文章强调由于写回操作而使读/写操作后都有一定的延迟,但从本文的介绍中写可以看出,即使是读后立即重写的设计,由于是与数据输出同步进行,并不存在延迟。只有在写操作后进行其他的操作时,才会有这方面的影响。写操作虽然是0延迟进行,但每笔数据的真正写入则需要一个足够的周期来保证,这段时间就是写回周期(tWR)。所以预充电不能与写操作同时进行,必须要在tWR之后才能发出预充电命令,以确保数据的可靠写入,否则重写的数据可能是错的,这就造成了写回延迟。

数据写入时预充电操作时序图(可点击放大):注意其中的tWR参数,由于它的存在,使预充电操作延后,从而造成写回延迟 |

刷新

之所以称为DRAM,就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是DRAM最重要的操作。

刷新操作与预充电中重写的操作一样,都是用S-AMP先读再写。但为什么有预充电操作还要进行刷新呢?因为预充电是对一个或所有L-Bank中的工作行操作,并且是不定期的,而刷新则是有固定的周期,依次对所有行进行操作,以保留那些久久没经历重写的存储体中的数据。但与所有L-Bank预充电不同的是,这里的行是指所有L-Bank中地址相同的行,而预充电中各L-Bank中的工作行地址并不是一定是相同的。

那么要隔多长时间重复一次刷新呢?目前公认的标准是,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000秒),也就是说每一行刷新的循环周期是64ms。这样刷新速度就是:行数量/64ms。我们在看内存规格时,经常会看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的标识,这里的4096与8192就代表这个芯片中每个L-Bank的行数。刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096行时为15.625μs(微秒,1/1000毫秒),8192行时就为7.8125μs。

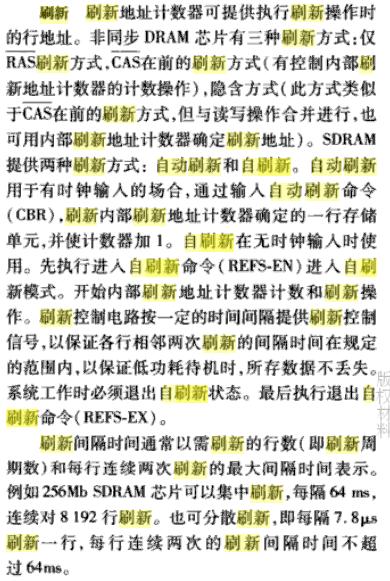

刷新操作分为两种:自动刷新(Auto Refresh,简称AR)与自刷新(Self Refresh,简称SR)。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。对于AR, SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者说CAS在RAS之前有效。所以,AR又称CBR(CAS Before RAS,列提前于行定位)式刷新。由于刷新涉及到所有L-Bank,因此在刷新过程中,所有L-Bank都停止工作,而每次刷新所占用的时间为9个时钟周期(PC133标准),之后就可进入正常的工作状态,也就是说在这9 个时钟期间内,所有工作指令只能等待而无法执行。64ms之后则再次对同一行进行刷新,如此周而复始进行循环刷新。显然,刷新操作肯定会对SDRAM的性能造成影响,但这是没办法的事情,也是DRAM相对于SRAM(静态内存,无需刷新仍能保留数据)取得成本优势的同时所付出的代价。

SR则主要用于休眠模式低功耗状态下的数据保存,这方面最著名的应用就是STR(Suspend to RAM,休眠挂起于内存)。在发出AR命令时,将CKE置于无效状态,就进入了SR模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并进入正常操作状态。

数据掩码

在讲述读/写操作时,我们谈到了突发长度。如果BL=4,那么也就是说一次就传送4×64bit的数据。但是,如果其中的第二笔数据是不需要的,怎么办?还都传输吗?为了屏蔽不需要的数据,人们采用了数据掩码(Data I/O Mask,简称DQM)技术。通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。DQM由北桥控制,为了精确屏蔽一个P-Bank位宽中的每个字节,每个DIMM有8个DQM信号线,每个信号针对一个字节。这样,对于4bit位宽芯片,两个芯片共用一个DQM信号线,对于8bit位宽芯片,一个芯片占用一个DQM信号,而对于16bit位宽芯片,则需要两个DQM引脚。

SDRAM官方规定,在读取时DQM发出两个时钟周期后生效,而在写入时,DQM与写入命令一样是立即成效。

读取时数据掩码操作,DQM在两个周期后生效,突发周期的第二笔数据被取消(上图可点击放大)

写入时数据掩码操作,DQM立即生效,突发周期的第二笔数据被取消(上图可点击放大)

有关内存内部的基本操作就到此结束,其实还有很多内存的操作没有描述,但都不是很重要了,限于篇幅与必要性,我们不在此介绍,有兴趣的读者可以自行查看相关资料。