中断处理学习笔记

中断处理

如果想使用中断:

1 初始化

A设置源头

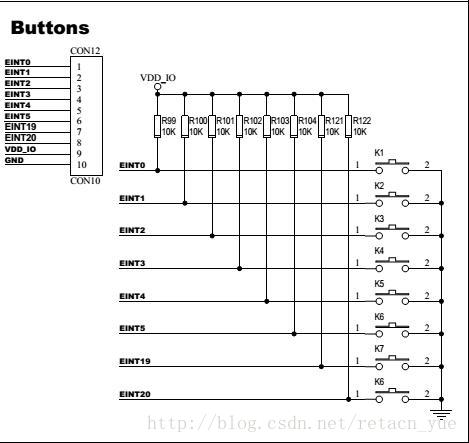

查看原理图

XEINT0/kpROW0/GPN0

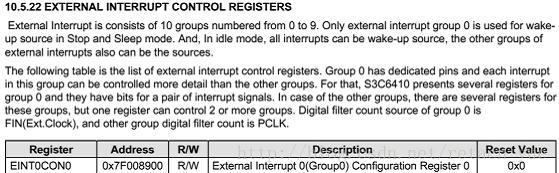

查看芯片手册

![]()

使能

![]()

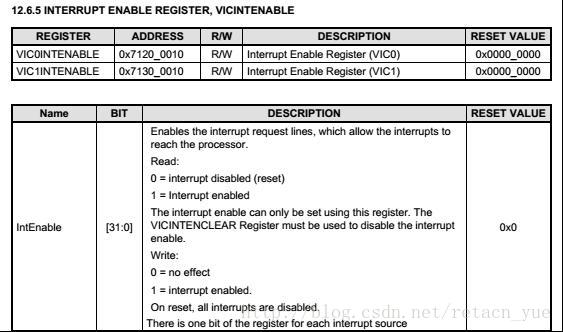

B 设置中断控制器

This chapter describes the functions and usage ofVectored Interrupt Controller in S3C6410X RISC

microprocessor.

12.1 OVERVIEW

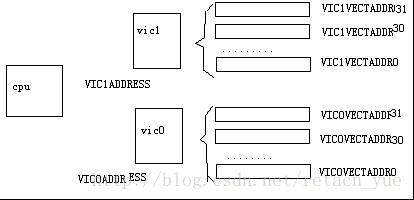

The interrupt controller in the S3C6410X is composed of2 VIC’s (Vectored Interrupt Controller, ARM PrimeCell

PL192) and 2 TZIC’s (TrustZone Interrupt Controller, SP890).

Two TZIC’s and VIC’s are daisy-chained to support up to 64 interrupt sources.

12.2 FEATURES

The Vectored Interrupt Controller features in S3C6410 incudes the following:

• Support for 32 vectored IRQ interrupts per VIC

• Fixed hardware interrupt priority levels

• Programmable interrupt priority levels

• Hardware interrupt priority level masking

• Programmable interrupt priority level masking

• IRQ and FIQ generation

• Software interrupt generation

• Raw interrupt status

• Interrupt request status

• Privileged mode support for restricted access

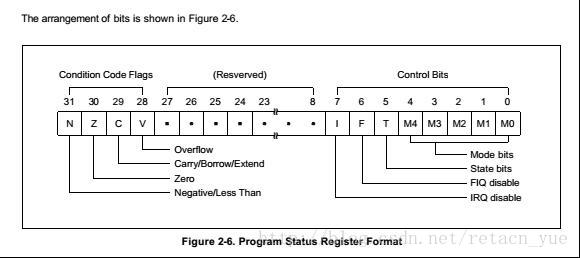

C 打开cpsr 中的I状态位(清零)

如果发生中断:

1 cpu进入irp模式

2 cpsr保存到spsr_irq

3 使用r13_irq,r14_irq

4 把下一条指令地址存放到r14中去

5 跳到0x18执行

保存中断

处理中断

恢复中断

中断向量寄存器