基于模型设计的FPGA开发与实现:滤波器设计与实现(四)Matlab中滤波器HDL代码生成优化

MBD-FPGA 开发与实现

http://blog.sina.com.cn/McCrocodile

先来看看前面章节设计的滤波器对于实际应用是个多糟糕的设计!!!

上面一节中我们使用分离两个信号的滤波器高达60阶,如果我们要放大EP3C25中,基本上是不可接受的,如果我们还有其他逻辑。EP3C25只有132个9bit的嵌入式乘法器。

屏幕剪辑的捕获时间: 2011/9/10 21:33

下面看下上一节生成代码的编译报告。可以从看出资源占用情况和可以工作的最大频率fMax=3.28MHz,在很多应用中这个可以认为是一个失败的设计。原因和滤波器的阶数、滤波器的结构等多个方面的有关系,如何针对FPGA优化设计,提高吞吐量等问题时本节主要讨论的内容。

屏幕剪辑的捕获时间: 2011/9/11 8:41

屏幕剪辑的捕获时间: 2011/9/11 8:41

Fmax最大时钟速率很多情况下是最重要的问题。

1、滤波器的结构:info(Hf2)

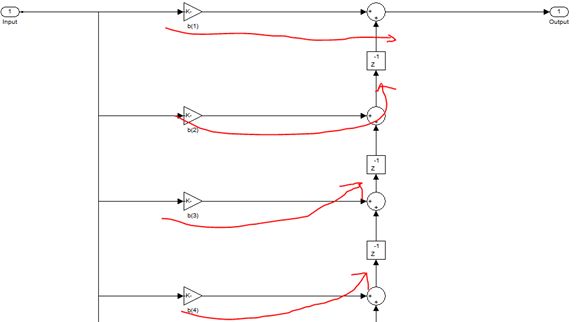

上图所示为滤波器时直接型的FIR,下图为直接型FIR的结构,连串的加法器是最坏路径,也是Fmax比较小的罪魁祸首。

这个问题需要在设计滤波器的时候选择合适的滤波器结构。下面看看直接传输型FIR滤波器的结构。可以看出最坏路径是一个常数乘法器和一个加法器。这时候引入新的问题:输入的信号有太多的扇出,着同样可能会造成FMax比较小,不过这个问题很好解决,在滤波器的输入端口采用2~4级寄存器,并在HDL综合器中选择自动复制寄存器,就可以解决问题。这儿不做深入讨论主要是说明解决问题的途径,后面滤波器结构将分别对FIR和IIR滤波器做专门讨论。实现的过程在这节结尾有两个例子,以供学习。

上面的结果可以看得出,滤波器的结构所带来的性能差异。FIR滤波器结构的问题后面会在单速滤波器的FIR结构中详细介绍了。下面是以直接传输型的FIR为例说明的,下面是源程序。

%提升滤波器性能之转换为直接传输型

%Author by McCrocodile@20110911

clear all; close all;

load TD2.mat

%% 查看滤波器的结构

info(hd)

%% 转换滤波器结构并定点化

Hf3=convert(hd,'df1t')%转换滤波器结构,也可以在FDATool中手动转换

Hf3.Arithmetic='fixed';%滤波器做定点化处理

set(Hf3, 'CoeffWordLength', 9);%设置滤波器系数的字长

% 根据FPGA特性详细设置

set (Hf3, 'InputWordLength', 10);%输入ADC位宽

set (Hf3, 'ProductMode', 'SpecifyPrecision');%设置滤波器内部乘法模式

set (Hf3, 'ProductWordLength', 18);%如Altera的CIII片子的乘法器为9的倍数,这儿选18bit

set (Hf3, 'AccumMode', 'SpecifyPrecision');%累加器的字长,通常累加器比乘法器多4比特作为保护位宽

set (Hf3, 'AccumWordLength', 28);%输出数据总线

set(Hf3,'OverflowMode','saturate');%修改溢出模式,会增加面积

%自动调整

tx = 2*sign(fliplr(impz(Hf3)));%激励

Hf3 = autoscale(Hf3, tx);%自动调整动态方位

fvtool(Hf3)%,比较不同字长设置

%% 测试

% 最坏情况测试

fipref('LoggingMode', 'on', 'DataTypeOverride', 'ForceOff');%创建fipref对象打开记录

y = filter(Hf3, tx);

fipref('LoggingMode', 'off');

R = qreport(Hf3)%查看报告,报告最近的顶点滤波计算报告

% 对信号分离的定点化测试

fipref('LoggingMode', 'on', 'DataTypeOverride', 'ForceOff');%创建fipref对象打开记录

y1 = filter(Hf3, x);

fipref('LoggingMode', 'off');

R1 = qreport(Hf3)%查看报告,报告最近的顶点滤波计算报告

figure;plot(y1);title('定点化滤波信号分离测试')

%% 生成Simulink模型

%直接传输型FIR滤波器不能直接生成代码,不过可以生成Simulink模型之后生成HDL代码

realizemdl(Hf3)

2、滤波器中乘法器和加法器引起的最坏路径

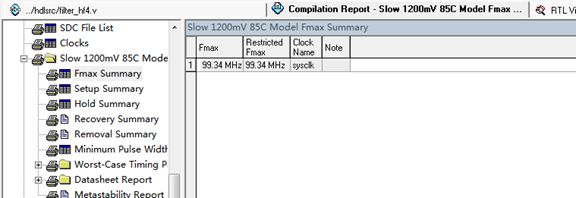

这里以一个例子说明对乘法或者加法寄存器设置加入寄存器,来增加时序收敛性。这里给出一个问题,是加法器设置寄存器在这儿起了作用?还是乘法器?还是两者共同其做了?

源程序:

%提升滤波器性能之转换为直接传输型

%Author by McCrocodile@20110911

clear all; close all;

load TD2.mat

%% 查看滤波器的结构

info(hd)

%% 转换滤波器结构并定点化

Hf4=convert(hd,'dfsymfir')%转换滤波器结构,也可以在FDATool中手动转换

Hf4.Arithmetic='fixed';%滤波器做定点化处理

set(Hf4, 'CoeffWordLength', 9);%设置滤波器系数的字长

% 根据FPGA特性详细设置

set (Hf4, 'InputWordLength', 10);%输入ADC位宽

set (Hf4, 'FilterInternals', 'SpecifyPrecision');%设置滤波器内部乘法模式

set (Hf4, 'ProductWordLength', 18);%如Altera的CIII片子的乘法器为9的倍数,这儿选18bit

set (Hf4, 'AccumWordLength', 22);%累加器的字长,通常累加器比乘法器多4比特作为保护位宽

set (Hf4, 'OutputWordLength', 16);%输出数据总线

set(Hf4,'OverflowMode','saturate');%修改溢出模式,会增加面积

%自动调整

tx = 2*sign(fliplr(impz(Hf4)));%激励

Hf4 = autoscale(Hf4, tx);%自动调整动态方位

fvtool(Hf4)%,比较不同字长设置

%% 测试

% 最坏情况测试

fipref('LoggingMode', 'on', 'DataTypeOverride', 'ForceOff');%创建fipref对象打开记录

y = filter(Hf4, tx);

fipref('LoggingMode', 'off');

R = qreport(Hf4)%查看报告,报告最近的顶点滤波计算报告

% 对信号分离的定点化测试

fipref('LoggingMode', 'on', 'DataTypeOverride', 'ForceOff');%创建fipref对象打开记录

y1 = filter(Hf4, x);

fipref('LoggingMode', 'off');

R1 = qreport(Hf4)%查看报告,报告最近的顶点滤波计算报告

figure;plot(y1);title('定点化滤波信号分离测试')

%% 生成HDL代码

fdhdltool(Hf4)

save TD5.mat

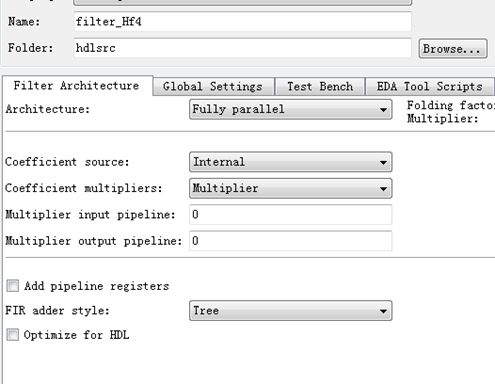

不设置乘法器和加法流水寄存器

generatehdl(Hf4, 'ResetType', 'Synchronous',...

'OptimizeForHDL', 'on',...

'Name', 'filter_Hf4',...

'ResetAssertedLevel', 'Active-low',...

'TargetLanguage', 'Verilog');

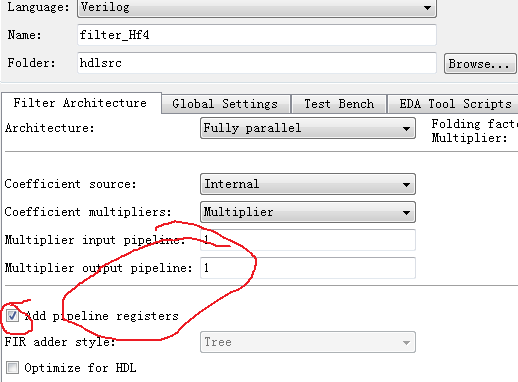

设置加法流水寄存器

generatehdl(Hf4, 'ResetType', 'Synchronous',...

'OptimizeForHDL', 'on',...

'Name', 'filter_Hf4',...

'ResetAssertedLevel', 'Active-low',...

'TargetLanguage', 'Verilog');

或者使用GUI设置

上面的例子可以看出生成的代码性能差异明显。诸如对称性的滤波器可以节约,但是并不是所有的滤波器都能够这样设置,这就需要根据滤波器的机构不同参考帮助予以设置。

3、滤波器面积与速度平衡

最后给出了一些生成滤波器的其他几个优化选项。这些选项需要对照帮助文档实践,再根据需要设置,一般都可以达到需要的性能。

屏幕剪辑的捕获时间: 2011/9/13 22:30

未完待续~~~~