硬件相关基础知识3(DDR3基本知识)

DDR3 基本知识

一、DDR3 简介

memory)是应用在计算机及电子产品领域的一种高带宽并行数据总线。DDR3 在 DDR2

的基础上继承发展而来,其数据传输速度为 DDR2 的两倍。同时,DDR3 标准可以使

单颗内存芯片的容量更为扩大,达到 512Mb 至 8Gb,从而使采用 DDR3 芯片的内存条

容量扩大到最高 16GB。此外,DDR3 的工作电压降低为 1.5V,比采用 1.8V 的 DDR2

省电 30%左右。说到底,这些指标上的提升在技术上最大的支撑来自于芯片制造工

艺的提升,90nm 甚至更先进的 45nm 制造工艺使得同样功能的 MOS 管可以制造的更

小,从而带来更快、更密、更省电的技术提升。

于 2007 年应用于 Intel P35 “Bearlake”芯片组上,但并没有像业界预想的那样

很快替代 DDR2,这中间还经历了对 SDRAM 业界影响深远的金融危机,不但使 DDR3

占领市场的速度更加减慢, 还使 DDR3 在技术上一度走在世界领先地位的内存大厂奇

梦达倒闭,实在是让人惋惜。虽然如此,DDR3 现今是并行 SDRAM 家族中速度最快的

成熟标准,JEDEC 标准规定的 DDR3 最高速度可达 1600MT/s(注,1MT/s 即为每秒钟

一百万次传输)。 不仅如此, 内存厂商还可以生产速度高于 JEDEC 标准的 DDR3 产品,

如速度为 2000MT/s 的 DDR3 产品,甚至有报道称其最高速度可高达 2500MT/s。

二、DDR 存储器特性

DDR 存储器的主要优势就是能够同时在时钟循环的上升和下降沿提取

数据,从而把给定时钟频率的数据速率提高 1 倍。例如,在 DDR200 器件中,数据传

输频率为 200 MHz,而总线速度则为 100 MHz。

DDR1、DDR2 和 DDR3 存储器的电压分别为 2.5、1.8 和 1.5V,因此与采

用 3.3V 的正常 SDRAM 芯片组相比,它们在电源管理中产生的热量更少,效率更高。

延时性是 DDR 存储器的另一特性。存储器延时性可通过一系列数字体

现,如用于 DDR1 的 2-3-2-6-T1、3-4-4-8 或 2-2-2-5。这些数字表明存储器进行某

一操作所需的时钟脉冲数,数字越小,存储越快。

这些数字代表的操作如下:CL- tRCD – tRP – tRAS – CMD。要理解

它们,您必须牢记存储器被内部组织为一个矩阵,数据保存在行和列的交叉点。

•CL:列地址选通脉冲(CAS)延迟,是从处理器发出数据内存请求到存储

器返回内存间的时间。

•tRCD:行地址选通脉冲(RAS)到 CAS 的延迟,是激活行(RAS)和激活

列(CAS)间的时间,其中,数据保存在矩阵中。

•tRP:RAS 预充电时间,是禁用数据行接入和开始另一行数据接入间的时

间。

•tRAS:激活预充电延时,是在启动下一次存储器接入前存储器必须等待

的时间。

•CMD:命令速率是存储芯片激活和向存储器发送第一个命令间的时间。有

时,该值不会公布。它通常是 T1(1 个时钟速度)或 T2(2 个时钟速度)。

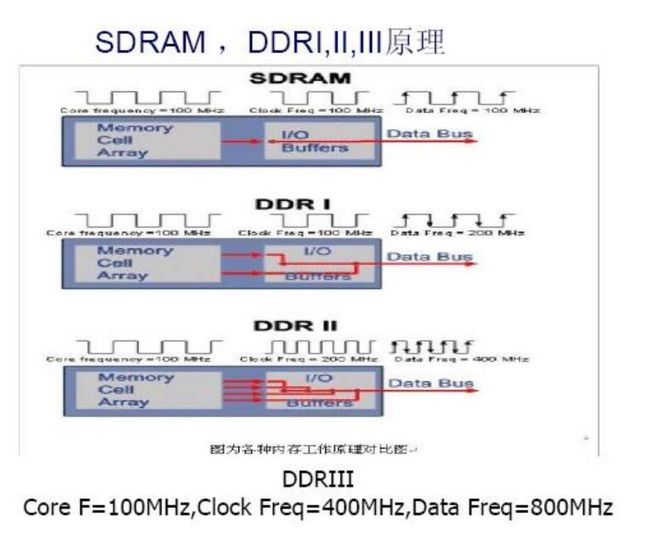

三、内存的工作速度

内存技术从 SDR,DDR,DDR2,DDR3 一路发展而来,传输速度以指数递增,

除了晶圆制造工艺的提升因素之外,还因为采用了 Double Data Rate 以及 Prefetch

两项技术。实际上,无论是 SDR 还是 DDR 或 DDR2、3,内存芯片内部的核心时钟基

本上是保持一致的,都是 100MHz 到 200MHz(某些厂商生产的超频内存除外)。DDR

即 Double Data Rate 技术使数据传输速度较 SDR 提升了一倍。如下图所示,SDR 仅

在时钟的上升沿传输数据,而 DDR 在时钟信号上、下沿同时传输数据。例如同为

133MHz 时钟,DDR 却可以达到 266Mb/s 的数传速度。

Double Data Rate 技术使数据外传速度提升了一倍,而芯片内部数

据数据传输速度的提升则是通过 Prefetch 技术实现的。所谓 Prefetch 简单的说就

是在一个内核时钟周期同时寻址多个存储单元并将这些数据以并行的方式统一传输

到 IO Buffer 中,之后以更高的外传速度将 IO Buffer 中的数据传输出去。这个更

高的速度在 DDR I 上就是通过 Double Data Rate 实现的,也正因为如此,DDR I 外

部 Clock 管脚的频率与芯片内部的核心频率是保持一致的。如下图所示为 DDR I 的

Prefetch 过程中,在 16 位的内存芯片中一次将 2 个 16bit 数据从内核传输到外部

MUX 单元,之后分别在 Clock 信号的上、下沿分两次将这 2 x 16bit 数据传输给北

桥或其他内存控制器,整个过程经历的时间恰好为一个内核时钟周期。

发展到 DDR2, 芯片内核每次 Prefetch 4 倍的数据至 IO Buffer 中,

为了进一步提高外传速度,芯片的内核时钟与外部接口时钟(即我们平时接触到的

Clock 管脚时钟)不再是同一时钟,外部 Clock 时钟频率变为内核时钟的 2 倍。同

理, DDR3 每次 Prefetch 8 倍的数据, 其芯片 Clock 频率为内核频率的 4 倍, 即 JEDEC

标准(JESD79-3)规定的 400MHz 至 800MHz,再加上在 Clock 信号上、下跳变沿同

时传输数据,DDR3 的数据传输速率便达到了 800MT/s 到 1600MT/s。具体到内存条速

度,我们以 PC3-12800 为例,其采用的 DDR3-1600 芯片核心频率为 200MHz,经过

Prefetch 后 Clock 信号频率到达 800MHz,再经过 Double Data Rate 后芯片数据传

输速率为 1600 MT/s,内存条每次传输 64 比特或者说 8 字节数据,1600x8 便得到

12800MB/s 的峰值比特率。

下表列出了 JEDEC标准(JESD79-3) 规定的 DDR3芯片及内存条相关参数。

需要说明的是,如前所述,并不是所有的内存产品都完全遵从 JEDEC 标准,有些厂

商会生产速度更高速的 DDR3 芯片,一般情况下这些芯片是从芯片检测流程中筛选出

来的频率动态范围更大的芯片,或者是可加压超频工作的芯片。

四、DDR3 与 DDR2 的差异

数据传输速率的差异是 DDR3 与 DDR2 最显著的区别,这部分上文已有描述,我们来看看其他方面的不同。

在供电方面,DDR3 的工作电压降低至 1.5V,实际上 JEDEC 标准规定

1.575V 为 DDR3 的最大安全工作电压。另外,标准也规定内存条所能经受的安全供

电电压必须大于 1.975V,当然,在这个电压下内存条可能已经不能正常工作但还不

至于损坏。

在芯片级 DDR3 引入了异步 Reset 信号,该信号主要提供两方面

的功能,其一是可以简化内存芯片上电后的初始化过程,其二是当内存系统进入一

旦进入未知或不可控状态后可以直接 Reset 而无需掉电重启。

在接口方面,以普通的 Un-Buffer 内存条为例,DDR3 与 DDR2 均为

240 个 pin 脚,尺寸一致但防呆槽的位置不同,由于工作电压不同二者在电气特性

上也是互不兼容的。

在系统设计方面 DDR3 与 DDR2 最大的区别在于 DDR3 将时钟、地

址及控制信号线的终端电阻从计算机主板移至内存条上,这样一来在主板上将不需

要任何端接电阻。为了尽可能减小信号反射,在内存条上包括时钟线在内的所有控

制线均采用 Fly-by 拓扑结构。同时,也是因为 Fly-by 的走线结构致使控制信号线

到达每颗内存颗粒的长度不同从而导致信号到达时间不一致。这种情况将会影响内

存的读写过程,例如在读操作时,由于从内存控制器发出的读命令传送到每颗内存

芯片的时间点不同,将导致每颗内存芯片在不同的时间向控制器发送数据。为了消

除这种影响,需要在对内存进行读写等操作时对时间做补偿,这部分工作将由内存

控制器完成。DDR3 总线的系统框架如下图所示,其中红线代表 DQ、DM 以及差分 DQS

信号线,黑线代表时钟、地址及控制信号线,T 代表相应的端接电阻。

五、DDR3 测试

JEDEC 标准规定的 DDR3 测试主要分为三个方面,分别为:

· 时钟测试

· 时序测试

· 电气性能测试

其中时钟测试主要测试时钟信号的周期、上下沿脉宽、周期抖动以及连

续 n 周期累积误差等指标; 时序测试主要测试数据读写时的建立保持时间相关参数;

电气性能测试主要测试信号完整性相关指标, 主要包括各信号的斜率以及直/交流逻

辑高/低电平等指标。完整的 DDR3 测试项目不但种类繁多并且涉及到信号读写分离

等复杂的判断过程,手工测量不但费时费力且难以保证测量的准确性。针对于此,

力科专门推出了最新的 QPHY-DDR3 自动化测试软件包,它将以图形化的界面帮助用

户完成从被测信号的搭接、信号采集与读写分离、自动测试与分析到最终的测试报

告生成这一系列完整的测试工作。

六、结语

可以预期的是,DDR3 将在未来的两年内加速占领更多的市场份额,

Intel 的 Core i7 处理器以及 AMD 的 Phenom II 处理器均内置内存控制器并且支持

DDR3,同时 Core i7 处理器将不支持 DDR2。