LVPECL转LVDS端接优化的经历

这两天画板子要处理PXIe的那几个3.3V的LVPECL信号。受FPGA的限制,需要在片外把电平转换成LVDS。

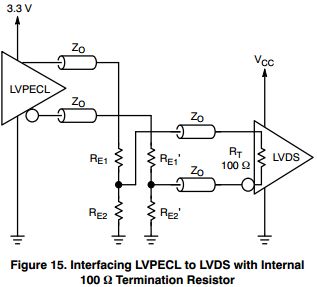

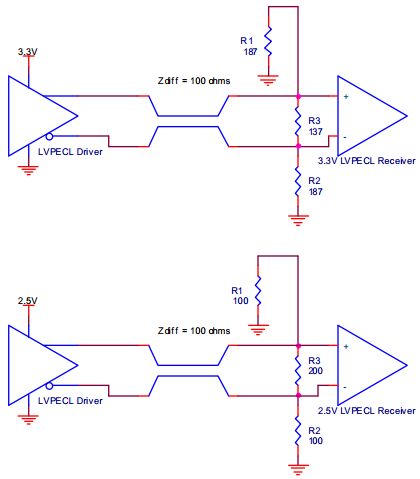

一开始用了ONSEMI一篇应用笔记中提到的这样一个电路:

这个电路画出来之后发现那4个电阻还是比较占板面空间的,导致那一区域特别挤,等长也走的很艰难。我的期望是如果RE1和RE2的阻值是一样的,就可以用排阻来减小布局面积。

文中给出的RE1和RE2是不相等的。虽说还真有不等值的排阻,以前挤模拟板的时候用过,但这次这两个阻值集成在一起的不好买到。

项目中电源芯片的输出数比较冗余,有空闲的电源可以用,借助这个条件想了想办法。

LVPECL端接

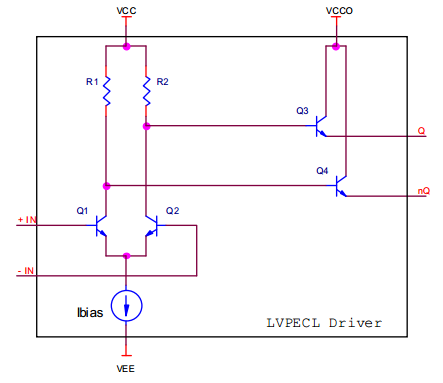

LVPECL的输出级长成这个模样:

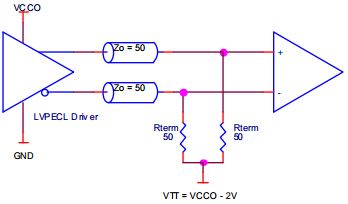

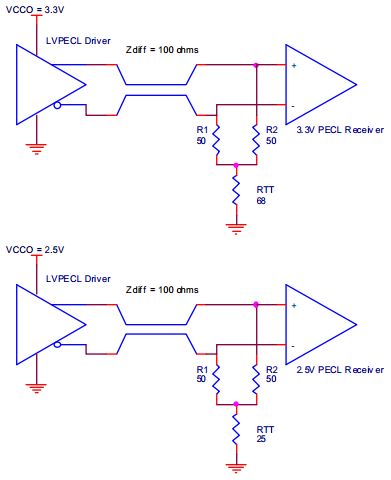

标准端接方式是两根线分别50Ω电阻接到VCCO-2.0V上:

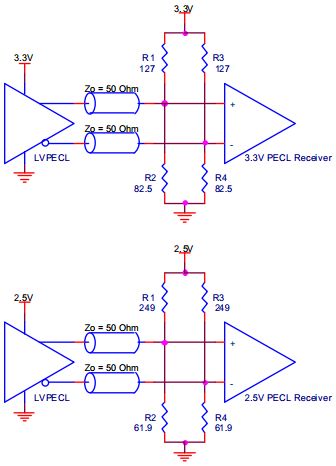

VCCO为3.3V或2.5V时,对应的VTT是1.3V和0.5V。为了端接单做这样一个电源轨出来不是所有场合都愿意的(尤其是0.5V这样低的电源),于是出现了两种常用的等效端接——戴维南等效端接和T端接:

戴维南等效端接的原理就是它的名字。

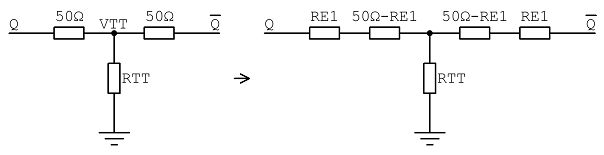

T端接的思路是,利用差分信号的共模电压,在两个50Ω电阻的汇合点产生VTT。以3.3V为例,LPVECL的共模电压差不多1.9V,这样可以计算出汇合点等于VTT=1.3V时,两个50Ω电阻和RTT的分压。

标准端接方式实际上与T端接有很强的联系,相当于把T端接的接地点抬高到VTT,从而减小RTT到0。也就是说只要保证在正负两个信号线电压都等于1.9V时,两个50Ω电阻的汇合点是VTT,那么T网络的第三端电压是多少是没有关系的,只要对应地调整RTT就可以了。这个结论对后面比较有用。

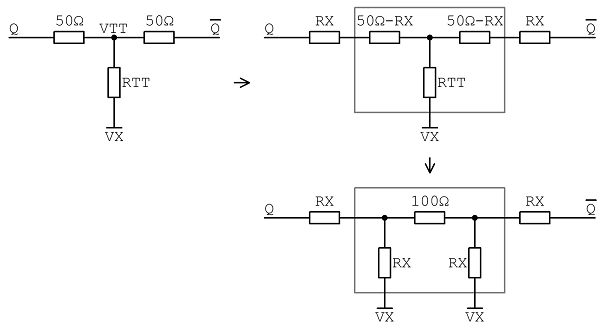

T端接衍生出PI端接,最开头给出的那个电路应该就是PI端接的方式。把这个三端T网络做T-Π变换:

设计思路

主要约束有:

- LVPECL的差分端接阻值;

- LVPECL的VTT电压;

- LVDS的共模电压;

- LVDS的差分幅度。

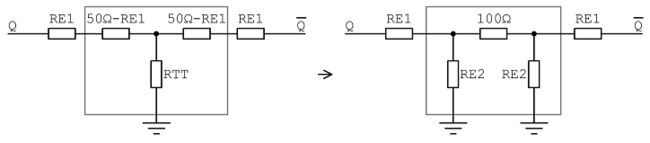

最开头ONSEMI的那个电路,可以想象如果把RE2、RE2’和RT看成一个Π网络,做T-Π变换,就会得到一个T端接。

也就是说它可以通过把T端接的R1和R2(两个50Ω电阻)分别拆成串联的两个电阻,

其中一个与RTT做T-Π变换得到。

如果限定T-Π变换之后,跨接在两个接地电阻之间的电阻RT恰好是LVDS的100Ω(FPGA自带),那么这个拆分串联的方式是唯一的。

现在我可以通过额外的电源,来调整T网络本来接地的那个点的电压,从而影响RTT以至RE1、RE2的值。也就是说,VTT通过RTT接到的不是0V了:

这里的变量有VX、RTT、RX三个,需要三个方程来解。其中一个是第一张图中共模的电流定律

其中1.9是LVPECL的共模电压,VTT取1.3V。

然后是T-Π变换的两个方程

这样可以解出来

也就是说,用电源芯片产生一个1.15V的电压,再用四个30.9Ω的电阻(或排阻)就可以构成一个端接了。

LVDS共模电压和差分幅度的检验

按照上面的结果,可以算出输出给LVDS的共模电压

我的LVDS要求的最大共模电压是1.425V,这个超了不少。这个方法似乎没有那么理想。

看来要动用LVPECL的裕量了。LVPECL要求VTT是VCCO-2.0±0.2V,那么我用3.3V-2.2V=1.1V代到上面方程中去解,得到

进一步榨取50Ω的裕量,取55Ω得到

这个已经看起来差不多了。

输出差分幅度其实不太用检验,300多mV吧,对付个LVDS没有什么问题。

最终取得的参数是

| VICM | VTT | VOCM |

|---|---|---|

| 1.85 | 1.10 | 1.38 |

| 1.90 | 1.11 | 1.40 |

| 1.95 | 1.12 | 1.42 |

可以用36Ω的排阻。感觉都是踩在极限上,先这么将就着试试看吧。走过路过恳请指教。