TTL和CMOS的不同

一. TTL和CMOS的介绍:

1.TTL电路:全称Transistor-Transistor Logic,即BJT-BJT逻辑门电路,是数字电子技术钟常用的一种逻辑门电路,应用较早,技术比较成熟,TTL主要有BJT(Bipolar Junction Transistor即双极结型晶体管,也就是所说的晶体三极管)和电阻构成,是数字集成电路的一大门类,采用双极型工艺制造。主要经历了三代的发展:

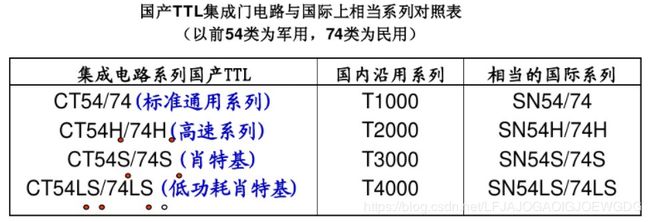

● 第一代TTL包括SN54/74系列,54系列和74系列具有相同的字系列,两个系列的参数基本相同,不同之处主要是电源电压范围和工作环境温度范围,主要有低功耗L、高速H,

● 第二代包括肖特基系列S和低功耗肖特基系列LS.

● 第三代采用等平面工艺制造的先进系列AS、ALS

2. CMOS电路:CMOS英文全称为Complementary Metal-Oxide-Semiconductor即互补金属-氧化物-半导体(PMOS管和NMOS管)共同构成的互补型MOS集成电路制造工艺,他的特点是低功耗。CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,诞生于20世纪60年代,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件,CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力远优于TTL,此外,几乎所有的超大规模的存储器件,以及PLD器件都采用CMOS工艺制造,且费用低。

● 第一代CMOS电路为4000系列,随后发展为4000B系列。

● 第二代高速的CMOS系列HC(HCT)系列。

● 第三代先进CMOS系列AC(ACT)系列

二、性能对比:

◆ 原理和性能的不同:

TTL电路:集成电路的主要型式为晶体管-晶体管逻辑门(transistor-transistor logic gate),电流控制器件、速度快,传输延时时间短(5-10ns),但是功耗大。

CMOS电路: CMOS电路的优点是噪声容限较宽,静态功耗很小,电压控制器件、速度慢,传输延迟时间长(25-50ns),但功耗低。COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。

◆ 电平的不同:

TTL电路:大部分都采用5V电源,输入高电平大于等于2.0V,输入低电平小于等于0.8V,输出高电平大于等于2.4V,输出低电 平小于等于0.4V。

CMOS电路:输入高电平大于等于0.7*VCC,输入低电平小于等于0.2*VCC,输出高电平近似等于VCC,输出低电平近似等于0V。

从上面可以看出:

在 同样5V电源电压情况下,COMS电路可以直接驱动TTL,因为CMOS的输出高电平大于2.0V,输出低电平小于0.8V;而TTL电路则不能直接驱动 CMOS电路,如果想TTL驱动CMOS,或者3.3V的CMOS驱动5V的CMOS就要采取以下几种方法:

(1) 晶体管+上拉电阻法

(2) OC/OD 器件+上拉电阻法

(3) 74xHCT系列芯片升压 (3.3V→5V)

74系列中分为很多种,而我们平时用得最多的应该是以下几种:74LS,74HC,74HCT这三种,这三种系列在电平方面的区别如下:

输入电平 输出电平

74LS TTL电平 TTL电平

74HC COMS电平 COMS电平

74HCT TTL电平 COMS电平

还有个74LV系列,这里面有74LV573,输入TTL,输出CMOS电平,但74LV245的输入和输出都是CMOS电平

(4) 超限输入降压法 (5V→3.3V, 3.3V→1.8V, ...)

凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制 (改变了输入级保护电路)。例如,74AHC/VHC 系列芯片,其 datasheets 明确注明"输入电压范围为0~5.5V",如果采用 3.3V 供电,就可以实现 5V→3.3V 电平转换。

(5) 专用电平转换芯片

最著名的就是 164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的 (俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。

(6) 电阻分压法

(7) 限流电阻法

如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如 74HC 系列为 20mA),仍然是安全的。

◆ 输入管脚的不同:

TTL电路:

1 . TTL是电流驱动,无锁定效应。

2. TTL门电路中输入端负载特性(输入端带电阻特殊情况的处理):

悬空时相当于输入端接高电平。因为这时可以看作是输入端接一个无穷大的电阻。在门电路输入端串联10K电阻后再输 入低电平,输入端出呈现的是高电平而不是低电平。因为由TTL门电路的输入端负载特性可知,只有在输入端接的串联电阻小于910欧 时,它输入来的低电平信号才能被门电路识别出来,串联电阻再大的话输入端就一直呈现高电平。这个一定要注意。COMS门电路就不用考虑这些了

CMOS电路:

1. 锁定效应:输入电流超过1mA 就有可能烧毁CMOS器件,当在输入太大的电流时,内部的电流急剧增大,除非切断电源,电流一直在增大。这种效应就是锁定效应。当产生锁定效应时,COMS的内部电流能达到40mA以上,很容易烧毁芯片,基于以上问题在进行设计时根据具体情况可以采取以下几点防御措施。

1>. 芯片的电源输入端加去耦电路,防止VDD端出现瞬间的高压,同时在VDD和外电源之间加限流电阻,即使有大的电流也不让它进去。。

2>.在输入端和输出端加钳位电路,使输入和输出不超过不超过规定电压。

3>.输入端接低内阻的信号源时,要在输入端和信号源之间要串联限流电阻,使输入的电流限制在1mA之内。

4>.当接长信号传输线时,必然有较大的分布电容和分布电感,易形成LC振荡,特别当输入端一旦发生负电压,极易破坏 CMOS中的保护二极管。其保护办法为在输入端处接一个电阻,如图3所示, R=VDD/1mA。

5>.当输入端接大电容时,应该在输入端和电容间接保护电阻。电阻值为R=V0/1mA.V0是外界电容上的电压。

6>.输入信号的上升和下降时间不易过长,否则一方面容易造成虚假触发而导致器件失去正常功能,另一方面还会造成大的损耗。对于74HC系列限于0.5us以内。若不满足此要求,需用施密特触发器件进行输入整形

7>. 当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启COMS路得电 源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭COMS电路的电源

2. CMOS 器件不用的输入端必须连到高电平或低电平, 这是因为 CMOS 是高输入阻抗器件, 理想状态是没有输入电流的. 如果不用的输入引脚悬空, 很容易感应到干扰信号, 影响芯片的逻辑运行, 甚至静电积累永久性的击穿这个输入端, 造成芯 片失效,所以要注意以下不用的管脚不要悬空,要接上拉电阻或者下拉电阻,给它一个恒定的电平。

◆ 输出管脚的不同:

1.什么叫做图腾柱,它与开漏电路有什么区别:

TTL集成电路中,输出有接上拉三极管的输出叫做图腾柱输出,没有的叫做OC门。因为TTL就是一个三级关,图腾柱也就是两个三级管推挽相连。所以推挽就是图腾。一般图腾式输出,高电平400UA,低电平8MA

2.输出端的保护:

MOS管输出端:

1>. MOS器件输出端既不允许和电源短接,也不允许和地短接,否则输出级的MOS管就会因过流而损坏;

2>. 除了三端输出器件外,不允许两个器件输出端并接,因为不同的器件参数不一致,有可能导致NMOS和PMOS器件同时导通,形成大电流。但为了增加电路的驱动能力,允许把同一芯片上的同类电路并联使用。

3>.当CMOS电路输出端有较大的容性负载时,流过输出管的冲击电流较大,易造成电路失效。为此,必须在输出端与负载电容间串联一限流电阻,将瞬态冲击电流限制在10mA以下