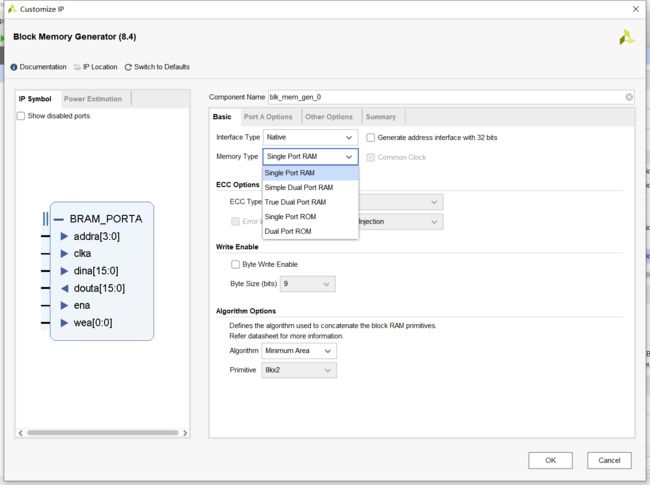

打开 IP Catalog,搜索 Block Memory Generator,即可看到其 Memory Type 可分为 5 中,分别是单口 RAM(Single Port RAM)、伪双口 RAM(Simple Dual Port RAM)、真双口 RAM(True Dual Port RAM)、单口 ROM(Single Port ROM)、双口 ROM(Dual Port ROM)。

单口 RAM 与伪双口 RAM、真双口 RAM 的区别在于:

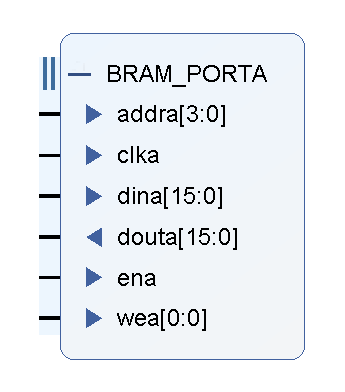

单口 RAM 只有一个时钟(clka)(时钟上升沿到来时对数据进行写入或者读出)、一组输入输出数据线(dina & douta)、一组地址线(addra)、一个使能端(ena)(“ena == 1”时可进行读或写的操作,“ena == 0”时无法进行读或写的操作)、一个写使能端(wea)(在“ena == 1”的情况下:“wea == 1”时只写不读,“wea == 0”时只读不写)。单口读、写无法同时进行,只能或读或写。

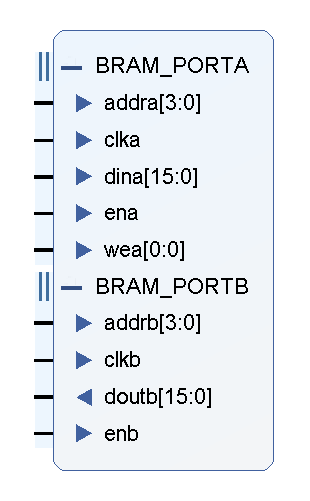

伪双口 RAM 有两个时钟(clka & clkb)、一组输入输出数据线(dina & doutb)、两组地址线(addra & addrb),两个使能端(ena & enb)、一个写使能端(wea)。一个端口只读(Port a),另一个端口只写(Port b)。整体上,读、写可以同时进行。

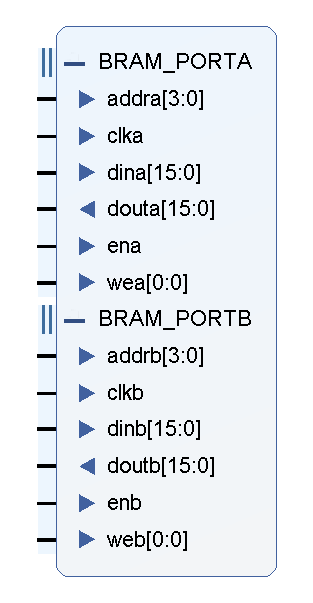

真双口 RAM 有两个时钟(clka & clkb)、两组输入输出数据线(dina & douta & dinb & doutb)、两组地址线(addra & addrb),两个使能端(ena & enb)、两个写使能端(wea & web)。两个端口都可以进行读写操作(Port a 和 Port b 可以一起读或者一起写或者一个读一个写)。整体上,读、写可以同时进行。

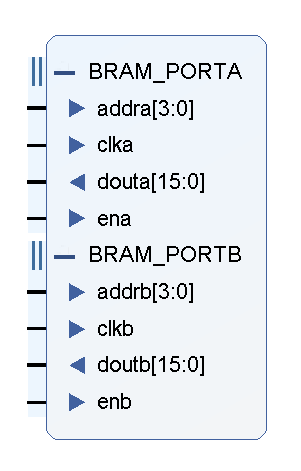

如下是单口 RAM、 伪双口 RAM 、真双口 RAM 的 IP 模块:

单口 ROM 与双口 ROM 的区别在于:

单口 ROM 只有一个时钟(clka)、一组输出数据线(douta)、一组地址线(addra)、一个使能端(ena)。只能进行读操作,且一个时钟只能读出某个地址上的一组数据。

双口 ROM 有两个时钟(clka & clkb)、两组输出数据线(douta & doutb)、两组地址线(addra & addrb)、两个使能端(ena & enb)。也是只能进行读操作,且每个端口中,一个时钟只能读出某个地址上的一组数据。其实和单口 ROM 没什么区别,基本上可以当成是两个单口 ROM 拼接而成的罢了,只是存储的数据是共享的。

如下是单口 RAM、 伪双口 RAM 、真双口 RAM 的 IP 模块:

最后,再声明一下,在使用双口 RAM 还是双口 ROM 的时候,一定要避免在同一时刻对同一地址进行读或写的操作,防止发生冲突(这也是不允许的)。