- (179)时序收敛--->(29)时序收敛二九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (180)时序收敛--->(30)时序收敛三十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (158)时序收敛--->(08)时序收敛八

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛八(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (159)时序收敛--->(09)时序收敛九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (160)时序收敛--->(10)时序收敛十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (153)时序收敛--->(03)时序收敛三

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (121)DAC接口--->(006)基于FPGA实现DAC8811接口

FPGA系统设计指南针

FPGA接口开发(项目实战)fpga开发FPGAIC

1目录(a)FPGA简介(b)IC简介(c)Verilog简介(d)基于FPGA实现DAC8811接口(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电

- FPGA复位专题---(3)上电复位?

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发

(3)上电复位?1目录(a)FPGA简介(b)Verilog简介(c)复位简介(d)上电复位?(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限

- (182)时序收敛--->(32)时序收敛三二

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三二(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- quartus频率计 时钟设置_FPGA021 基于QuartusⅡ数字频率计的设计与仿真

weixin_39876739

quartus频率计时钟设置

摘要随着科技电子领域的发展,可编程逻辑器件,例如CPLD和FPGA的在设计中得到了广泛的应用和普及,FPGA/CPLD的发展使数字设计更加的灵活。这些芯片可以通过软件编程的方式对内部结构进行重构,使它达到相应的功能。这种设计思想改变了传统的数字系统设计理念,促进了EDA技术的迅速发展。数字频率计是一种基本的测量仪器。它被广泛应用与航天、电子、测控等领域。采用等精度频率测量方法具有测量精度保持恒定,

- Quartus sdc UI界面设置(二)

落雨无风

IC设计fpgafpga开发

Quartussdc设置根据一配置quartus综合简单流程(一)上次文章中,说了自己写sdc需要配置的分类点,这次将说明在UI界面配置sdc。1.在Quartus软件中,导入verilog设计之后,打开Tools/TimeQuestTimingAnalyzer界面大致分为上下两部分,上半部分左侧显示Report、Tasks,右侧显示欢迎界面;下半部分显示Console和History,此处缺图,

- 2020-11-12 写单片机内存的脚本 nc openocd 事务自动测试

linuxScripter

这是写单片机内存的脚本:z@z-ThinkPad-T400:~/zworkT400/EDA_heiche/zREPOgit/simple-gcc-stm32-project$catz.wholeRun.oneCase.cmdcattmp6.toWrite|awk'{system("echomwb"$1""$2"|nclocalhost4444");}'catUSER/DEBUG/debug.h|g

- VLSI电路单元的自动布局:全局布局基础介绍

Jaaiko

数学建模算法开源图论matlab

2024年华数杯全国大学生数学建模竞赛B题为:VLSI电路单元的自动布局。本题主要关注的是全局布局问题。学术界针对全局布局的评估模型和优化方法的研究历史悠久。本文借题顺势介绍全局布局的一些重点基础内容和相关工具/资料,以期为对EDA算法设计领域感兴趣、对数学建模感兴趣的人降低研究门槛。VLSI是超大规模集成电路的简称。完成一个VLSI设计的流程十分复杂,包含多种数据格式的转化,其中将逻辑网表转变为

- VLSI 电路单元的自动布局-2024华数杯B题

2401_84314384

算法python数学建模

摘要超大规模集成电路设计通常采用电子设计自动化(EDA)的方式进行,布局是EDA工具的核心的核心。本文通过构建的线长评估模型及网格密度评估模型,并在此基础上对模型进行优化,最后利用模型实现VLSI电路单元的自动布局。问题一:基于结合直线型斯坦纳最小树思想的优化HPWL模型评估与电路单元连线接口坐标相关的线长。本题需要建立与电路单元连线接口坐标相关的线长评估模型,最小化每组估计线长与对应RSMT的差

- 牛客Verilog语法刷题Day 1

SAChemAdvance

刷题fpga开发

校验器的输入是由原始数据位和校验位组成对于奇偶校验,若合法编码中奇数位发生了错误,也就是编码中的1变成0或0变成1,则编码中1的个数的奇偶性就发生了变化,从而可以发现错误,但不能检测出是哪些位出错。对于一个设置为50MHz的移位寄存器,把16左移到128,需要()nsA.30B.40C.50D.60本题答案选D,从16到128需要3位,50MHz的时钟为20ns,移动3位则为60ns时间(s)=1

- 连续发送多个数据(uart串口RS232协议/verilog详细代码+仿真)

勇敢牛牛(FPGA学习版)

fpga开发嵌入式硬件matlab智能硬件

写在前言以下内容详细源文件,已经上传个人主页资源,需要自取~目录写在前言需求分析UART简介整体架构流程小结需求分析使用串口(rs232协议)间隔1s连续发送16byte的数据。由于每次发送的数据只有8bit,16byte=128bit,所以要发送16帧。UART简介这里实验所使用的参数有:rs232通信协议+9600bps+quartus18.0+modelsim2020异步通信:UART是一种

- 事件驱动的架构及应用

treewinder

EDAsoa分布式应用电子政务processing企业应用jms

事件驱动的架构及应用来源:软件世界作者:李臣亮Gartner在2003年引入了一个新术语事件驱动架构(EventDrivenArchitecture,EDA),主要用于描述一种基于事件的范例。EDA是一种用于进行设计和实现应用和系统的方法—在这些应用和系统里,事件所触发的消息可以在独立的、非耦合的组件和服务之间传递,这些模块彼此并不知晓对方。这些应用程序中的EDA极大地改进了企业或政府响应不同的、

- 第11周作业---HLS编程环境入门

pss_runner

目录HLS概念HLS是什么HLS与VHDL/Verilog有什么关系?HLS技术问题HLS开发步骤环境搭建编写test.cpp文件预编译cpp文件HLS概念HLS是什么高层次综合(High-levelSynthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括C、C++、SystemC等,通常有着较高的抽象度,并且往往不具有时

- VCS简介

XtremeDV

VCS快速实战指南

1.2.1关于VCSVCS是VerilogCompiledSimulator的缩写。VCSMX®是一个编译型的代码仿真器。它使你能够分析,编译和仿真Verilog,VHDL,混合HDL,SystemVerilog,OpenVera和SystemC描述的设计。它还为您提供了一系列仿真和调试功能,以验证您的设计。这些功能提供了源码调试和仿真结果查看功能。vcs提供了一系列的feature,如下图:业界

- vcs 入门

hemmingway

Xilinx/FPGA

synopsysvcs软件是仿真和验证的软件,必须掌握。vcs即verilogcompilesimulator支持verilog,systemVerilog,openvera,systemC等语言,同时也有代码覆盖率检测等功能。可以合第三方软件集合使用,例如Vera,Debussy,Specman等等。在linux下调用vcs,需要设置相应的环境变量。1、学习vcs最好的资料肯定是官方的说明书,安

- 探索未来编程新纪元:flow-eda——可视化低代码的创新实践

史锋燃Gardner

探索未来编程新纪元:flow-eda——可视化低代码的创新实践flow-eda采用springboot+vue/react搭建的一个基于事件驱动的流式低代码编程应用程序,您可以在编辑器中采用拖拽的形式来实现业务编程工作,一键运行和停止,让开发工作变得更简单高效。项目地址:https://gitcode.com/gh_mirrors/fl/flow-eda项目介绍在软件开发领域,flow-eda正迅

- Xilinx Vivado的RTL分析(RTL analysis)、综合(synthesis)和实现

2401_84185145

程序员fpga开发

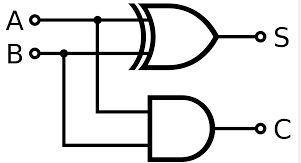

理论上,FPGA从编程到下载实现预期功能的过程最少仅需要上述7个步骤中的4、5、6和7,即RTL分析、综合、实现和下载。其中的RTL分析、综合、实现的具体含义和区别又是什么?2、RTL分析(RTLanalysis)一般来讲,通常的设计输入都是Verilog、VHDL或者SystemVerilog等硬件描述语言HDL编写的文件,RTL分析这一步就是将HDL语言转化成逻辑电路图的过程。比如HDL语言描

- 第R3周:天气预测

Jessica2017lj

python

本文为[365天深度学习训练营]中的学习记录博客参考文章:第R3周:LSTM-火灾温度预测(训练营内部可读)作者:[K同学啊]任务说明:该数据集提供了来自澳大利亚许多地点的大约10年的每日天气观测数据。你需要做的是根据这些数据对RainTomorrow进行一个预测,这次任务任务与以往的不同,我增加了探索式数据分析(EDA),希望这部分内容可以帮助到大家。我的环境:●语言环境:Python3.8●编

- 1. Verilog2. C语言3. 数组4. 关键词5. 模块

行者..................

c语言fpga开发开发语言FPGA

###5.2.4Verilog数组VSC语言数组####Verilog数组在Verilog语言中,数组通常被称作内存。以下是一个定义的例子:```verilog(*ram_style="distributed"*)reg[0:31]MyMem[0:7]```这行代码定义了一个长度为32位,包含7个元素的数组。具体来说:-`reg[0:31]`表示每个数组元素是一个32位的寄存器。-`MyMem[0

- (170)时序收敛--->(20)时序收敛二十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- 初识 Verilog

栀栀栀

笔记

Verilog综述:类C,并行,自顶向下,硬件描述语言,VHDL,VerilogHDL。VHDL,VerilogHDL,两种不同描述语言。Verilog语言(并行,硬件)类似C语言(串行,软件)。基础知识:1.Verilog的四值逻辑系统0低电平1高电平X不确定Z高阻态2.Verilog的数据类型寄存器数据类型表示一个抽象的数据存储单元,只能在always语句和initial语句等过程语句中被赋值

- Verilog刷题笔记31

十六追梦记

笔记

题目:Supposeyouaredesigningacircuittocontrolacellphone’sringerandvibrationmotor.Wheneverthephoneneedstoringfromanincomingcall(),yourcircuitmusteitherturnontheringer()orthemotor(),butnotboth.Ifthephoneis

- Quartus网盘资源下载与安装 附图文安装教程

学习天使Alice

fpga开发学习

如大家所了解的,Quartus是一种FPGA设计软件(相信理工科的小伙伴,很多都接触或学习过FPGA),旨在为数字电路设计师提供一个高效、便捷的开发环境。它可以帮助用户完成数字逻辑电路的设计、仿真、综合和布局,以及与外围设备进行通信和控制。Quartus支持多种编程语言,包括VHDL、Verilog等,并具有丰富的功能和工具库,可满足不同级别、不同规模的数字电路设计需求。收藏的Quartus安装包

- 2020-03-24

黑乎乎AI

Datawhale零基础入门数据挖掘-Task2数据分析【代码摘要】赛题:零基础入门数据挖掘-二手车交易价格预测地址:[https://tianchi.aliyun.com/competition/entrance/231784/introduction?spm=5176.12281957.1004.1.38b02448ausjSX]EDA的价值主要在于熟悉数据集,了解数据集,对数据集进行验证来确

- Verilog刷题笔记59

十六追梦记

笔记

题目:Exams/m2014q6c解题:moduletop_module(input[6:1]y,inputw,outputY2,outputY4);assignY2=y[1]&w==0;assignY4=(y[2]&w==1)|(y[3]&w==1)|(y[5]&w==1)|(y[6]&w==1);endmodule结果正确:注意点:起初,我的代码有错误,代码如下:moduletop_modul

- 312个免费高速HTTP代理IP(能隐藏自己真实IP地址)

yangshangchuan

高速免费superwordHTTP代理

124.88.67.20:843

190.36.223.93:8080

117.147.221.38:8123

122.228.92.103:3128

183.247.211.159:8123

124.88.67.35:81

112.18.51.167:8123

218.28.96.39:3128

49.94.160.198:3128

183.20

- pull解析和json编码

百合不是茶

androidpull解析json

n.json文件:

[{name:java,lan:c++,age:17},{name:android,lan:java,age:8}]

pull.xml文件

<?xml version="1.0" encoding="utf-8"?>

<stu>

<name>java

- [能源与矿产]石油与地球生态系统

comsci

能源

按照苏联的科学界的说法,石油并非是远古的生物残骸的演变产物,而是一种可以由某些特殊地质结构和物理条件生产出来的东西,也就是说,石油是可以自增长的....

那么我们做一个猜想: 石油好像是地球的体液,我们地球具有自动产生石油的某种机制,只要我们不过量开采石油,并保护好

- 类与对象浅谈

沐刃青蛟

java基础

类,字面理解,便是同一种事物的总称,比如人类,是对世界上所有人的一个总称。而对象,便是类的具体化,实例化,是一个具体事物,比如张飞这个人,就是人类的一个对象。但要注意的是:张飞这个人是对象,而不是张飞,张飞只是他这个人的名字,是他的属性而已。而一个类中包含了属性和方法这两兄弟,他们分别用来描述对象的行为和性质(感觉应该是

- 新站开始被收录后,我们应该做什么?

IT独行者

PHPseo

新站开始被收录后,我们应该做什么?

百度终于开始收录自己的网站了,作为站长,你是不是觉得那一刻很有成就感呢,同时,你是不是又很茫然,不知道下一步该做什么了?至少我当初就是这样,在这里和大家一份分享一下新站收录后,我们要做哪些工作。

至于如何让百度快速收录自己的网站,可以参考我之前的帖子《新站让百

- oracle 连接碰到的问题

文强chu

oracle

Unable to find a java Virtual Machine--安装64位版Oracle11gR2后无法启动SQLDeveloper的解决方案

作者:草根IT网 来源:未知 人气:813标签:

导读:安装64位版Oracle11gR2后发现启动SQLDeveloper时弹出配置java.exe的路径,找到Oracle自带java.exe后产生的路径“C:\app\用户名\prod

- Swing中按ctrl键同时移动鼠标拖动组件(类中多借口共享同一数据)

小桔子

java继承swing接口监听

都知道java中类只能单继承,但可以实现多个接口,但我发现实现多个接口之后,多个接口却不能共享同一个数据,应用开发中想实现:当用户按着ctrl键时,可以用鼠标点击拖动组件,比如说文本框。

编写一个监听实现KeyListener,NouseListener,MouseMotionListener三个接口,重写方法。定义一个全局变量boolea

- linux常用的命令

aichenglong

linux常用命令

1 startx切换到图形化界面

2 man命令:查看帮助信息

man 需要查看的命令,man命令提供了大量的帮助信息,一般可以分成4个部分

name:对命令的简单说明

synopsis:命令的使用格式说明

description:命令的详细说明信息

options:命令的各项说明

3 date:显示时间

语法:date [OPTION]... [+FORMAT]

- eclipse内存优化

AILIKES

javaeclipsejvmjdk

一 基本说明 在JVM中,总体上分2块内存区,默认空余堆内存小于 40%时,JVM就会增大堆直到-Xmx的最大限制;空余堆内存大于70%时,JVM会减少堆直到-Xms的最小限制。 1)堆内存(Heap memory):堆是运行时数据区域,所有类实例和数组的内存均从此处分配,是Java代码可及的内存,是留给开发人

- 关键字的使用探讨

百合不是茶

关键字

//关键字的使用探讨/*访问关键词private 只能在本类中访问public 只能在本工程中访问protected 只能在包中和子类中访问默认的 只能在包中访问*//*final 类 方法 变量 final 类 不能被继承 final 方法 不能被子类覆盖,但可以继承 final 变量 只能有一次赋值,赋值后不能改变 final 不能用来修饰构造方法*///this()

- JS中定义对象的几种方式

bijian1013

js

1. 基于已有对象扩充其对象和方法(只适合于临时的生成一个对象):

<html>

<head>

<title>基于已有对象扩充其对象和方法(只适合于临时的生成一个对象)</title>

</head>

<script>

var obj = new Object();

- 表驱动法实例

bijian1013

java表驱动法TDD

获得月的天数是典型的直接访问驱动表方式的实例,下面我们来展示一下:

MonthDaysTest.java

package com.study.test;

import org.junit.Assert;

import org.junit.Test;

import com.study.MonthDays;

public class MonthDaysTest {

@T

- LInux启停重启常用服务器的脚本

bit1129

linux

启动,停止和重启常用服务器的Bash脚本,对于每个服务器,需要根据实际的安装路径做相应的修改

#! /bin/bash

Servers=(Apache2, Nginx, Resin, Tomcat, Couchbase, SVN, ActiveMQ, Mongo);

Ops=(Start, Stop, Restart);

currentDir=$(pwd);

echo

- 【HBase六】REST操作HBase

bit1129

hbase

HBase提供了REST风格的服务方便查看HBase集群的信息,以及执行增删改查操作

1. 启动和停止HBase REST 服务 1.1 启动REST服务

前台启动(默认端口号8080)

[hadoop@hadoop bin]$ ./hbase rest start

后台启动

hbase-daemon.sh start rest

启动时指定

- 大话zabbix 3.0设计假设

ronin47

What’s new in Zabbix 2.0?

去年开始使用Zabbix的时候,是1.8.X的版本,今年Zabbix已经跨入了2.0的时代。看了2.0的release notes,和performance相关的有下面几个:

:: Performance improvements::Trigger related da

- http错误码大全

byalias

http协议javaweb

响应码由三位十进制数字组成,它们出现在由HTTP服务器发送的响应的第一行。

响应码分五种类型,由它们的第一位数字表示:

1)1xx:信息,请求收到,继续处理

2)2xx:成功,行为被成功地接受、理解和采纳

3)3xx:重定向,为了完成请求,必须进一步执行的动作

4)4xx:客户端错误,请求包含语法错误或者请求无法实现

5)5xx:服务器错误,服务器不能实现一种明显无效的请求

- J2EE设计模式-Intercepting Filter

bylijinnan

java设计模式数据结构

Intercepting Filter类似于职责链模式

有两种实现

其中一种是Filter之间没有联系,全部Filter都存放在FilterChain中,由FilterChain来有序或无序地把把所有Filter调用一遍。没有用到链表这种数据结构。示例如下:

package com.ljn.filter.custom;

import java.util.ArrayList;

- 修改jboss端口

chicony

jboss

修改jboss端口

%JBOSS_HOME%\server\{服务实例名}\conf\bindingservice.beans\META-INF\bindings-jboss-beans.xml

中找到

<!-- The ports-default bindings are obtained by taking the base bindin

- c++ 用类模版实现数组类

CrazyMizzz

C++

最近c++学到数组类,写了代码将他实现,基本具有vector类的功能

#include<iostream>

#include<string>

#include<cassert>

using namespace std;

template<class T>

class Array

{

public:

//构造函数

- hadoop dfs.datanode.du.reserved 预留空间配置方法

daizj

hadoop预留空间

对于datanode配置预留空间的方法 为:在hdfs-site.xml添加如下配置

<property>

<name>dfs.datanode.du.reserved</name>

<value>10737418240</value>

- mysql远程访问的设置

dcj3sjt126com

mysql防火墙

第一步: 激活网络设置 你需要编辑mysql配置文件my.cnf. 通常状况,my.cnf放置于在以下目录: /etc/mysql/my.cnf (Debian linux) /etc/my.cnf (Red Hat Linux/Fedora Linux) /var/db/mysql/my.cnf (FreeBSD) 然后用vi编辑my.cnf,修改内容从以下行: [mysqld] 你所需要: 1

- ios 使用特定的popToViewController返回到相应的Controller

dcj3sjt126com

controller

1、取navigationCtroller中的Controllers

NSArray * ctrlArray = self.navigationController.viewControllers;

2、取出后,执行,

[self.navigationController popToViewController:[ctrlArray objectAtIndex:0] animated:YES

- Linux正则表达式和通配符的区别

eksliang

正则表达式通配符和正则表达式的区别通配符

转载请出自出处:http://eksliang.iteye.com/blog/1976579

首先得明白二者是截然不同的

通配符只能用在shell命令中,用来处理字符串的的匹配。

判断一个命令是否为bash shell(linux 默认的shell)的内置命令

type -t commad

返回结果含义

file 表示为外部命令

alias 表示该

- Ubuntu Mysql Install and CONF

gengzg

Install

http://www.navicat.com.cn/download/navicat-for-mysql

Step1: 下载Navicat ,网址:http://www.navicat.com/en/download/download.html

Step2:进入下载目录,解压压缩包:tar -zxvf navicat11_mysql_en.tar.gz

- 批处理,删除文件bat

huqiji

windowsdos

@echo off

::演示:删除指定路径下指定天数之前(以文件名中包含的日期字符串为准)的文件。

::如果演示结果无误,把del前面的echo去掉,即可实现真正删除。

::本例假设文件名中包含的日期字符串(比如:bak-2009-12-25.log)

rem 指定待删除文件的存放路径

set SrcDir=C:/Test/BatHome

rem 指定天数

set DaysAgo=1

- 跨浏览器兼容的HTML5视频音频播放器

天梯梦

html5

HTML5的video和audio标签是用来在网页中加入视频和音频的标签,在支持html5的浏览器中不需要预先加载Adobe Flash浏览器插件就能轻松快速的播放视频和音频文件。而html5media.js可以在不支持html5的浏览器上使video和audio标签生效。 How to enable <video> and <audio> tags in

- Bundle自定义数据传递

hm4123660

androidSerializable自定义数据传递BundleParcelable

我们都知道Bundle可能过put****()方法添加各种基本类型的数据,Intent也可以通过putExtras(Bundle)将数据添加进去,然后通过startActivity()跳到下一下Activity的时候就把数据也传到下一个Activity了。如传递一个字符串到下一个Activity

把数据放到Intent

- C#:异步编程和线程的使用(.NET 4.5 )

powertoolsteam

.net线程C#异步编程

异步编程和线程处理是并发或并行编程非常重要的功能特征。为了实现异步编程,可使用线程也可以不用。将异步与线程同时讲,将有助于我们更好的理解它们的特征。

本文中涉及关键知识点

1. 异步编程

2. 线程的使用

3. 基于任务的异步模式

4. 并行编程

5. 总结

异步编程

什么是异步操作?异步操作是指某些操作能够独立运行,不依赖主流程或主其他处理流程。通常情况下,C#程序

- spark 查看 job history 日志

Stark_Summer

日志sparkhistoryjob

SPARK_HOME/conf 下:

spark-defaults.conf 增加如下内容

spark.eventLog.enabled true spark.eventLog.dir hdfs://master:8020/var/log/spark spark.eventLog.compress true

spark-env.sh 增加如下内容

export SP

- SSH框架搭建

wangxiukai2015eye

springHibernatestruts

MyEclipse搭建SSH框架 Struts Spring Hibernate

1、new一个web project。

2、右键项目,为项目添加Struts支持。

选择Struts2 Core Libraries -<MyEclipes-Library>

点击Finish。src目录下多了struts