VHDL全加器设计以及ALU设计报告+(全代码)

1.四位并行加法器的逻辑实现图

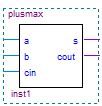

全加器设计图

(2)具体设计

architecture pluss of adder is

signal cin1 ,cin2 ,cin3 : std_logic;

component plusmax

port(

a,b,cin:in std_logic;

s,cout: out std_logic

);

end component ;

begin

G1 : plusmax port map

(cin => cinn , a=> m(0) , b => n(0), s => y(0) , cout => cin1 ) ;

G2 : plusmax port map

(cin => cin1 , a => m(1) , b => n(1), s => y(1) , cout => cin2 ) ;

G3 : plusmax port map

(cin => cin2 , a => m(2) , b => n(2), s => y(2) , cout => cin3 ) ;

G4 : plusmax port map

(cin => cin3 , a => m(3) , b => n(3), s => y(3) , cout => coutt ) ;

end pluss;

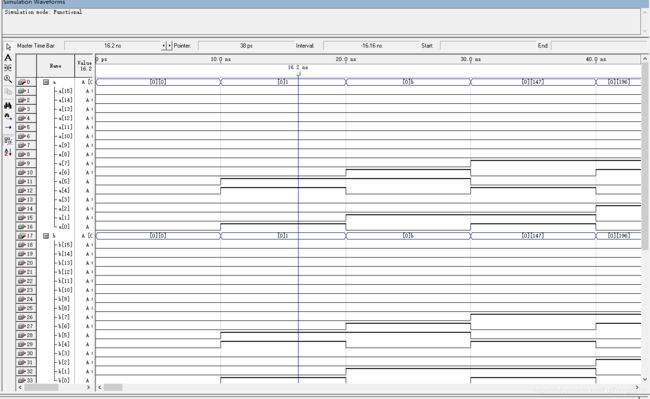

(3)测试及分析

图 3

分析如图3

当cinn = 0 ,n = “1111” ,m = “0101” 时,按正常逻辑计算,y = “0100”且 coutt = 1 图中仿真结果与理论值一样。

当cinn = 1 ,m = “0101” , n = “0000” 时 ,按正常逻辑计算,y = “0100”且 coutt = 0 图中仿真结果与理论值一样。

2.16位ALU

(1)逻辑符号

(2)具体设计

architecture aluu of adde is

signal result: std_logic_vector(16 downto 0);

begin

abc : process(se,selects,b,a,result)

begin

if(se = '1') then --1为算数运算

case selects is

when "000" => --此时为加法器

result <= ('0'&b) + ('0'&a);

cout <= result(15 downto 0);

c <= result(16);

when "001" => --此时为减法器

result <= ('0'&a) - ('0'&b) ;

cout <= result(15 downto 0);

c <= result(16);

when "010" => ----此时为加1

result <= ('0'&a) + ("000000000000001" );

cout <= result(15 downto 0);

when "011" => ----此时为减1

result <= ('0'&a) - ("000000000000001" );

cout <= result(15 downto 0);

when "100" => --此时为减2

result <= ('0'&a) - ("000000000000010" );

cout <= result(15 downto 0);

when "101" => --此时为加2

result <= ('0'&a) + ("000000000000010" );

cout <= result(15 downto 0);

when "110" => --此时为加法器减1

result <= ('0'&a) - ('0'&b) + ("000000000000001" );

cout <= result(15 downto 0);

c <= result(16);

when "111" => --此时为加法器减1

result <= ('0'&a) + ('0'&b) - ("000000000000001" );

cout <= result(15 downto 0);

c <= result(16);

end case ;

else

case selects is

when "000" => --此时为与

cout <= b and a;

when "001" => --此时为或

cout <= a or b;

when "010" => --此时为非

cout <= not a;

when "011" => --此时为与非

cout <= a nand b;

when "100" => --此时为或非

cout <= a nor b;

when "101" => --此时为同或

cout <= a xor b;

when "110" => --此时为异或

cout <= a xnor b;

when "111" =>

cout <= "ZZZZZZZZZZZZZZZZ";

end case;

end if ;

if ( result = "0000000000000000") then z <= '1';

else z <= '0';

end if;

end process;

end aluu;

(2)测试及分析

分析:当se =’1’时,为算术器,并且selects =’001’,即为算术减法器。输入a = b = 110001

运算结果为0,所以z =’0’且c = ‘0’。

- 总结与思考

1.全加器实现原理:

一位全加器(FA)的逻辑表达式为:

S=A⊕B⊕Cin;Cout=AB+BCin+ACin,其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;如果要实现多位加法可以进行级联,就是串起来使用。

比如32位+32位,就需要32个全加器;这种级联就是串行结构速度慢,如果要并行快速相加可以用超前进位加法。

如果将全加器的输入置换成A和B的组合函数Xi和Y(S0…S3控制),然后再将X,Y和进位数通过全加器进行全加,就是ALU的逻辑结构结构。即 X=f(A,B);

Y=f(A,B)不同的控制参数可以得到不同的组合函数,因而能够实现多种算术运算和逻辑运算

- 总结:更加熟练地掌握了VHDL语言中元件的定义与使用,明白了全加器工作原理,也学会了如何模拟实现。

- 全加器应用很广泛,用于诸多计算机控制。半加器、全加器是组合电路中的基本元器件,也是CPU中处理加法运算的核心。

- 详细代码请见链接