PS与PL通信概述

传统的SoPC设计无外乎两种方式:(1)在FPGA上设计一个软核,比如Altera的NIOSII,Xilinx的MicroBlaze等(2)将一个独立的FPGA和处理器芯片(比如ARM等)联合使用。第一种方式的局限在于软核的性能远远不及硬核,而且会占用大量的FPGA资源;第二种方式的局限在于如果处理器核FPGA之间需要大量数据通信的时候,两者之间的带宽往往就会成为瓶颈。而ZYNQ-7000芯片的出现,解决了这两方面的问题:一方面FPGA和ARM做在同一款芯片里面,使用的是硬核处理器,处理能力相比软核大大提升;另一方面,做在同一个芯片内,通过高速总线,解决了FPGA和ARM通信瓶颈的问题。前面的一系列文章其实已经对两者之间的通信有所涉及,但因为最近发现有很多人想对PS和PL部分的通信多了解一些,所以我决定写一篇文章,介绍一下。介绍的宗旨是全而不详,因为每一种方式都在Xilinx官方有很详细的文档,我就不做文字搬家了,只写出所有的通信方式,每一种大家可以去芯片手册或者其他相关文档查找。

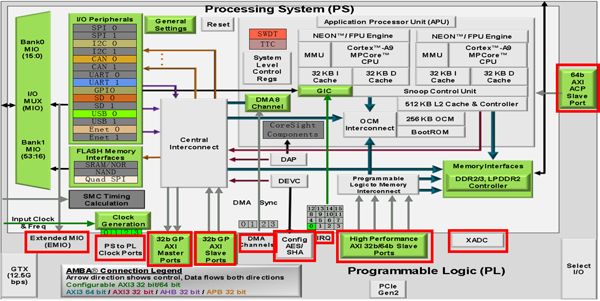

其实,PS和PL部分的通信,从ZYNQ-7000的芯片结构图上面都可以找到:

我们看上面这个图,其实横跨PS与PL两部分的都属于PS与PL的通信,只是有的带宽大,有的小。图中我用红颜色的框框出来了10个地方,这也是PS与PL的几乎所有的通信接口,还有一两个图上没有体现出来,后面会说明。下面我们分组介绍一下。

方式一:总线级别的接口

前面的文章《ZYNQ-7000使用总结(6)——AXI接口简述》已经简单介绍过AXI总线,而PL与PL部分通信所使用的总线就是AXI总线。从图中可以看出总共有4种9条:2条32位Master总线接口,2条32位的Slave总线接口,4条32位/64位可配置的高性能Slave接口,1条64位的Slave ACP接口。下面我们分别做一下介绍。

32b GP AXI Master/Slave Ports

首先我们可以看到这两种总线都是通过Central Interconnect连接到IO Peripheral(IOP)那边去的;其次,我们需要知道里面的GP就是General Purpose的意思;最后,这两类线都是32位的。结合这些,我们就可以了解到这两类线都是AXI中速度相对比较低的总线,主要用于PL与PS中的IOP的通信。

High Performance AXI 32b/64b Slave Ports

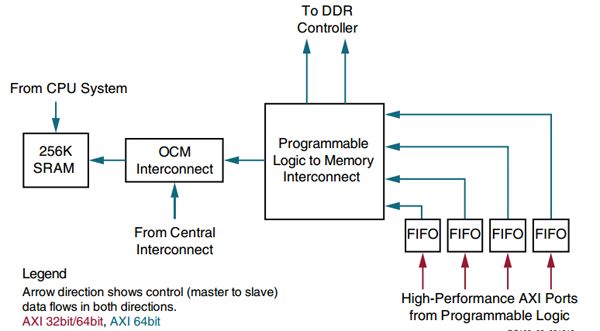

这个总线的信息基本在名字里面体现的差不多了:高性能、32位/64位可配置、Slave是它最主要的三个特点。然后我们来看一看这高性能的线到底是干嘛的。首先我们看一下它的结构图:

我们可以看到PL是通过4个FIFO控制器连接到了Memory Interconnect,其中两条连到了DDR控制器,一条连接到到了一个双端口的OCM Interconnect。而我们知道DDR和OCM都属于高速设备,所以这也就是为什么这里要用这种高性能总线的原因。所以,这个总线主要是用于大吞吐量数据的传输,而且用户还可以做一定的配置。而且该总线(每条)还具有如下一些特性:

. PL与PS部分内存传输延迟低

. 有1KB 深度的FIFO

. 32位/64位可配置

. 支持高达32字(word)长的读缓冲

. 在读的时候可是释放对数据的控制以更加高效的利用AXI Interconnect带宽

. 支持多个对DDR和OCM的控制命令

64b AXI ACP Slave Port

这个也是64位的,和前面的相比,多了一个ACP,而这个ACP的全称是Accelerator Coherency Port,一般翻译为“加速一致性接口”。我们从图中可以看到,它是连接到了CPU的Snoop Control Unit(SCU),这个一般翻译为侦测控制单元。他的作用就是保证两个处理器核对共享的缓存操作的数据保持一致性(好像有点拗口),因为我们看到两个A9核共享的是同一个二级缓存,那么可能就会出现一个改变了缓存内容,另外一个不知道的情况,而这个SCU就是“监视”这个共享区域的,一旦它发生了变化,便会通知另外一个处理器核,通过这样的机制,便实现了前面所谓的“一致性”。所以,这个接口也是高速的,不过它和前面的总线相比,还会多一个ACP的功能。

好了,总线级别的接口就介绍完了,总共四种九条。

方式二:EMIO

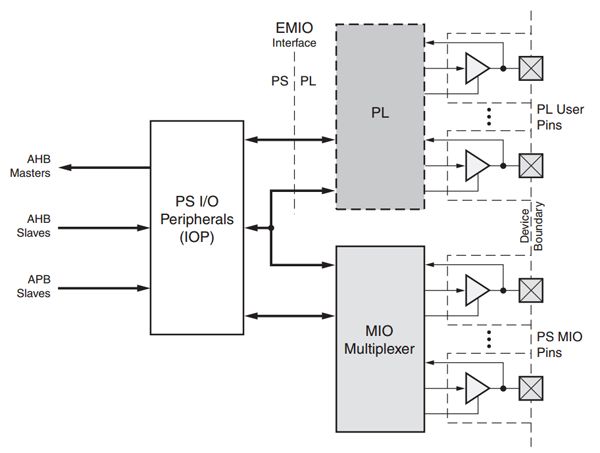

EMIO是ZYNQ-7000中的一个新概念,全称是Extendable MIO,即可扩展的MIO。而MIO全称Multiplexed IO,也就是复用IO。我们从Xilinx的一些资料可以得知MIO的数量有限,而且已经将其地址分配给了PS部分已有的一些外设资源,这个分配工作由软件去做。而这个EMIO就是用来对有限的MIO做扩展的。通过它我们可以从PL部分访问PS部分还没有映射地址的外设。下面是一张图:

所以,除了32b AXI GP Master/Slave以外,EMIO也是我们从PL部分访问PS部分IOP的一个途径,不过相比总线,EMIO的速度会慢一点,但是它的灵活性却会更高一些。更多关于MIO和EMIO的资料可参考UG585文档以及其他相关文档去了解。

方式三:其他

这里把剩下的放在一起做一下很简单的介绍。主要原因是前面的两种方式主要在PS和PL的通信中起数据传输作用,而且一般量会比较大。而其他的就主要就是一些信号,功能为主,数据传输只是实现功能的一个方式,一般量也比较小,比如像时钟呀,DMA之类的,不像前面的,主要就是做一个简单的数据传输。下面简单列举出来:

DMA、中断、事件信号

. 用于传输事件信号的处理器总线

. PL部分的外设IP传给PS部分中断控制器(GIC)信号线路

. 给PL部分使用的4通道DMA信号

. 异步触发信号

时钟和复位

. PS部分输出的4个时钟信号(供PL部分使用)

. PS部分输出的4个复位信号(供PL部分使用)

配置及其他信息

. 前面的文章已经讲过ZYNQ的PL部分也是由PS部分做的,所以PS与PL之间也会存在配置的一些通路

. 上面的图中还有XADC通信方式(XADC就是Xilinx的AD转换:Xilinx AD Converter)

. Config AES/SHA。这个是板子上的一些加密配置,AES和SHA都是目前国际上标准的加密/认证标准。

. 还有图中未画出的JTAG接口

总结

至此,Xilinx ZYNQ-7000的PS(Processing System,即ARM处理器部分)和PL(Programmable Logic,即FPGA部分)的通信就介绍完了,里面也对涉及的属于概念作了一下简单介绍。对于每种通信方式的细节没有做很深入的介绍,大家如果想了解可以去查找对应的文档。