小数分频N.5分频

小数分频N.5分频

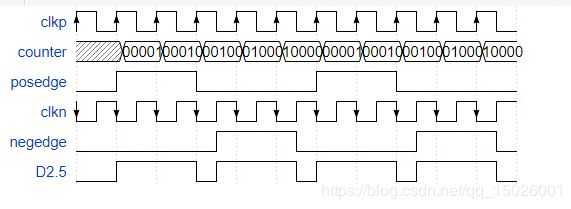

- 2.5分频波形图

- 原理分析

- verilog code

- testbench

- 仿真结果

博主之前写过三分频,今天有空补充一下小数分频,原理大同小异,具体可以参考博主之前的博客三分频

2.5分频波形图

{signal: [

{name: ‘clkp’, wave: ‘P…’},

{name: ‘counter’, wave: ‘x2222222222’, data: [‘00001’, ‘00010’, ‘00100’, ‘01000’,‘10000’,‘00001’, ‘00010’, ‘00100’, ‘01000’,‘10000’]},

{name: ‘posedge’, wave: ‘0h.l…h.l…’},

{name: ‘clkn’, wave: ‘N…’},

{name: ‘negedge’, wave: ‘l…nhpl.nhp’},

{name: ‘D2.5’, wave: ‘lh.nhph.nhp’}

]}

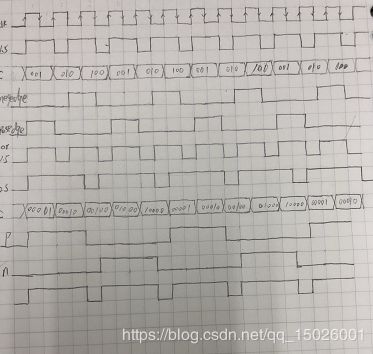

原理分析

上图是博主分析小数分频时所画的时序图,分别为1.5 以及2.5 分频,总结就是在进行N.5分频是shiftcount需要2N位 分别采用上升沿与下降沿进行采样,其中采样的高电平时间为N,最后将二者的结果进行或运算。

verilog code

module D2div5(

input clk,

input reset,

output D2div5,

output [4:0] count,

output clkN,

output clkP

);

reg [4:0] count;

wire [4:0]shiftcount;

reg clkP,clkN;

assign shiftcount = 5'b00001;

always @ (posedge clk ,negedge reset)

if(!reset)

count <= shiftcount;

else

count <= {count[3:0],count[4]};

always @ (negedge clk or negedge reset)

if(!reset)

clkN <= 1'b0;

else if(count == 5'b01000 || count == 5'b10000)

clkN <= 1'b1;

else clkN <= 1'b0;

always @ (posedge clk or negedge reset)

if(!reset)

clkP <= 1'b0;

else if(count == 5'b00001 || count == 5'b00010)

clkP <= 1'b1;

else clkP <= 1'b0;

assign D2div5 = clkP | clkN;

testbench

// Code your testbench here

// or browse Examples

module txt();

reg clk;

reg reset;

wire D2div5;

wire [4:0] count;

wire clkN;

wire clkP;

initial

begin

$dumpfile("d.vcd");

$dumpvars(1);

clk = 0;

reset =0;

#10

reset =1;

end

always # 10 clk = ~clk;

D2div5 D2div5_inst(

.clk,

.reset,

.D2div5,

.count,

.clkN,

.clkP

);

endmodule

endmodule