ART世界探险(17) - 中层中间代码MIR

Dalvik字节码的指令格式

指令格式分类

Dalvik指令,根据需要的寄存器数目的不同,长度也有所不同。

如下面的结构所示,有下面的这些情况:

enum Format {

k10x, // op

k12x, // op vA, vB

k11n, // op vA, #+B

k11x, // op vAA

k10t, // op +AA

k20t, // op +AAAA

k22x, // op vAA, vBBBB

k21t, // op vAA, +BBBB

k21s, // op vAA, #+BBBB

k21h, // op vAA, #+BBBB00000[00000000]

k21c, // op vAA, thing@BBBB

k23x, // op vAA, vBB, vCC

k22b, // op vAA, vBB, #+CC

k22t, // op vA, vB, +CCCC

k22s, // op vA, vB, #+CCCC

k22c, // op vA, vB, thing@CCCC

k32x, // op vAAAA, vBBBB

k30t, // op +AAAAAAAA

k31t, // op vAA, +BBBBBBBB

k31i, // op vAA, #+BBBBBBBB

k31c, // op vAA, thing@BBBBBBBB

k35c, // op {vC, vD, vE, vF, vG}, thing@BBBB (B: count, A: vG)

k3rc, // op {vCCCC .. v(CCCC+AA-1)}, meth@BBBB

k51l, // op vAA, #+BBBBBBBBBBBBBBBB

};

计算指令格式长度

MIRGraph的ParseInsn方法就是用来计算指令长度的。

/*

* Parse an instruction, return the length of the instruction

*/

int MIRGraph::ParseInsn(const uint16_t* code_ptr, MIR::DecodedInstruction* decoded_instruction) {

const Instruction* inst = Instruction::At(code_ptr);

decoded_instruction->opcode = inst->Opcode();

decoded_instruction->vA = inst->HasVRegA() ? inst->VRegA() : 0;

decoded_instruction->vB = inst->HasVRegB() ? inst->VRegB() : 0;

decoded_instruction->vB_wide = inst->HasWideVRegB() ? inst->WideVRegB() : 0;

decoded_instruction->vC = inst->HasVRegC() ? inst->VRegC() : 0;

if (inst->HasVarArgs()) {

inst->GetVarArgs(decoded_instruction->arg);

}

return inst->SizeInCodeUnits();

}

MIR中使用的Dalvik指令集

我们之前用了8讲的内容专门讲指令。

下面我们将这些指令的中间细节列一下,大家从下面的表中可以查到每一条指令的格式。

const uint64_t MIRGraph::oat_data_flow_attributes_[kMirOpLast] = {

// 00 NOP

DF_NOP,

// 01 MOVE vA, vB

DF_DA | DF_UB | DF_IS_MOVE,

// 02 MOVE_FROM16 vAA, vBBBB

DF_DA | DF_UB | DF_IS_MOVE,

// 03 MOVE_16 vAAAA, vBBBB

DF_DA | DF_UB | DF_IS_MOVE,

// 04 MOVE_WIDE vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_IS_MOVE,

// 05 MOVE_WIDE_FROM16 vAA, vBBBB

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_IS_MOVE,

// 06 MOVE_WIDE_16 vAAAA, vBBBB

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_IS_MOVE,

// 07 MOVE_OBJECT vA, vB

DF_DA | DF_UB | DF_NULL_TRANSFER_0 | DF_IS_MOVE | DF_REF_A | DF_REF_B,

// 08 MOVE_OBJECT_FROM16 vAA, vBBBB

DF_DA | DF_UB | DF_NULL_TRANSFER_0 | DF_IS_MOVE | DF_REF_A | DF_REF_B,

// 09 MOVE_OBJECT_16 vAAAA, vBBBB

DF_DA | DF_UB | DF_NULL_TRANSFER_0 | DF_IS_MOVE | DF_REF_A | DF_REF_B,

// 0A MOVE_RESULT vAA

DF_DA,

// 0B MOVE_RESULT_WIDE vAA

DF_DA | DF_A_WIDE,

// 0C MOVE_RESULT_OBJECT vAA

DF_DA | DF_REF_A,

// 0D MOVE_EXCEPTION vAA

DF_DA | DF_REF_A | DF_NON_NULL_DST,

// 0E RETURN_VOID

DF_NOP,

// 0F RETURN vAA

DF_UA,

// 10 RETURN_WIDE vAA

DF_UA | DF_A_WIDE,

// 11 RETURN_OBJECT vAA

DF_UA | DF_REF_A,

// 12 CONST_4 vA, #+B

DF_DA | DF_SETS_CONST,

// 13 CONST_16 vAA, #+BBBB

DF_DA | DF_SETS_CONST,

// 14 CONST vAA, #+BBBBBBBB

DF_DA | DF_SETS_CONST,

// 15 CONST_HIGH16 VAA, #+BBBB0000

DF_DA | DF_SETS_CONST,

// 16 CONST_WIDE_16 vAA, #+BBBB

DF_DA | DF_A_WIDE | DF_SETS_CONST,

// 17 CONST_WIDE_32 vAA, #+BBBBBBBB

DF_DA | DF_A_WIDE | DF_SETS_CONST,

// 18 CONST_WIDE vAA, #+BBBBBBBBBBBBBBBB

DF_DA | DF_A_WIDE | DF_SETS_CONST,

// 19 CONST_WIDE_HIGH16 vAA, #+BBBB000000000000

DF_DA | DF_A_WIDE | DF_SETS_CONST,

// 1A CONST_STRING vAA, string@BBBB

DF_DA | DF_REF_A | DF_NON_NULL_DST,

// 1B CONST_STRING_JUMBO vAA, string@BBBBBBBB

DF_DA | DF_REF_A | DF_NON_NULL_DST,

// 1C CONST_CLASS vAA, type@BBBB

DF_DA | DF_REF_A | DF_NON_NULL_DST,

// 1D MONITOR_ENTER vAA

DF_UA | DF_NULL_CHK_A | DF_REF_A,

// 1E MONITOR_EXIT vAA

DF_UA | DF_NULL_CHK_A | DF_REF_A,

// 1F CHK_CAST vAA, type@BBBB

DF_UA | DF_REF_A | DF_CHK_CAST | DF_UMS,

// 20 INSTANCE_OF vA, vB, type@CCCC

DF_DA | DF_UB | DF_CORE_A | DF_REF_B | DF_UMS,

// 21 ARRAY_LENGTH vA, vB

DF_DA | DF_UB | DF_NULL_CHK_B | DF_CORE_A | DF_REF_B,

// 22 NEW_INSTANCE vAA, type@BBBB

DF_DA | DF_NON_NULL_DST | DF_REF_A | DF_UMS,

// 23 NEW_ARRAY vA, vB, type@CCCC

DF_DA | DF_UB | DF_NON_NULL_DST | DF_REF_A | DF_CORE_B | DF_UMS,

// 24 FILLED_NEW_ARRAY {vD, vE, vF, vG, vA}

DF_FORMAT_35C | DF_NON_NULL_RET | DF_UMS,

// 25 FILLED_NEW_ARRAY_RANGE {vCCCC .. vNNNN}, type@BBBB

DF_FORMAT_3RC | DF_NON_NULL_RET | DF_UMS,

// 26 FILL_ARRAY_DATA vAA, +BBBBBBBB

DF_UA | DF_REF_A | DF_UMS,

// 27 THROW vAA

DF_UA | DF_REF_A | DF_UMS,

// 28 GOTO

DF_NOP,

// 29 GOTO_16

DF_NOP,

// 2A GOTO_32

DF_NOP,

// 2B PACKED_SWITCH vAA, +BBBBBBBB

DF_UA | DF_CORE_A,

// 2C SPARSE_SWITCH vAA, +BBBBBBBB

DF_UA | DF_CORE_A,

// 2D CMPL_FLOAT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_FP_B | DF_FP_C | DF_CORE_A,

// 2E CMPG_FLOAT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_FP_B | DF_FP_C | DF_CORE_A,

// 2F CMPL_DOUBLE vAA, vBB, vCC

DF_DA | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_FP_B | DF_FP_C | DF_CORE_A,

// 30 CMPG_DOUBLE vAA, vBB, vCC

DF_DA | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_FP_B | DF_FP_C | DF_CORE_A,

// 31 CMP_LONG vAA, vBB, vCC

DF_DA | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 32 IF_EQ vA, vB, +CCCC

DF_UA | DF_UB | DF_SAME_TYPE_AB,

// 33 IF_NE vA, vB, +CCCC

DF_UA | DF_UB | DF_SAME_TYPE_AB,

// 34 IF_LT vA, vB, +CCCC

DF_UA | DF_UB | DF_SAME_TYPE_AB,

// 35 IF_GE vA, vB, +CCCC

DF_UA | DF_UB | DF_SAME_TYPE_AB,

// 36 IF_GT vA, vB, +CCCC

DF_UA | DF_UB | DF_SAME_TYPE_AB,

// 37 IF_LE vA, vB, +CCCC

DF_UA | DF_UB | DF_SAME_TYPE_AB,

// 38 IF_EQZ vAA, +BBBB

DF_UA,

// 39 IF_NEZ vAA, +BBBB

DF_UA,

// 3A IF_LTZ vAA, +BBBB

DF_UA,

// 3B IF_GEZ vAA, +BBBB

DF_UA,

// 3C IF_GTZ vAA, +BBBB

DF_UA,

// 3D IF_LEZ vAA, +BBBB

DF_UA,

// 3E UNUSED_3E

DF_NOP,

// 3F UNUSED_3F

DF_NOP,

// 40 UNUSED_40

DF_NOP,

// 41 UNUSED_41

DF_NOP,

// 42 UNUSED_42

DF_NOP,

// 43 UNUSED_43

DF_NOP,

// 44 AGET vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 45 AGET_WIDE vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 46 AGET_OBJECT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_A | DF_REF_B | DF_CORE_C | DF_LVN,

// 47 AGET_BOOLEAN vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 48 AGET_BYTE vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 49 AGET_CHAR vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 4A AGET_SHORT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 4B APUT vAA, vBB, vCC

DF_UA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 4C APUT_WIDE vAA, vBB, vCC

DF_UA | DF_A_WIDE | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 4D APUT_OBJECT vAA, vBB, vCC

DF_UA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_A | DF_REF_B | DF_CORE_C | DF_LVN,

// 4E APUT_BOOLEAN vAA, vBB, vCC

DF_UA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 4F APUT_BYTE vAA, vBB, vCC

DF_UA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 50 APUT_CHAR vAA, vBB, vCC

DF_UA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 51 APUT_SHORT vAA, vBB, vCC

DF_UA | DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 52 IGET vA, vB, field@CCCC

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 53 IGET_WIDE vA, vB, field@CCCC

DF_DA | DF_A_WIDE | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 54 IGET_OBJECT vA, vB, field@CCCC

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_A | DF_REF_B | DF_IFIELD | DF_LVN,

// 55 IGET_BOOLEAN vA, vB, field@CCCC

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 56 IGET_BYTE vA, vB, field@CCCC

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 57 IGET_CHAR vA, vB, field@CCCC

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 58 IGET_SHORT vA, vB, field@CCCC

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 59 IPUT vA, vB, field@CCCC

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 5A IPUT_WIDE vA, vB, field@CCCC

DF_UA | DF_A_WIDE | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 5B IPUT_OBJECT vA, vB, field@CCCC

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_A | DF_REF_B | DF_IFIELD | DF_LVN,

// 5C IPUT_BOOLEAN vA, vB, field@CCCC

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 5D IPUT_BYTE vA, vB, field@CCCC

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 5E IPUT_CHAR vA, vB, field@CCCC

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 5F IPUT_SHORT vA, vB, field@CCCC

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// 60 SGET vAA, field@BBBB

DF_DA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 61 SGET_WIDE vAA, field@BBBB

DF_DA | DF_A_WIDE | DF_SFIELD | DF_CLINIT | DF_UMS,

// 62 SGET_OBJECT vAA, field@BBBB

DF_DA | DF_REF_A | DF_SFIELD | DF_CLINIT | DF_UMS,

// 63 SGET_BOOLEAN vAA, field@BBBB

DF_DA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 64 SGET_BYTE vAA, field@BBBB

DF_DA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 65 SGET_CHAR vAA, field@BBBB

DF_DA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 66 SGET_SHORT vAA, field@BBBB

DF_DA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 67 SPUT vAA, field@BBBB

DF_UA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 68 SPUT_WIDE vAA, field@BBBB

DF_UA | DF_A_WIDE | DF_SFIELD | DF_CLINIT | DF_UMS,

// 69 SPUT_OBJECT vAA, field@BBBB

DF_UA | DF_REF_A | DF_SFIELD | DF_CLINIT | DF_UMS,

// 6A SPUT_BOOLEAN vAA, field@BBBB

DF_UA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 6B SPUT_BYTE vAA, field@BBBB

DF_UA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 6C SPUT_CHAR vAA, field@BBBB

DF_UA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 6D SPUT_SHORT vAA, field@BBBB

DF_UA | DF_SFIELD | DF_CLINIT | DF_UMS,

// 6E INVOKE_VIRTUAL {vD, vE, vF, vG, vA}

DF_FORMAT_35C | DF_NULL_CHK_OUT0 | DF_UMS,

// 6F INVOKE_SUPER {vD, vE, vF, vG, vA}

DF_FORMAT_35C | DF_NULL_CHK_OUT0 | DF_UMS,

// 70 INVOKE_DIRECT {vD, vE, vF, vG, vA}

DF_FORMAT_35C | DF_NULL_CHK_OUT0 | DF_UMS,

// 71 INVOKE_STATIC {vD, vE, vF, vG, vA}

DF_FORMAT_35C | DF_CLINIT | DF_UMS,

// 72 INVOKE_INTERFACE {vD, vE, vF, vG, vA}

DF_FORMAT_35C | DF_NULL_CHK_OUT0 | DF_UMS,

// 73 RETURN_VOID_NO_BARRIER

DF_NOP,

// 74 INVOKE_VIRTUAL_RANGE {vCCCC .. vNNNN}

DF_FORMAT_3RC | DF_NULL_CHK_OUT0 | DF_UMS,

// 75 INVOKE_SUPER_RANGE {vCCCC .. vNNNN}

DF_FORMAT_3RC | DF_NULL_CHK_OUT0 | DF_UMS,

// 76 INVOKE_DIRECT_RANGE {vCCCC .. vNNNN}

DF_FORMAT_3RC | DF_NULL_CHK_OUT0 | DF_UMS,

// 77 INVOKE_STATIC_RANGE {vCCCC .. vNNNN}

DF_FORMAT_3RC | DF_CLINIT | DF_UMS,

// 78 INVOKE_INTERFACE_RANGE {vCCCC .. vNNNN}

DF_FORMAT_3RC | DF_NULL_CHK_OUT0 | DF_UMS,

// 79 UNUSED_79

DF_NOP,

// 7A UNUSED_7A

DF_NOP,

// 7B NEG_INT vA, vB

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// 7C NOT_INT vA, vB

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// 7D NEG_LONG vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// 7E NOT_LONG vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// 7F NEG_FLOAT vA, vB

DF_DA | DF_UB | DF_FP_A | DF_FP_B,

// 80 NEG_DOUBLE vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// 81 INT_TO_LONG vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_CORE_A | DF_CORE_B,

// 82 INT_TO_FLOAT vA, vB

DF_DA | DF_UB | DF_FP_A | DF_CORE_B,

// 83 INT_TO_DOUBLE vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_FP_A | DF_CORE_B,

// 84 LONG_TO_INT vA, vB

DF_DA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// 85 LONG_TO_FLOAT vA, vB

DF_DA | DF_UB | DF_B_WIDE | DF_FP_A | DF_CORE_B,

// 86 LONG_TO_DOUBLE vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_FP_A | DF_CORE_B,

// 87 FLOAT_TO_INT vA, vB

DF_DA | DF_UB | DF_FP_B | DF_CORE_A,

// 88 FLOAT_TO_LONG vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_FP_B | DF_CORE_A,

// 89 FLOAT_TO_DOUBLE vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_FP_A | DF_FP_B,

// 8A DOUBLE_TO_INT vA, vB

DF_DA | DF_UB | DF_B_WIDE | DF_FP_B | DF_CORE_A,

// 8B DOUBLE_TO_LONG vA, vB

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_FP_B | DF_CORE_A,

// 8C DOUBLE_TO_FLOAT vA, vB

DF_DA | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// 8D INT_TO_BYTE vA, vB

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// 8E INT_TO_CHAR vA, vB

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// 8F INT_TO_SHORT vA, vB

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// 90 ADD_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 91 SUB_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 92 MUL_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 93 DIV_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 94 REM_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 95 AND_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 96 OR_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 97 XOR_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 98 SHL_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 99 SHR_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 9A USHR_INT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 9B ADD_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 9C SUB_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 9D MUL_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 9E DIV_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// 9F REM_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// A0 AND_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// A1 OR_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// A2 XOR_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// A3 SHL_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// A4 SHR_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// A5 USHR_LONG vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_CORE_A | DF_CORE_B | DF_CORE_C,

// A6 ADD_FLOAT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_FP_A | DF_FP_B | DF_FP_C,

// A7 SUB_FLOAT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_FP_A | DF_FP_B | DF_FP_C,

// A8 MUL_FLOAT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_FP_A | DF_FP_B | DF_FP_C,

// A9 DIV_FLOAT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_FP_A | DF_FP_B | DF_FP_C,

// AA REM_FLOAT vAA, vBB, vCC

DF_DA | DF_UB | DF_UC | DF_FP_A | DF_FP_B | DF_FP_C,

// AB ADD_DOUBLE vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_FP_A | DF_FP_B | DF_FP_C,

// AC SUB_DOUBLE vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_FP_A | DF_FP_B | DF_FP_C,

// AD MUL_DOUBLE vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_FP_A | DF_FP_B | DF_FP_C,

// AE DIV_DOUBLE vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_FP_A | DF_FP_B | DF_FP_C,

// AF REM_DOUBLE vAA, vBB, vCC

DF_DA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_UC | DF_C_WIDE | DF_FP_A | DF_FP_B | DF_FP_C,

// B0 ADD_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B1 SUB_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B2 MUL_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B3 DIV_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B4 REM_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B5 AND_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B6 OR_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B7 XOR_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B8 SHL_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// B9 SHR_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// BA USHR_INT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// BB ADD_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// BC SUB_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// BD MUL_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// BE DIV_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// BF REM_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// C0 AND_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// C1 OR_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// C2 XOR_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// C3 SHL_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// C4 SHR_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// C5 USHR_LONG_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_CORE_A | DF_CORE_B,

// C6 ADD_FLOAT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_FP_A | DF_FP_B,

// C7 SUB_FLOAT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_FP_A | DF_FP_B,

// C8 MUL_FLOAT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_FP_A | DF_FP_B,

// C9 DIV_FLOAT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_FP_A | DF_FP_B,

// CA REM_FLOAT_2ADDR vA, vB

DF_DA | DF_UA | DF_UB | DF_FP_A | DF_FP_B,

// CB ADD_DOUBLE_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// CC SUB_DOUBLE_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// CD MUL_DOUBLE_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// CE DIV_DOUBLE_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// CF REM_DOUBLE_2ADDR vA, vB

DF_DA | DF_A_WIDE | DF_UA | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// D0 ADD_INT_LIT16 vA, vB, #+CCCC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D1 RSUB_INT vA, vB, #+CCCC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D2 MUL_INT_LIT16 vA, vB, #+CCCC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D3 DIV_INT_LIT16 vA, vB, #+CCCC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D4 REM_INT_LIT16 vA, vB, #+CCCC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D5 AND_INT_LIT16 vA, vB, #+CCCC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D6 OR_INT_LIT16 vA, vB, #+CCCC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D7 XOR_INT_LIT16 vA, vB, #+CCCC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D8 ADD_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// D9 RSUB_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// DA MUL_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// DB DIV_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// DC REM_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// DD AND_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// DE OR_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// DF XOR_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// E0 SHL_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// E1 SHR_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// E2 USHR_INT_LIT8 vAA, vBB, #+CC

DF_DA | DF_UB | DF_CORE_A | DF_CORE_B,

// E3 IGET_QUICK

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// E4 IGET_WIDE_QUICK

DF_DA | DF_A_WIDE | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// E5 IGET_OBJECT_QUICK

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_A | DF_REF_B | DF_IFIELD | DF_LVN,

// E6 IPUT_QUICK

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// E7 IPUT_WIDE_QUICK

DF_UA | DF_A_WIDE | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// E8 IPUT_OBJECT_QUICK

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_A | DF_REF_B | DF_IFIELD | DF_LVN,

// E9 INVOKE_VIRTUAL_QUICK

DF_FORMAT_35C | DF_NULL_CHK_OUT0 | DF_UMS,

// EA INVOKE_VIRTUAL_RANGE_QUICK

DF_FORMAT_3RC | DF_NULL_CHK_OUT0 | DF_UMS,

// EB IPUT_BOOLEAN_QUICK vA, vB, index

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// EC IPUT_BYTE_QUICK vA, vB, index

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// ED IPUT_CHAR_QUICK vA, vB, index

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// EE IPUT_SHORT_QUICK vA, vB, index

DF_UA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// EF IGET_BOOLEAN_QUICK vA, vB, index

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// F0 IGET_BYTE_QUICK vA, vB, index

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// F1 IGET_CHAR_QUICK vA, vB, index

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// F2 IGET_SHORT_QUICK vA, vB, index

DF_DA | DF_UB | DF_NULL_CHK_B | DF_REF_B | DF_IFIELD | DF_LVN,

// F3 UNUSED_F3

DF_NOP,

// F4 UNUSED_F4

DF_NOP,

// F5 UNUSED_F5

DF_NOP,

// F6 UNUSED_F6

DF_NOP,

// F7 UNUSED_F7

DF_NOP,

// F8 UNUSED_F8

DF_NOP,

// F9 UNUSED_F9

DF_NOP,

// FA UNUSED_FA

DF_NOP,

// FB UNUSED_FB

DF_NOP,

// FC UNUSED_FC

DF_NOP,

// FD UNUSED_FD

DF_NOP,

// FE UNUSED_FE

DF_NOP,

// FF UNUSED_FF

DF_NOP,

// Beginning of extended MIR opcodes

// 100 MIR_PHI

DF_DA | DF_NULL_TRANSFER_N,

// 101 MIR_COPY

DF_DA | DF_UB | DF_IS_MOVE,

// 102 MIR_FUSED_CMPL_FLOAT

DF_UA | DF_UB | DF_FP_A | DF_FP_B,

// 103 MIR_FUSED_CMPG_FLOAT

DF_UA | DF_UB | DF_FP_A | DF_FP_B,

// 104 MIR_FUSED_CMPL_DOUBLE

DF_UA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// 105 MIR_FUSED_CMPG_DOUBLE

DF_UA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_FP_A | DF_FP_B,

// 106 MIR_FUSED_CMP_LONG

DF_UA | DF_A_WIDE | DF_UB | DF_B_WIDE | DF_CORE_A | DF_CORE_B,

// 107 MIR_NOP

DF_NOP,

// 108 MIR_NULL_CHECK

DF_UA | DF_REF_A | DF_NULL_CHK_A | DF_LVN,

// 109 MIR_RANGE_CHECK

0,

// 10A MIR_DIV_ZERO_CHECK

0,

// 10B MIR_CHECK

0,

// 10D MIR_SELECT

DF_DA | DF_UB,

// 10E MirOpConstVector

0,

// 10F MirOpMoveVector

0,

// 110 MirOpPackedMultiply

0,

// 111 MirOpPackedAddition

0,

// 112 MirOpPackedSubtract

0,

// 113 MirOpPackedShiftLeft

0,

// 114 MirOpPackedSignedShiftRight

0,

// 115 MirOpPackedUnsignedShiftRight

0,

// 116 MirOpPackedAnd

0,

// 117 MirOpPackedOr

0,

// 118 MirOpPackedXor

0,

// 119 MirOpPackedAddReduce

DF_FORMAT_EXTENDED,

// 11A MirOpPackedReduce

DF_FORMAT_EXTENDED,

// 11B MirOpPackedSet

DF_FORMAT_EXTENDED,

// 11C MirOpReserveVectorRegisters

0,

// 11D MirOpReturnVectorRegisters

0,

// 11E MirOpMemBarrier

0,

// 11F MirOpPackedArrayGet

DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 120 MirOpPackedArrayPut

DF_UB | DF_UC | DF_NULL_CHK_B | DF_RANGE_CHK_C | DF_REF_B | DF_CORE_C | DF_LVN,

// 121 MirOpMaddInt

DF_FORMAT_EXTENDED,

// 122 MirOpMsubInt

DF_FORMAT_EXTENDED,

// 123 MirOpMaddLong

DF_FORMAT_EXTENDED,

// 124 MirOpMsubLong

DF_FORMAT_EXTENDED,

};

MIR

生成一条MIR

// Allocate a new MIR.

MIR* MIRGraph::NewMIR() {

MIR* mir = new (arena_) MIR();

return mir;

}

代码块 - BasicBlock

我们都知道,Java中的代码是由一个个代码块所组成的。

代码块的类型 - BBType

enum BBType {

kNullBlock,

kEntryBlock,

kDalvikByteCode,

kExitBlock,

kExceptionHandling,

kDead,

};

代码块列表类型

enum BlockListType {

kNotUsed = 0,

kCatch,

kPackedSwitch,

kSparseSwitch,

};

基本块的数据流

// Dataflow attributes of a basic block.

struct BasicBlockDataFlow {

ArenaBitVector* use_v;

ArenaBitVector* def_v;

ArenaBitVector* live_in_v;

int32_t* vreg_to_ssa_map_exit;

};

基本代码块的创建 - CreateNewBB方法

- 首先根据block_list_中已有的基本代码块的数目生成新的BasicBlockId。

- 然后调用NewMemBB去真正分配空间。

- 生成之后,再压到block_list_向量中。

BasicBlock* MIRGraph::CreateNewBB(BBType block_type) {

BasicBlockId id = static_cast(block_list_.size());

BasicBlock* res = NewMemBB(block_type, id);

block_list_.push_back(res);

return res;

}

分配一个基本代码块

主要是预留出相应的空间来。

另外还要到block_id_map_中备个案。

// Allocate a new basic block.

BasicBlock* MIRGraph::NewMemBB(BBType block_type, int block_id) {

BasicBlock* bb = new (arena_) BasicBlock(block_id, block_type, arena_);

// TUNING: better estimate of the exit block predecessors?

bb->predecessors.reserve((block_type == kExitBlock) ? 2048 : 2);

block_id_map_.Put(block_id, block_id);

return bb;

}

代码项

Dex文件中的代码项,用CodeItem结构体来表示:

struct CodeItem {

uint16_t registers_size_;

uint16_t ins_size_;

uint16_t outs_size_;

uint16_t tries_size_;

uint32_t debug_info_off_; // file offset to debug info stream

uint32_t insns_size_in_code_units_; // size of the insns array, in 2 byte code units

uint16_t insns_[1];

private:

DISALLOW_COPY_AND_ASSIGN(CodeItem);

};

调用类型

调用方法的类型有以下几种:

- kStatic:调用静态方法

- kDirect:调用普通方法

- kVirtual:调用虚方法

- kSuper:调用父类方法

- kInterface:调用实现的接口中的方法

enum InvokeType {

kStatic, // <>

kDirect, // <>

kVirtual, // <>

kSuper, // <>

kInterface, // <>

kMaxInvokeType = kInterface

};

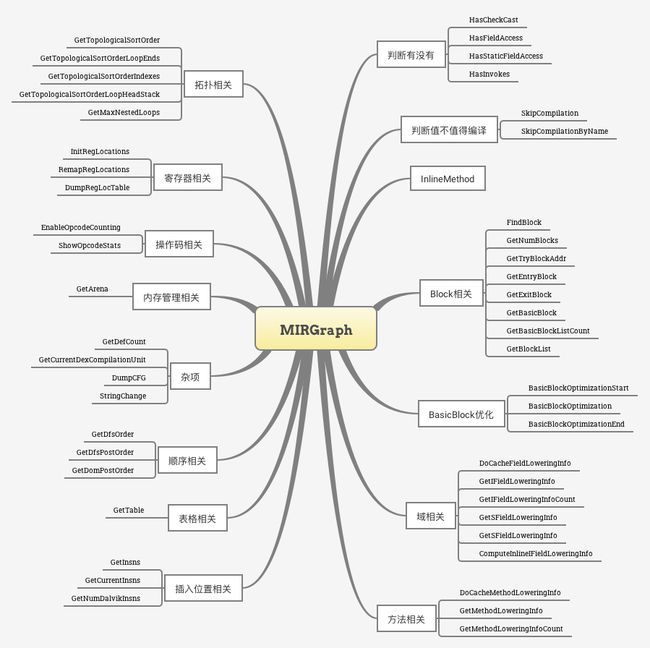

最后,我们上一张MIRGraph的大图. 后面几节我们主要都是跟它打交道了