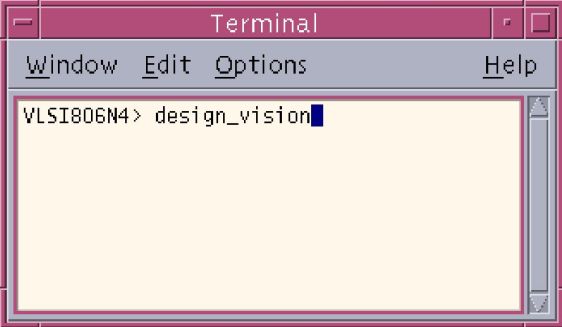

1、软件启动

新开一个terminal窗口,输入命令 :design_vision,回车即可开启图形界面,进入图形界面后可通

过菜单、对话框等来实现DC的功能,相关的命令操作同样可以使用。

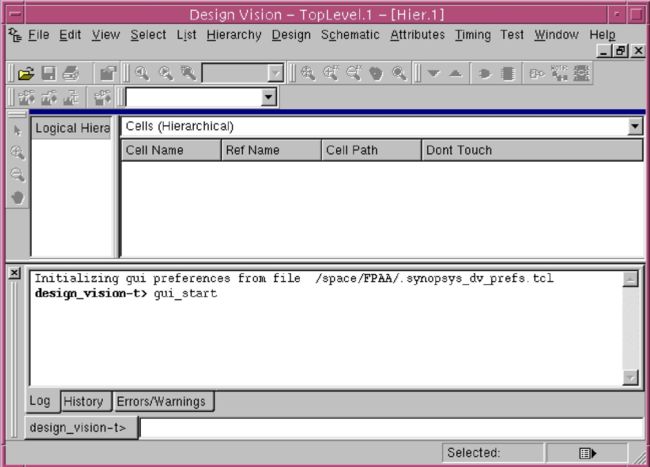

2、指定相关库文件及路径

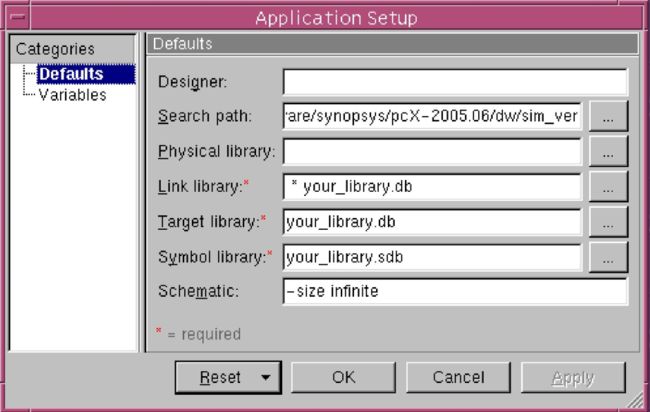

“File > Setup”打开下图所示对话框:

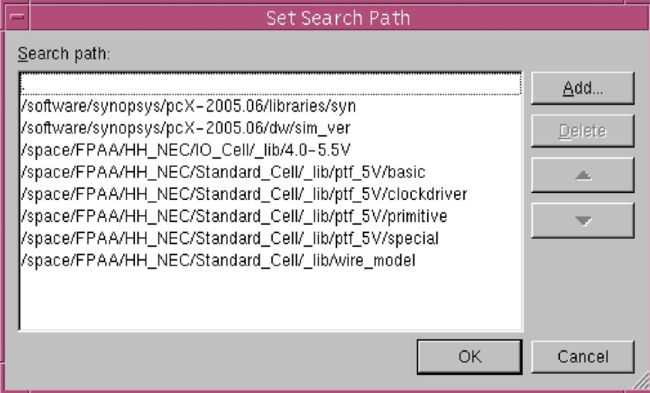

Search_path指定了搜索路径,点击右侧按钮进入如图所示对话框点击add添加库文件所在路径。

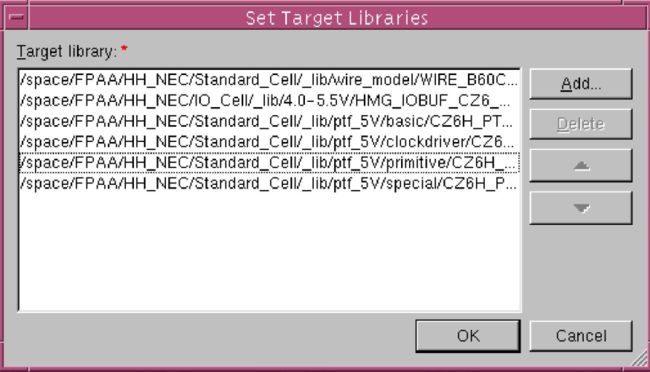

Target_library为逻辑综合的目标库,由代工厂提供的* .db文件,用相似的方法添加所需库文件。

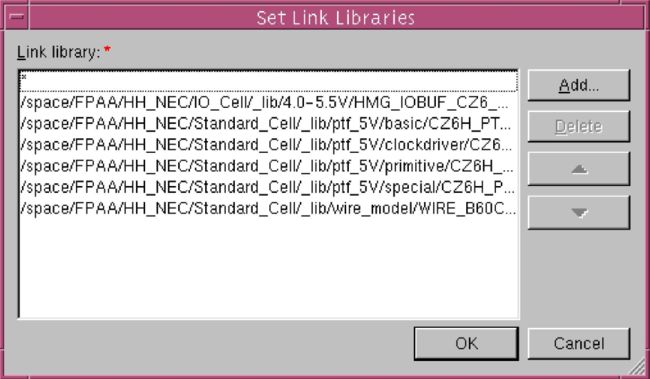

Link_library是链接库,一般和目标库相同。

注:“*” 这一项要保留,否则链接时会出错,该项指示DC在链接时首先搜索内存中的内容。

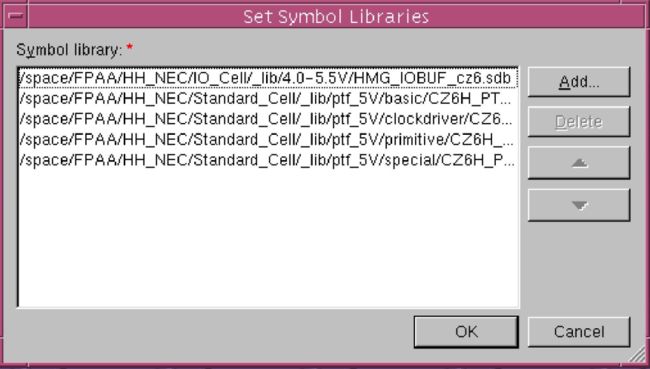

Symble_library为指定的符号库,一般为*.sdb文件,与单元的库文件对应。

在软件启动时,启动文件中所定义的变量均已加载,若希望改变其他变量的值,可以打开“File>Setup”对话框,然后选择Variables设置窗口进行设置修改。

3、设计读入

设计的读入有两种方法:analyze+elaborate和read。

3、1 analyze+elaborate

analyze命令用以分析、翻译RTL代码,并将中间结果存入指定的库中。其语法为:

analyze -library 《库名称》 -format 《文件类型》 《文件名列表》

-library《库名称》:指定中间结果所存放的库,即UNIX下的一个目录,缺省为当前目录。

-format《文件类型》:RTL源文件的类型,即Verilog或vhdl。

-《文件名列表》:所以需要分析的源文件名,若有多个文件,则用“{}”括起来。

列3.1.1(将直接数字频率合成器的所有设计源文件读入lib1库中):

hdlin_enable_presto=false /*禁止Presto编译器功能*/

define_design_lib lib1 -path "./lib1" /*将目录./lib1映射为一个设计库*/

analyze -library lib1 -format verilog {croma.v,cromb.v,ddfs.v,froma.v,fromb.v}

在图形界面中,选择“File > Analyze”。在弹出的Analyze File对话框的File域中填入源文件名,并在Library域中填入“lib1”,选中“Create New Library if it Doesn't Exist”复选框,点击OK即可。

Elaborate命令用于为设计建立一个结构级的与工艺无关的描述,为下一步的工艺映射做好准备。命令的一般格式为:

elaborate 《设计名》 -library 《库名称》 -architecture 《构造名称》 -parameter 《参数列表》 -update

《设计名》:需要描述的设计

-library 《库名称》:设计的分析结果所在的库

-architecture 《构造体名》:需要分析的构造体,针对VHDL描述同一个实体对应多个构造体的情况;对于Verilog描述,该选项可缺省或为verilog。

-parameter 《参数列表》:在这里给设计中的参数重新赋值,若缺省则参数使用缺省值。

-update:要求综合器自动跟新所有过期的文件。

例3.3.2(将先前读入的设计产生结构级描述,并设置相应的参数值):

elaborate ddfs -library lib1 -architecture “verilog” -parameter “PAL_sub = 32'h20098ACB,NTSC_sub = 32'h06F07BD6” -update

由于重置了参数值,顶层的设计名称变为“ddfs_20098acb_06f07bd6”,为方便起见,将顶层设计名改为“ddfs”:rename_design ddfs_20098acb_06f07bd6 ddfs

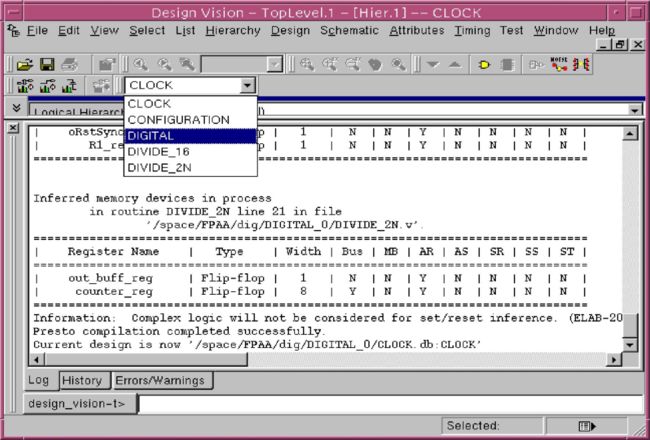

在图形界面中,选择“File > Elaborate”菜单,在弹出的“Elaborate Design”对话框的Library域中选择lib1,在design域中选择ddfs,填入相应的参数值并选择“Re-Analyze Out-of-Date Libraries”复选框后点OK。

完成以上步骤后,即可看到所有成功读入的设计模块,如前所述,利用命令行将顶层设计名改为“ddfs”。在图形界面中,双击ddfs设计即可看到该设计的符号描述。

3.2 read命令

使用read命令可以一步完成Analyze + Elaborate 的工作,并且read命令还可以用来读取db、EDIF等格式的设计(Analyze + Elaborate 仅能用于VHDL和Verilog)。但是,read命令无法支持参数修改、VHDL中的构造体选择等功能。该命令的语法为:

read -format 《文件类型》 《文件列表》

-format 《文件类型》:源文件的类型,如verilog,vhdl,edif,db等

《文件列表》:所有需要读入的源文件名,如有多个文件,则用“{}”括起来

例3.2.1(利用read命令将读取直接数字频率合成器的所有设计源文件):

read -format verilog {croma.v,cromb.v,ddfs.v,froma.v,fromb.v}

“File > Read”读入设计文件,用此方式读入时在此处不用指定顶层文件,但读入后应马上指明设计的顶层名。

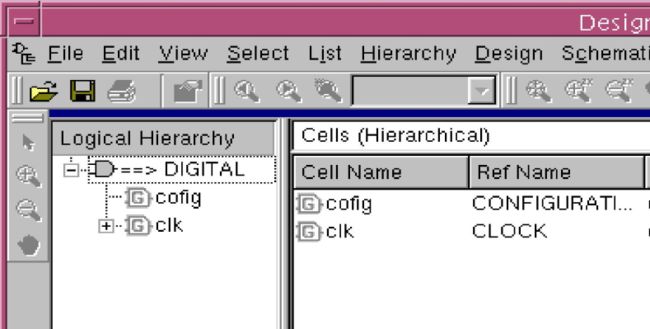

通过左侧的窗口可以观察设计的层次。

4、链接

在进一步工作之前,需要将设计中调用的子模块与链接库中定义的模块建立对应关系,这一过程叫做链接。这一过程可以利用link命令显式地完成,也可以将来综合时利用compile命令隐式地进行。推荐每次设计读入以后都用link命令执行一次链接。

注意:由于该命令以及以后提到的大部分命令均对于当前设计(current_design)进行操作,所以在执行该命令前应正确设置current_design变量。

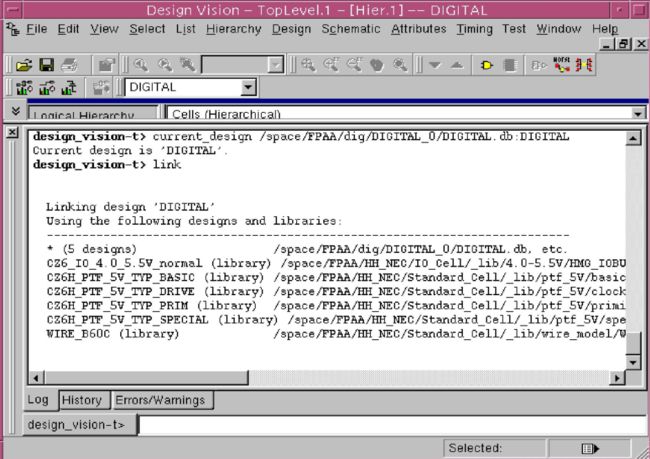

例4.1(链接直接数字频率合成器的顶层设计:ddfs):

current_design ddfs /*将ddfs设置为当前设计*/

link

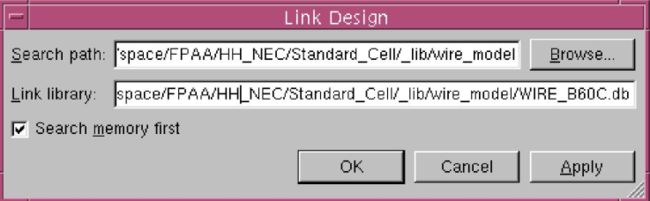

“File > Link Design”在弹出对话框中点击 “ok”即可完成链接。选中“Search Memory First”复选框将指示DC首先搜索内存来匹配相应的模块。

其执行的相关信息可从命令框中可查看。

一般有两种情况可能导致链接过程出错:

1、设计中所调用子模块的描述文件没有读入;

2、设计中使用了工艺库中的单元,但该工艺库没有加入链接库(link_Library)或因为搜索路径(search_path)设置有误而导致DC无法正确定位链接库。

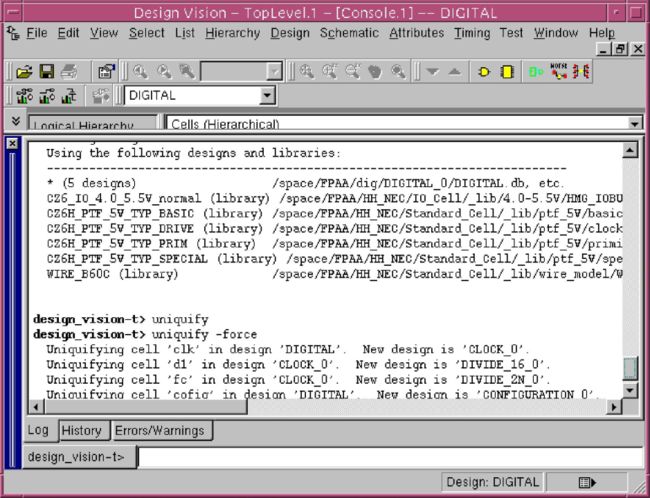

5、实例唯一化

当设计中有某个子模块被多次调用时就需要对设计进行实例唯一化。实例唯一化就是将同一个子模块的多个实例生成为多个不同的子设计的过程。之所以要进行实例唯一化是因为DC在逻辑综合时可能使用不同的电路形式来实现同一个子模块的不同实例,从而这些实例在DC看来是不同的设计(尽管其调用的子模块代码和功能完全相同)。

例5.1 (将ddfs设计进行实例唯一化):

current_design ddfs

uniquify

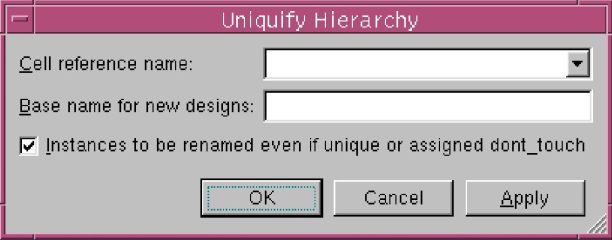

GUI方法:“Hierarchy > Uniquify > Hierarchy”在弹出对话框中默认点击“ok”即可,命令框中将显示“design_vision-t> uniquify”。

若选中“instances to be renamed even if unique or assigned don’t_touch”则会强制将所调用的模块从新命名,此时命令框中显示“design_vision-t> uniquify –force”。

注意:若设计中不存在同一子模块被多次调用的情况(比如上例中的ddfs设计),可不比进行实例唯一化,但仍推荐进行。

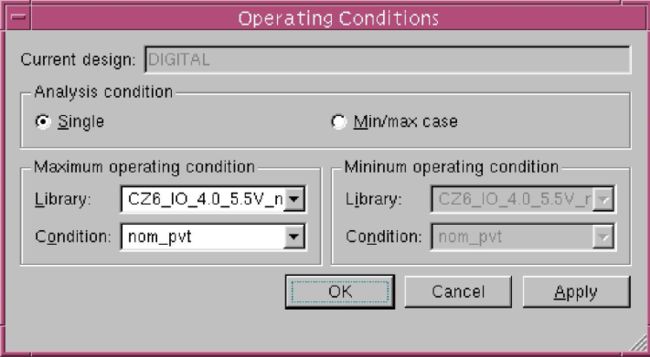

6、设置电路的工作环境

“Attributes > Operating Environment > Operating conditions”选择相应的库和其对应的条件点击“Apply”添加,添加完成后点击“ok”关闭对话框。

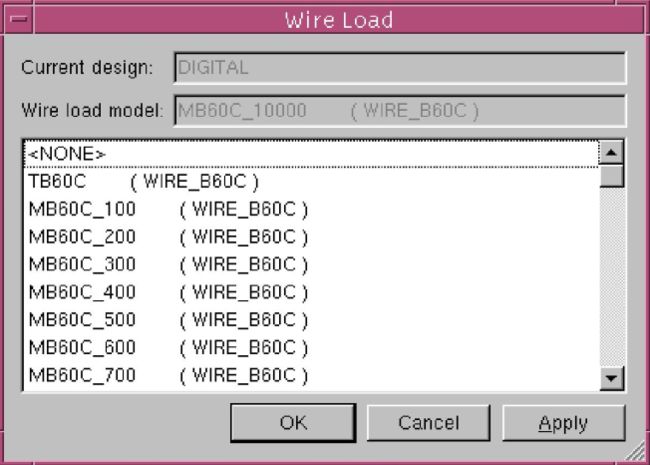

7、设置连线负载

“Attributes > Operating Environment > Wire Load”

本实例中所用的库有两种连线负载模式“TOP对应上图TB60C”和“Macro对应MB60C_*

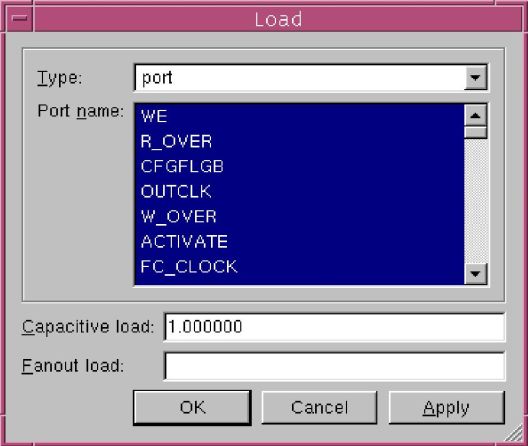

8、设置输出负载

点击工具栏中“芯片样式”的图标开启符号窗口,选中要设置的输出引脚(可多选),然后点击“Attributes > Operating Environment > Load”打开设置对话框进行设置。默认电容单位为pf。

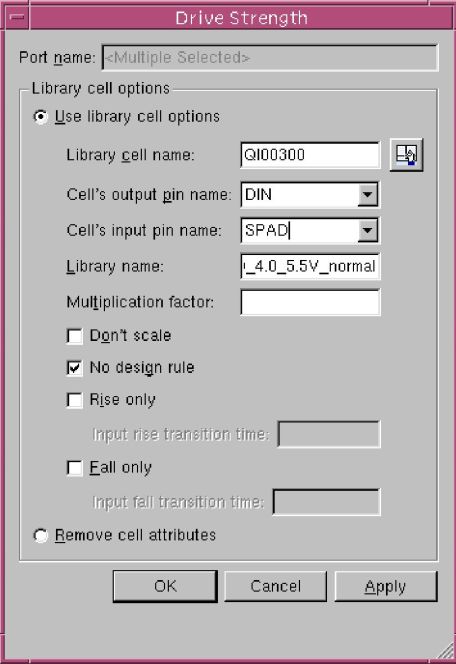

9、设置输入驱动

方法与上类似,选折需要设置的输入引脚“Attributes > Operating Environment >Drive Strength”打开设置对话框进行相应的设置。

由于通常情况下,设计的时钟端由驱动能力很大的单元或树形缓冲来驱动,所以可以将其驱动能力设为无穷大,即将其阻抗设为0。如本设计中时钟端口名称为 “DCLK”,则只需在命令窗口中输 入“set_drive 0 DCLK”即可。复位端口一般也做相同的处理。

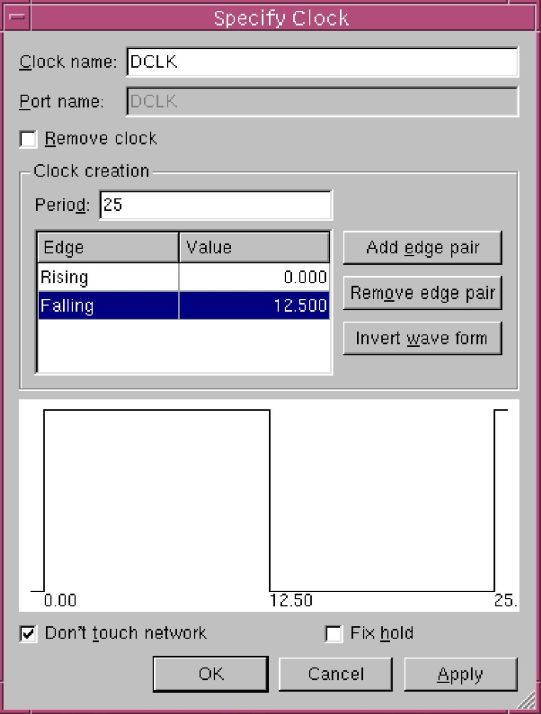

10、创建时钟

选中时钟端口如本设计中的“DCLK”, “Attributes > Specify Clock”打开设置框。

分别填入周期、上升时刻、下降时刻后点击“Apply”,便可在下面窗口中看到时钟波形。

如图生成的是一个周期为25占空比为1:1的时钟。默认时钟单位为“ns”。由于时钟端口的负载很大,DC会使用Buffer来增加其驱动能力。但一般设计者都使用布局布线工具来完成此项工作,所以有必要指示DC不要对时钟网络进行修改,可以选中上图中“Don’t touch network”进行设置。

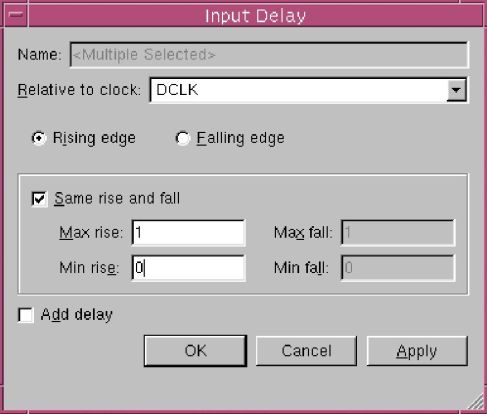

11、设置输入延时

选中需要设置的输入端口(可多选)“Attributes > Operating Environment > InputDelay”进行相应设置后点击“OK”。

12、设置输出延时

“Attributes > Operating Environment > Output Delay”设置方式与input delay完全类似。

如果是从寄存器直接输出,则可以不设置输出延时,因为触发器的输出延时基本是固定的。

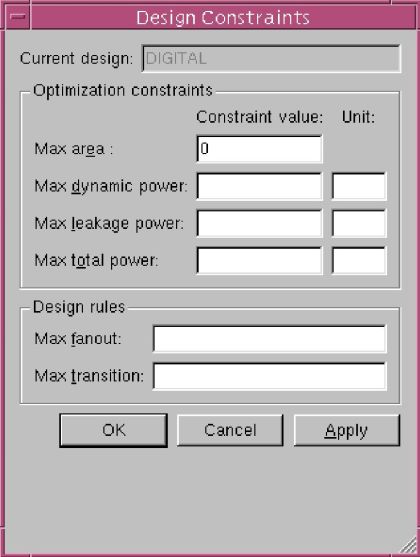

13、设置面积约束

“Attributes > Optimization Constraints > Design Constraints”。在Max area中填入0,这样能够尽可能的对面积进行优化。然后点击“ok”。

14、逻辑综合

完成以上基本设定之后便可以对设计进行逻辑综合。“Design > Compile Design”选择默认设置,点击“ok”。

15、查看综合结果

等综合完毕之后,可以从“Design > Repot *”查看相应的综合报告

16、保存综合后的网表文件(*.v)

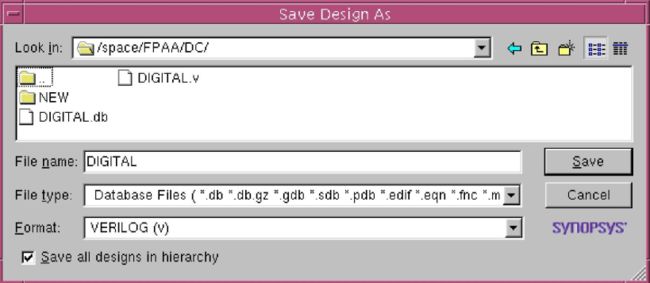

“File > Save As”打开对话框,Format选折“Verilog (v)”

17、导出时序文件(*.SDF)

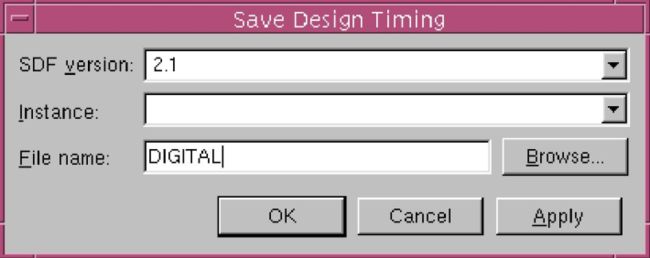

“File > Save Info > Design Timing”Instance项不选,保持空白。这样能直接保存与最顶层相对应的延时文件。之后可用此文件进行综合后的仿真。

18、导出设计约束文件(*.SDC)

该操作可以用write_sdc命令实现。(可参考在用图形界面保存SDF文件时,命令框中出现的与图形界面操作相对应的命令语句)。如:“write_sdc /space/FPAA/DC/DIGITAL.sdc”执行之后会把DIGITAL.sdc文件保存在/space/FPAA/DC文件夹中。该文件在会面做布局布线时将会被使用到。

补充:

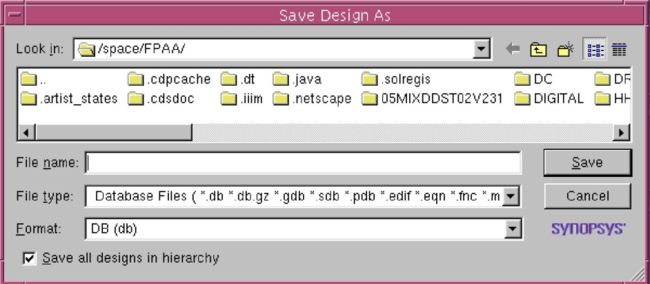

在每完成一步或几步设置之后应及时对设置进行保存和备份,保存格式为db。

这样只要读入该文件就会读入之前进行的设置。

(不过库文件及路径等需要从新设置)