姓名:高岩 学号:13020199025

本文转载自:http://www.eefocus.com/embedded/376519

【嵌牛导读】:比较详细的介绍了嵌入式视觉系统开发过程中需要考虑到的安全性和保密性问题。

【嵌牛鼻子】:嵌入式,安全性,保密性

【嵌牛提问】:嵌入式视觉中安全性与保密性效果如何?安全与保密问题能否得到保障?

【嵌牛正文】:

嵌入式视觉 (EV) 系统的广泛应用已经是无所不在,高级驾驶员辅助系统 (ADAS)、机器视觉、医疗成像、增强现实以及众多其他应用等等, 都离不开一个搞笑的嵌入式系统平台。

然而, 采用 EV 系统虽然能给最终应用带来明显优势,但也要确保采用该系统后不会造成人身伤亡或财产损失,这对开发人员来说义不容辞。要做到这点,不仅要考虑设计的安全性,严格遵循工程寿命周期和公认标准,还需要考虑 EV 系统的保密性,防止被恶意或其它方式修改。

EV 系统的终端应用是安全性和保密性需求强弱的驱动因素。例如,消费类应用对于安全性和保密性的要求,就比 ADAS 或机器视觉系统的要求低得多。

为在这些设计考虑因素和安全性与保密性要求方面协助我们,行业制定了多个知名的国际标准(如 IEC61508),为众多要求功能安全性的电子系统保驾护航。另外,还有更多专用标准,例如用于汽车应用的 ISO26262、用于机器设备的 IEC62061 和用于飞行应用的 DO178/DO254。此外,根据最终市场的情况,商业应用也要求 CE、UL 或 CSA 标识。这些标准中的每一项都有相应的开发和验证要求,需要落实在机构的工程设计和交付生命周期中以确保合规性。

而 EV 系统的核心是处理内核,该系统一般会采用一个 FPGA 或可编程的 SoC,以用于解决目前提出的一系列问题。

这些标准的实际意义是什么?

许多此类安全标准使用不同的名称定义安全级别,比如 IEC61508 的“安全完整性级别”(SIL)、DO254 的“设计保障级别”(DAL)和 ISO26262 的“汽车 SIL”(ASIL)。在 SIL、DAL 和 ASIL 内包含一系列不同级别,可根据应用的危害程度采用不同的安全级别。一般来说,这些级别是按失效时间(小时数)定义的,正确的说法是“失效时间(小时数)”。虽然这些不同的标准总体上保持一致,但也存在如下差异。

安全标准和不同级别

在开展设计分析时,会演示如何达到认证要求的级别。工程师习惯使用时间失效(FIT)率,即失效时间(小时数)的倒数。在 SIL4 和 DAL A 安全级别下运行时,这要求采用正确架构的系统来实现这些要求。

系统考虑因素

安全系统的开发要求出色的系统工程设计,同时在每个开发层级上配合明确定义且可跟踪的要求。

如上所述,工程生命周期由最终应用和所需的结果认证共同决定。该生命周期将决定从 EV 系统的概念、生产到处置所采取的总体工程方法。

在这个生命周期内,您可以定义工程评审门,以控制项目的进展。在这些评审中,由独立技术专家审核需求、设计、技术报告和测试结果,以确保设计成熟度足以支撑进入到下一阶段,或是需要进行进一步工作来达到所需的依据标准要求。

图 1:交付与工程生命周期示例

工程计划也要勾勒出每个层级的验证和确认流程,通过履行这一流程获得达到适用标准合规要求的证据。这可能要求在各种环境工作范围、动态振动与冲击下测试 EV 系统。您甚至可能必须让 EV 系统接受加速寿命测试,以确保能够达到系统的使用寿命。

当涉及到保密性时,您必须考虑一系列方面的因素,即工程师在试图确保其设计安全性时面临的高层次问题。这些方面包括如下:

-竞争对手对设计进行逆向工程操作

-未经授权对设计的改动

-未经授权访问设计中的数据

-未经授权控制或操控最终应用

有多种方法可供您解决一部分此类难题。您可以使用加密比特流,从而控制对设计和制造文件的访问。或是您可以通过限制对最终产品 JTAG 端口的访问,同时根据选择的器件的架构采取软件保密性措施,可以保护物理设计。

高质量设计

显然您需要根据终端应用应用考虑选择什么样的组件和制造标准,以确保您符合应用的质量要求。在处理内核方面,您可以使用赛灵思 FPGA 和 SoC 器件,此类器件既符合标准商用质量标准的等级,也符合工业、汽车、航空航天与军用等更严苛标准的等级。这样通过选择正确的组件等级,工程师团队从一开始就提高质量。

另外,还有一系列设计技术可供您用于帮助满足这些标准的严格要求。为了力助确保您满足可靠性要求(也即常称的成功概率),在必要时,您可以使用可靠性工程技术为系统中的各项功能创建可靠性方框图,并确保避免任何危险的失效模式和单点失效。在设计自身内,您可以进行失效模式影响与危害性分析 (FMECA)。开展这一分析的层级可视应用而定,可以从功能模块级直至组件级。FMECA 将考虑潜在故障模式、后效和对系统的最终影响,它还将考虑故障是否能被内置的自检和监控系统检测到。如果您要开发组件级的 FMECA,您就需要考虑设计中每个组件的部件应力分析 (PSA),以确保组件在正确的降额条件下工作。您应用的降额水平将取决于选择的常用标准。标准包括国防部 (Mil-STD 1547) 和欧洲太空总署(ESCC-Q-30-11A)。如果您不进行 PSA 分析,就可能在过应力情况下使用器件,造成这些器件成为设备使用寿命的限制因素。根据 FMECA 的预测,这些器件的失效可能导致也可能不会导致系统的损耗或性能衰减。

在分析可靠性的同时,您还能对系统进行威胁分析,根据使用案例确定系统威胁以及对识别出的威胁可能采取的缓解策略。

架构案例分析

在硬件层面,您需要考虑系统功能以及您如何实现功能安全性与保密性。虽然这可以从头开始实现,但更好的方法是选择已经支持这些功能的组件,例如赛灵思 Zynq® All Programmable SoC。

任何 EV 系统的核心都是图像处理流水线。这要求将高带宽处理能力与监视及控制功能相结合。相对于传统的处理器与 FPGA 组合,Zynq 全可编程 SoC 能让我们拥有紧密集成的架构。

这种处理器和逻辑结构之间更紧密的集成不仅能带来更出色的 SAWP-C 解决方案,由于处理器和逻辑结构之间的交互不对外暴露,不给恶意访问或其他访问可乘之机,从而提供更安全的系统。

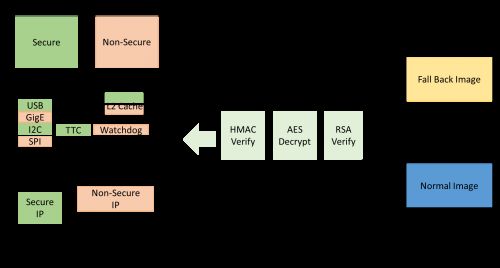

在电子架构内部,您可使用 Zynq全可编程SoC 的嵌入式安全架构提供安全配置功能。在可编程系统 (PS) 和可编程逻辑 (PL) 中,您可使用三段法确保系统分区的安全性。三段法包括散列消息认证代码 (HMAC)、高级加密标准 (AES) 解密和 RSA 认证。AES 和 HMAC 都使用 256 位私钥,而 RSA 使用 2,048 位密钥。Zynq 全可编程 SoC 的安全架构还允许启用或禁用 JTAG 访问。

当您在为我们的非易失性引导介质生成引导文件和配置分区时,这些安全特性是启用的。还可以定义一个回滚分区,这样如果最初的第一阶段引导加载程序加载其应用失败,就能回滚到存储在不同内存位置的该应用的另一个备份。

在您成功启动设备并开始运行时,我们可以使用 ARM Trust Zone 架构实现正交环境,限制对 Zynq AP SoC 内的硬件功能的访问,包括可编程逻辑 (PL) 外设在内。您还可以细分内存和 L2 缓存,确保安全环境和非安全环境间的交互受到限制。

Zynq AP SoC Secure Boot 和 Trust Zone 实现

如果要在 Zynq AP SoC 的可编程逻辑架构中实现图像处理流水线,您还可以使用 Trust Zone 提供对可编程逻辑架构中的 IP 核的安全或非安全访问。这样您就能够使对图像处理链的关键方面进行安全访问,避免发生对配置的无授权修改。

图像处理流水线可使用定制开发模块或来自 IP 库的模块实现。

部分安全性与保密性实现方案(例如 IEC61508)可能要求彼此隔离设计元,这可能是建立模块冗余,区分安全区域或测试功能的结果。通过使用隔离设计流程 (IDF),您可以在已确认区域间强制实施物理隔离。在使用 Vivado® Design Suite 时,支持对 Zynq 器件开展这种操作。

用于安全关键型 FPGA 的 IDF 强制政策

如果您想在处理链或其他控制逻辑中实现多数表决,隔离设计流程对您而言就非常有用。使用隔离设计流程可确保冗余模块间的唯一互联是通过可信路径实现的。

在实现设计的时候,您还需要考虑一系列针对器件和工具的设计考虑因素。当然终端应用应用和您的总体工程管理计划将决定采用这些技巧的必要性。

-在内存上使用检错纠错 (EDAC) 码。必要时,该功能还可与擦除功能相结合,定期读取和纠正内存中的数据,不管应用是否正在访问内存。

-在定义控制字时运用汉明(Hamming) 码的不同,增大命令字之间的汉明距离,同时要求实现更多位,有助于提高设计的可靠性。

-对关键命令使用 ARM 和 FIRE 方法,该方法要求动作关键型功能使用两个单独命令。

-在外部通信接口上使用 EDAC 码

-综合性内建测试(BIT)功能能报告系统的健康状态或其他状态Zynq XADC 是 BIT 系统功能非常强大的一个组件,因为通过多路复用器引入外部信号,它能够实现对器件电压和温度的监测。

总结

对您的嵌入式视觉系统应用正确的功能安全工业标准是能够做到的,有相当数量的组件、工具和开发方法可供系统开发人员使用。

要确保我们满足您的 EV 系统的认证要求,您需要从设计之初就开始正确判断适用标准,并生成工程管理计划,定义工程生命周期,用以收集通过认证所需的证据。