IBM正在研究的芯片“黑科技”

大部分读者对 IBM 最熟悉的应该是他们的“深蓝”和其推出的笔记本,但其实在半导体领域,IBM 也有很深的研究。

据不完全统计显示,倒装芯片封装技术是又 IBM 在 1960 年首先引入的;单晶体管 DRAM 是由 IBM 科学家 Robert Dennard 最先提出的;就连现在在嵌入式处理器领域广泛采用的精简指令集都是由 IBM 专家设计的。其他诸如 SiGe 硅工艺、铜互连、绝缘硅、应变硅和 Power 处理器,也无一不是 IBM 带给半导体业界的创举。

虽然因为各种主观和客观的原因,IBM 已经逐渐丢失了过往的那种震撼力。但从他们过去一年的研究成果看来,“蓝色巨人”还是走在集成电路技术探索的最前线。

下面我们来看一下 IBM 正在研究的集成电路“黑科技”

5nm 以后的晶体管选择:Nanosheet

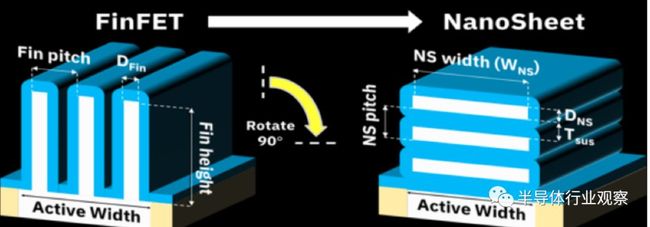

最近,三星 3nm GAA 工艺试产成功的消息传遍了笔者的朋友圈,也引起了读者的广泛讨论。因为在进入了 5nm 之后,FinFET 的魔力逐渐失去,而为了持续提升晶体管的表现,业界开始探索打破电流一直由通道顶部的“闸门”来控制传统的做法,这就催生了 Gate-All-Around (简称 GAA),

据介绍,GAA 利用特定的材料,能将整个电流通道包裹成类似 3D 结构,虽然这种设计比“闸门”更加复杂,但这能让芯片晶体管大幅提升性能,并能让未来的 2nm 和 1nm 的实现成为可能。

根据之前的资料,三星的 GAA 技术,是他们与 IBM 共同合作的结果。

IBM Research 方面表示,公司从事 GAA 晶体管研究已有十多年了,其设备架构已从单纳米线( single nanowire )发展到堆叠纳米片( stacked nanosheet)。2015 年,IBM 研究人员在 S3S 会议上发表了第一篇纳米片论文,首次为“纳米片”命名。IBM Research 方面生成,公司将继续与合作伙伴紧密合作,以加速从 FinFET 到纳米片晶体管的行业过渡。

IBM Research 指出,公司的卓越设备架构利用了 Gate all around(GAA)的堆叠纳米片,从而解决了 FinFET 在真正的 5 纳米(nm)节点及以后所面临的若干挑战。

对晶体管的未来发展有了解的读者,一定会发现 IBM 在这里并没有使用之前大家所讨论的纳米线,而是从 2017 年开始采用了纳米片.针对这个问题,IBM 硅集成和器件总监 Huiming Bu 之前在接受 IEEE 采访的时候提到,这主要与纳米片可以带来 pre-finFET 的优势有关。他指出,设计人员以前通过改变晶体管的宽度来提升操作速度或能源效率,而不是改变 finFET 晶体管中的硅的量.因为后者意味着使一些鳍更长而另一些更短。但由于制造的限制,鳍状硅片必须高度相同,所以这是不可能实现的。

为此 IBM 采用了宽度可以做到 8 到 50 纳米之间的纳米片。他们指出,:“更宽的纳米片性能更好,但是需要更高的功耗。宽度较小的纳米片虽然性能较差,但可以减少功耗。”

IBM 方面首先表示,使用这些晶体管,能带来更好的计算性能和更低的功耗,这主要与 GAA 中能提供更好的静电控制和更高的封装密度有关。他们表示 NanoSheet 提供了更好的功率性能设计点。与目前晶圆厂中可用的最新,最出色的 7nm FinFET 技术相比,NanoSheet 技术在相同功率下的性能提高了 25% 以上,在相同性能下的功耗节省了 50% 以上,IBM 方面强调。

其次,多样化的 sheet 具有更简化的设计。同时,借助极紫外光刻(EUV)技术,Nanosheet 技术能给 AI 和 5G 时代带来一种更好的计算机产品设备体系结构。这可以实现更加通用的设备设计,因为可以将具有不同通道沟通的纳米片设备共集成在同一芯片中,以进一步优化功耗和性能。

第三,沟通厚道控制;IBM 方面表示,增大 NanoSheet 堆栈沟道层可以创建用于沟道构造的原子级控件。FinFET 不可能实现这种精确的沟道厚度控制,因为它是由光刻技术与 RIE 结合定义的,其局部和全局工艺变化远高于外延厚度变化。

在早前举办的 IEDM 上,IBM 的三位研究员 Zhang Jingyun、Ruqiang Bao 和 Nicolas Loubet 也对 Nanosheet 的未来发展提出了他们的解决方案。

Zhang Jingyun 表示,由于拥有优异的静电性能,所以纳米片 GAA 器件可以实现极高的栅极长度(Lmet)。除了宽的 Sheet 外,Lmet 缩放对于满足高性能计算需求也至关重要。为了在如此高比例的 Lmet 下获得良好的短沟道性能,控制 sub-fin 泄漏至关重要。而 IBM 的研究人员则通过在 S / D 和栅极区域下方插入电介质层,从而消除了比例缩放的 Lmet 的 sub-channel 泄漏,从而开发了完整的底部电介质隔离(BDI)方案。此外,此功能还减少了寄生电容,并为 GAA 纳米片技术提供了额外的功率和性能改进。

Ruqiang Bao 也强调,在 GAA 纳米片沟道结构中,由于存在片对片间距(Sheet-to-sheet spacing:Tsus),栅极区域已演化为 4D。HPC 等应用也要求晶体管在满足多个阈值电压要求的同时控制 Tsus 厚度。而 IBM 研究人员已经发明了新颖的工艺和集成方案,以实现多种偶极厚度以实现无体积占用的多 Vt(即无体积多 Vt),从而实现了非常薄的 Tsus。此外,研究人员发明了一种在宽 sheet 图案化期间控制金属栅极边界的方法,从而解决了纳米片技术的一个基本问题。

Nicolas Loubet 则指出,GAA 纳米片技术的独特结构特征是在设备体系结构中形成了(Inner Spacer。我们开发了一种新颖的各向同性( novel isotropic)干法蚀刻技术,以对硅(> 150:1)和电介质(> 1000:1)的极高选择性来精确控制横向硅锗蚀刻。

此外,这种卓越的蚀刻工艺可在沟道释放过程中使用,可提供极低的沟道厚度变化以及静电和电阻变化,这对于优化高性能计算堆叠纳米片器件的功率/性能至关重要。

突破常见的冯诺依曼瓶颈:内存内计算

进入了 AI 时代之后,AI 任务对计算性能的需求越来越高,传统的计算和存储分开的架构因为带宽的限制,在数据交换和实时处理上面临严峻的挑战。为此,业界在探索一种被称为内存内计算(In Memory Computing)的方案,IBM 方面推出的基于相变存储(PCM)的内存方案则是其中的一种。

IBM 方面表示,PCM 单元的主要优势在于它可以处理大多数繁重的数据处理,而无需将数据传输到 CPU 或 GPU,从而能以较低的能源开销实现了更快的处理。从介绍我们得知, IBM 的 PCM 单元将用作 CPU 加速器,就像 Microsoft 用来加速 Bing 并增强其机器学习能力的现场可编程门阵列(FPGA)芯片一样。

据 IBM 称,其研究表明,在某些条件下,其 PCM 芯片可以以模拟方式运行以执行计算任务,并具有与四位 FPGA 存储器芯片相当的精度,但能耗却降低了 80 倍。

但我们也应该清晰认识到,模拟 PCM 硬件的不足之处在于,它不能用于高精度计算。幸运的是数字 CPU 和 GPU 都可以使用,IBM 认为混合架构可以达到平衡,从而提供更快的性能,更高的效率和精度。而该设计会将大部分处理留给内存,然后将较轻的负载移交给 CPU 进行一系列精度校正.

而在 2017 年,IBM 科学家展示了用于人工智能应用的存内计算方案。IBM Research 宣布其科学家已经证明,运行在一百万个相变存储器(PCM)设备上的无监督机器学习算法已成功地在未知数据流中发现了时间相关性。IBM 方面表示,与最先进的经典计算机相比,该原型技术有望在速度和能源效率方面提高 200 倍,使其非常适合为超密集,低功耗和大规模并行计算系统提供支持 AI 中的应用程序。

据介绍,研究人员在测试中使用的是由碲化锗锑合金制成的 PCM 设备,该设备堆叠并夹在两个电极之间。当科学家向材料施加微小电流时,他们会对其进行加热,从而将其状态从非晶态(具有无序的原子排列)改变为结晶态(具有有序的原子排列)。IBM 研究人员已使用结晶动力学来进行适当的计算。

从 IBM 的介绍我们得知,利用硫族化物玻璃的独特性能,相变存储怒可以顾名思义地改变其状态。硫属化物玻璃具有两个不同的物理相:高电导的结晶相和低电导的非晶相。这两个阶段共存于存储元件中。PCM 元件的电导率可以通过小的电脉冲进行增量调制,这将改变元件中的非晶区。

然后,总电阻由非晶区的大小确定,原子排列用于编码信息。IBM 指出:“因此,它不是像数字世界那样记录 0 或1,而是将状态记录为两者之间值的连续体——模拟世界。” IBM 指出。

但 IBM 方面强调,由于其低功耗要求,高能效和高可靠性,模拟技术非常适合边缘 AI。模拟加速器它将推动 AI 硬件加速的发展路线图超越常规数字方法的范围。但是,尽管数字 AI 硬件正在争相降低精度,但迄今为止,模拟一直受到其相对较低的固有精度的限制,从而影响了模型精度。为此开发了一种新技术来对此进行补偿,从而为模拟芯片实现了最高的精度。

据介绍,他们是通过一种称为 Proj-PCM 的新颖方法提高了 PCM 存储精度和稳定性,该方法是在与相变段平行的位置插入一个非绝缘的投影段。在写过程中,投影段对设备的操作影响最小。然而,在读取期间,编程状态的电导值主要由投影段确定,这明显不受电导变化的影响。这使得 Proj-PCM 设备可以实现比以前的 PCM 设备更高的精度。

这就是他们在 2018 年推出的一种基于相变存储器(PCM)的 8 位“模拟”芯片的新设计。

据了解,盒子中的存储材料的电导随其物理状态而变化,可以使用电脉冲进行修改。这就是 PCM 能够执行计算的方式。因为状态可以是 0 到 1 之间连续区域的任何位置,所以将其视为模拟值的原因之一。

但我们同时也应该看到,相变存储器(PCM)等新兴技术的使用仍然带来重大挑战。他们很容易受到噪声,电阻漂移,响应于电刺激的非对称和非线性电导率变化的影响以及可靠性问题。为了解决这些问题,来自 Almaden,Yorktown Heights,东京和苏黎世的实验室的 IBM 研究人员开发了新设备,新算法、体系结构解决方案,新颖的模型训练技术以及完整的定制设计。

世界上最小的 DRAM 单元

据 IBM 介绍,由于其出色的存储密度和低成本,DRAM 通常可以实现主存储器的功能。DRAM 的高存储密度源于其架构的简单性。DRAM 的存储单元也只是由 MOSFET 晶体管和电容器组成。

尽管 DRAM 是计算机的主存储器,但通常不集成在 CPU 芯片上,而是作为一个与高速总线连接的独立芯片而存在。而我们通常用 SRAM 来制作 CPU 芯片上的内存(通常称为高速缓存)。SRAM 不需要电容器,并且有比 DRAM 更高的速度运行。SRAM 的缺点则是存储密度较低。然而,用于 CPU 处理和电容器形成的制造技术已经变得非常专业。那就意味着在 CPU 芯片上嵌入 DRAM 已经没有了吸引力。

IBM 表示,过去的二十年中,人们一直在尝试摆脱电容器,从而进一步减少 DRAM 单元的面积和制造成本。而为了进一步缩小尺寸,拆掉电容器几乎已成为当务之急。这就要求做到在不减少可存储电荷量的情况下,缩小 cell 的横向尺寸,那就留出了一条可供制造的途径,即:使电容器“藏”得更深。

但 IBM 指出,从长远来看,这是一个瓶颈,这不仅是由于几何(geometrical)约束,而且还因为“孔”(well)顶部的电荷积累使使用整个存储容量更具挑战性。而将电荷存储在晶体管主体中已被认为是进一步缩小尺寸的最佳策略。研发人员已经使用硅对无电容器 DRAM cell 的不同变体进行了实验研究。但是很少有人关注基于替代半导体材料的类似概念。在 2019 年的《自然电子杂志上》,IBM 展示了有史以来最小的无电容器 DRAM,其存储单元长度只有 14 纳米。

这是一个单晶体管,无电容器的 DRAM cell,它使用晶体管主体作为一种电容器,其中的电荷(在这种情况下为空穴)被临时存储在其中。电子空穴从晶体管主体的注入和抽出使得能够调节晶体管的静电行为,从而导致两个不同的电流水平。像 InGaAs 这样的 III-V 材料通常具有比硅更小的带隙,而硅原则上具有在低得多的电压下工作的潜在优势。反过来,这转化为可能更低的功耗。

IBM 方便表示,他们已经证明了无电容器 MSDRAM cell 的栅极长度为 14 纳米的可行性。通过使用晶体管本体来存储电子空穴数量,我们能够获得对应于二进制状态 0 和 1 的两个不同的电流电平。而该存储器概念的实验实现证实了 TCAD 仿真获得的结果。

与基于硅的实现相比,IBM 使用 InGaAs 的新颖概念为实现 DRAM 存储器的积极小型化提供了一条有希望的途径,同时还降低了功耗。从有关性能指标(例如保留时间)的这一概念进一步改进的潜力,而 IBM 艰辛存在可行的策略来实现这些改进。

其实以上技术只是 IBM 研究项目的冰上一角,在 IBM Research 的博客上,他们还介绍了他们利用晶体半导体磷化镓制成高性能光子器件的发展。他们表示,这项工作代表了在芯片上集成半导体材料的光处理方面的突破,打开了可能对信息技术和计算的未来产生重大影响的众多应用之门。其他如量子计算机、为深度学习加速器而提出的一种称为电化学随机存取存储器或 ECRAM 的创新性非易失性存储器和首款可在室温下工作的可级联全光晶体管等都是 IBM 研究人员在探索的未来。

相信在这些研究人员的努力下,整个产业会在瓶颈限制下找到一条新的出路。