写在正文之前:

疫情高发,2020的春节,希望大家都能平安度过,武汉加油,祖国加油!

正文:

PCIe一直以来都是在我心头挥之不去的一片荆棘,不管是主流的X86架构,ARM架构,还是新兴的AI芯片,无一不把PCIe总线接口作为重要的互联接口。而在过去的工作中,芯片架构,总线拓扑,带宽计算,也都躲不开PCIe相关的研究。所以,最近抽出时间学习了PCIe总线架构和相关知识,在此总结(已经在公司内部做了分享),希望与各位交流共勉。

第一节:PCIe概述

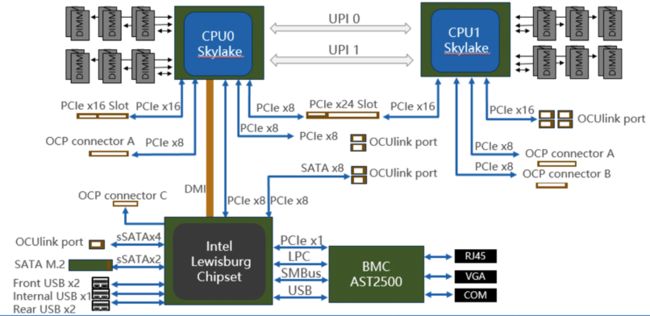

为了直观的给大家一个认识,首先抛出了这张Intel服务器的架构图,可以清晰的看到PCIe接口所处位置和主要连接对象。图中有很多专业名词,有兴趣可以查一下,对于长期从事服务器芯片开发的技术人员,应该比较熟悉了。

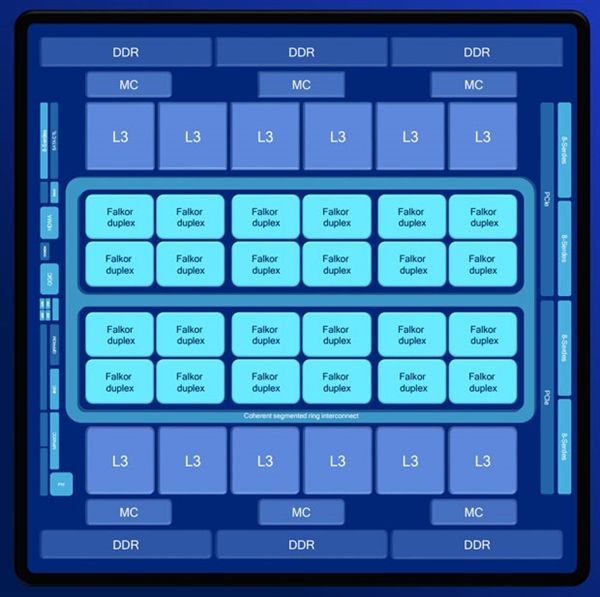

下面这张图片是高通/华芯通公司ARM 48核服务器的芯片架构,虽然华芯通已经不复存在,但是仍然留下了宝贵的学习资料.

通过上面两张图片,可以看到PCIe接口在芯片上的位置核结构,接下来会对PCIe做基本的介绍:

Peripheral Component Interconnect Express:

高性能高带宽的串行互联标准

与PCI总线保持软件兼容

串行差分双工信号线

点到点互连

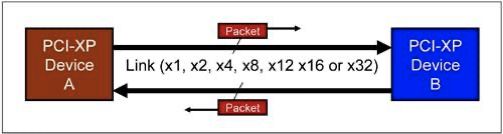

lane的概念:一组RX(2条差分线)与一组TX(2条差分线)

link的概念:若干lane组成的一条逻辑通道,有x1, x2, x4, x8, x16

那么什么是差分信号呢?

一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是1还是0

差分信号在布线时要求”等长”、”等宽”、”贴近”,而且在同层,所以外部干扰噪声将被”同值”而且”同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小, 所以差分信号可以使用更高的总线频率

差分信号可有效抑制电磁干扰(EMI, Electro Magnetic Interference)

我们在讨论芯片的架构时,经常会考量一个重要的PCIe指标,就是他的带宽:

计算方法:

PCIe3 .0 协议支持 8.0 GT/s, 即每一条Lane 上支持每秒钟内传输 8G个Bit。

而PCIe 3.0 的物理层协议中使用的是 128b/130b 的编码方案。 即每传输128个Bit,需要发送130个Bit。

那么, PCIe 3.0协议的每一条Lane支持 8 * 128 / 130 = 7.877 Gbps = 984.6 MB/s 的速率。

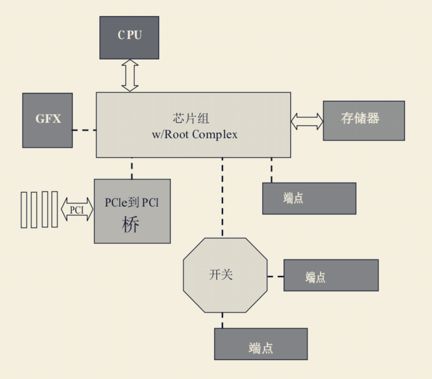

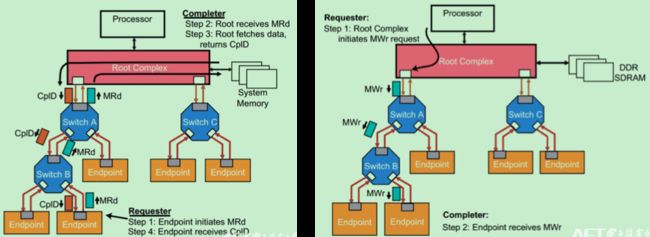

PCIe的基本拓扑结构:

如下图,PCIe具有主要的一些组件,组成了整体的拓扑结构.

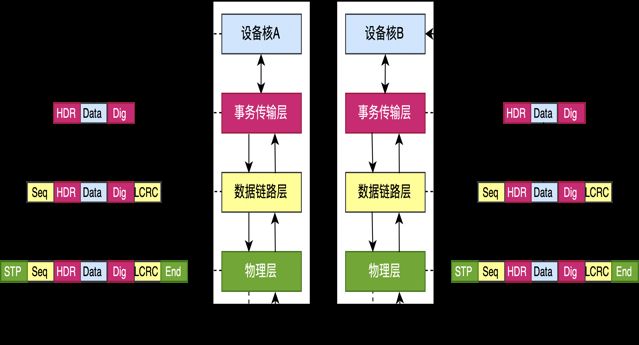

第二节:PCIe分层结构

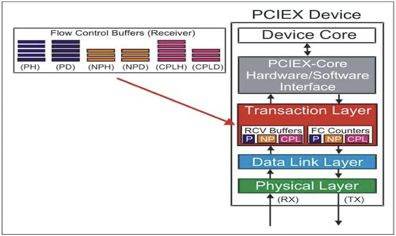

PCIe是层次化的协议结构:

事务层:

发送端TLP创建;接收端TLP解码、校验;QoS、Flow Control、Ordering

数据链路层:

DLLP的创建、解码、校验;Ack/nak应答机制

物理层:

Ordered-Set packet创建/解码

发送/接收所有Packet

128b/130b编码,扰码

链路训练和初始化

接下来会介绍三个层次各自的功能:

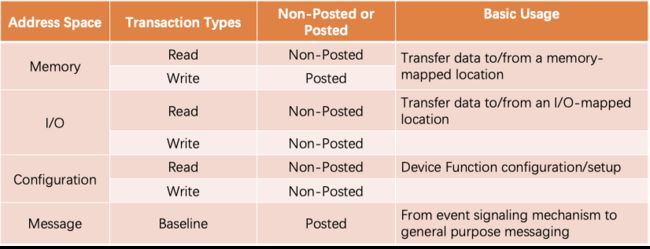

1. 事务传输层:

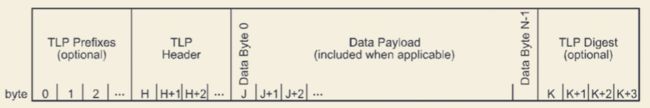

事务传输层产生发出的和接收的事务传输层数据包(TLP)

TLP包括一个报头(Header)、一个可选数据配载(Payload)以及一个可选的端到端CRC(ECRC).

TLP可以是请求(Request),也可以是对请求的响应(Response),永远是4byte的倍数

Header指定事务类型、优先级、地址,路由规则及其他数据包特征。

发送事务传输层构建数据包Header、添加ECRC并门控Payload的传输

接收事务传输层检查TLP格式和Header,检查ECRC

这里给出一个memory Read/Memory Write传输的例子:

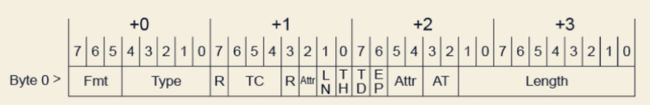

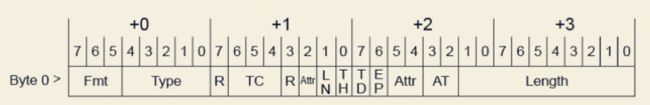

对于事务层的传输包,具有一个包头(Header):

Fmt[2:0]: Format of TLP, bits 7:5 of byte 0

Type[4:0]: Type of TLP – bits 4:0 of byte 0. Mrd/Mwr/IORd/IOWr/Msg/…

TC[2:0]: Traffic Class – bits 6:4 of byte 1

LN: Indicates a Memory Request is an LN Read/Write, or LN completion.

TH: The presences of TLP Processing Hints

Attr[2:0]: Attribute,ordering type of IDO/Relaxed

TD: Presence of TLP digest in the form of a single DW

EP – Indicates the TLP is Poisoned

Length[9:0] – Length of data payload in DW

TLP data must be 4-byte aligned

for TLPs that do not contain or refer to data payloads, including Cpl, CplLk and Messages.

事务层的优先级控制:

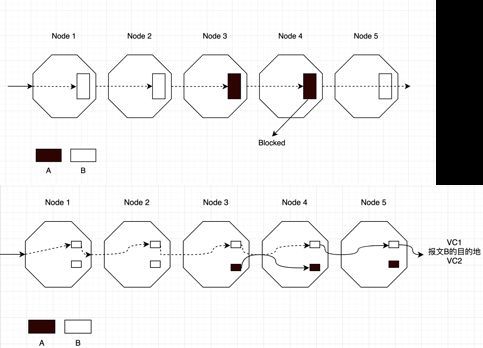

QoS: 传输类别和虚拟通道

传输分类: TC(Traffic class)

数据包被支配一个优先级

灵活的仲裁机制(任意、循环、加权轮询)

如在PC中,给视频流最高优先级保证足够带宽

通道虚拟化: VC(Virtual Channel)

允许多个独立的数据流复用同一条线路。虚拟通道拥有自己的缓冲资源

本质是一个缓冲Buffer

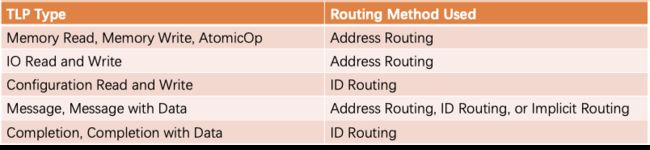

TLP的路由:

三种路由方法:

基于地址的路由. - Address Routing

基于ID的路由 - ID-Based Routing

隐式路由(Implicit). - Implicit Routing

流量控制:

从数据传输的角度看,网络中具有两类资源:

数据通路

数据缓冲

目的:

用于报文发送方与接收方之间的流量控制

发送方必须有足够的信用,才能发送报文

每次发送将消耗信用,接收方接收后,通过流控报文释放信用

每个虚通道要实现一套流控机制

包含Posted、Non-Posted和Completion 3类,每类又分报文头和负载

VC: 缓存到缓存之间的传递通路

VC和VC之间的数据传递,都需要实际的物理链路,所以称为“虚通路”

相同类型的报文一般使用同一个VC进行数据传输

PCIe中,一个TC只能对应一个VC

Credit-Based流量控制算法

N123

N123+

N23

数据链路层的内容放在下一节.