天之道,损有余而补不足,是故虚胜实,不足胜有余。作为一名技术人员一直奋斗在第一线,见证过很多从无到有,从小到大的各种基础架构系统、业务系统的发展。每次、每个阶段看技术问题总能发现不同的闪光点,了解越多感觉自己越无知。所以技术从业人员必须不断的学习,不断的提高自己。学而不思则罔,思而不学则殆。希望能通过一个系列的分享搭建起你我沟通的桥梁。

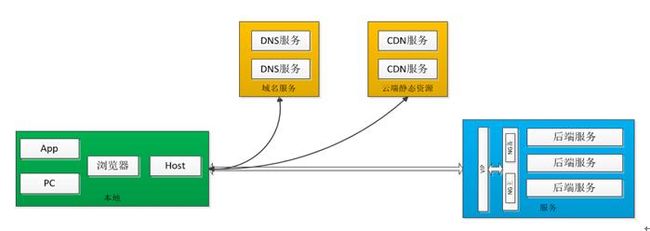

现代互联网技术分布式状态、分布式资源管理、分布式RPC、缓存、分布式数据库已经成为重要的技术基石。在各个基础架构系统、各个业务系统中扮演这重要的角色。本文先从缓存技术为切入点,希望能通过一个系列文章对缓存的技术进行分析与分享。当一个用户通过App或Pc访问某一个网站或服务时,一般情况一下都会直接或间接的使用多少次缓存呢?

带着这个问题我们简单来看一下,用户设备(必然有CPU)->浏览器->本地HOST->本地(DNS)->本地网络设备->网络传输协议->外部(DNS)->服务提供商(IP及机房)->防火墙及安全设备->负载均衡设备或LVS->NGNIX负载均衡->应用程序服务器->应用程序本地缓存->分布式资源管理->分布式缓存->分布式数据库。有多少次缓存在为用户提供服务呢?我们一起来分析一下。首先就是设备中的CPU,为什么是CPU?不管是用户设备还是服务器,核心的硬件设备就是CPU,它是指令的执行者和数据的加工者。

下面我们先走近CPU,看看CPU中的缓存是如何为用户及程序提供服务的。

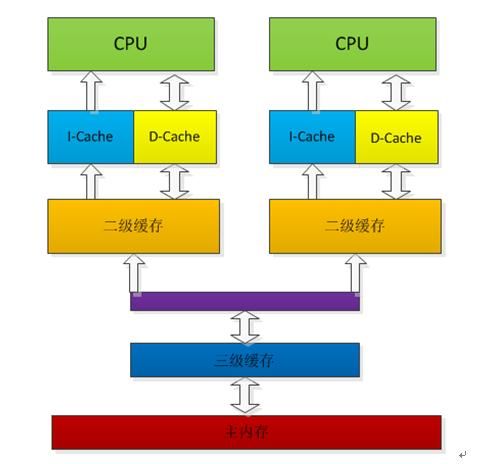

一、缓存的存储结构逻辑图:

二、L1 Cache(一级缓存)

一般来说,一级缓存可以分为一级数据缓存(Data Cache,D-Cache)是读写的,一级指令缓存(Instruction Cache,I-Cache),是只读的。

二者分别用来存放数据以及对执行这些数据的指令进行即时解码。

三、L2 Cache(二级缓存)

L2Cache(二级缓存)是CPU的第二层高速缓存,分内部和外部两种芯片。内部的芯片二级缓存运行速度与主频相同,而外部的二级缓存则只有主频的一半。

四、L3 Cache(三级缓存)

三级缓存是为读取二级缓存后未命中的数据设计的—种缓存,在拥有三级缓存的CPU中,只有约5%的数据需要从内存中调用,这进一步提高了CPU的效率。

五、内存访问:在缓存完全没命中的情况下,DRAM通道到每个槽的延迟平均为30~90ns。

六、MMU:它是中央处理器(CPU)中用来管理虚拟存储器、物理存储器的控制线路,同时也负责虚拟地址映射为物理地址,以及提供硬件机制的内存访问授权,多用户多进程操作系统。

缓存读取过程及效率:L1 cache命中时,访问时间为1~4个CPU周期,L1 cache不命中,L2 cache命中,访问时间为4~12个CPU周期,L2 cache不命中,L3 cache命中,访问时间为10~40个CPU周期,当要去内存中取单元时,访问时间可能就到30~100个CPU周期了。

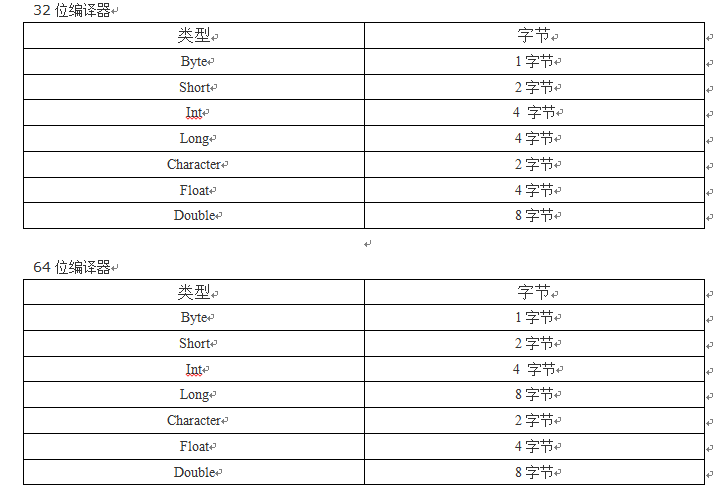

通过以上简要过程可以理解CPU指令及数据处理过程,在这个过程对于程序员来说需要注意哪些问题呢?缓存命中率、数据有效性(防止脏数据)、系统指令重排、数据一致性、数据块连续性、CPU指令上线文切换等。

1、缓存命中率:CPU读取数据会至上而下,通过各个缓存命中指令所需数据,从程序角度看对象调用尽量使用显示方式,这样可以增加指令与数据在缓存中的命中率及寻址空间。

2、数据有效性(防止脏数据):数据对象在使用完后尽量显示清空或回收,volatile及锁是双刃剑需要衡量开销。

3、系统指令重排:每种程序语言都有自己的规范,CPU为了更快、更优化的执行通常会对指令进行重排,当一段代码或程序被编写完成时,CPU并不一定能按照语言规范来执行。

4、数据一致:CPU为确保数据的一致性通常会使用FIFO策略、LRU策略、OPT置换策略,通过数据的回写确保数据在缓存中的一致性。

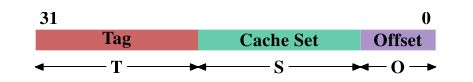

5、数据块连续性:CPU通过LINE、SET的数据结构来构建连续的缓存空间。

6、CPU指令上线文切换:CPU是高速运算单元,在程序执行的过程因为状态等待、数据等待、多线程、时钟、指令跳转等会进行指令切换。

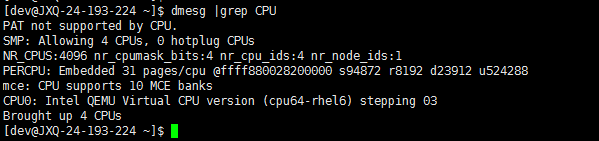

如我们在Linux主机或虚拟机上执行dmesg|grep CPU查看cpu相关信息时:

如图:

1、SMP:允许使用4个CPU,0个热插CPU。

2、NR_CPUS:CPU组合方式。

3、PERCPU:CPU变量副本配置。

4、MCE:CPU发现硬件错误时触发的异常及Bank寄存器。

5、Brought up4个CPU被触发。

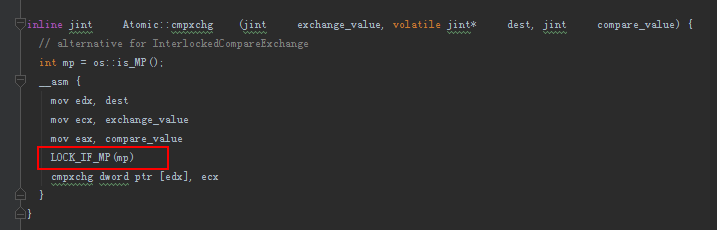

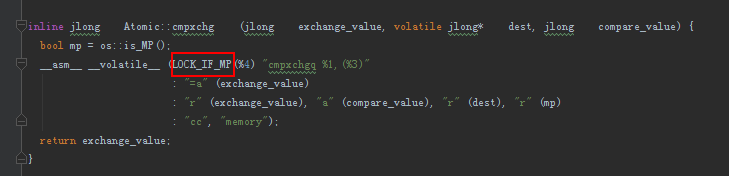

例如我们常用的CAS并发操作控制,sun.misc.Unsafe类的compareAndSwap()方法的源代码:

Windows_x86指令:

Linux_x86指令:

CPU看似是硬件但它是我们每一个程序、每一条指令的执行者。通过不断的指令、数据、时钟、寄存器等元器件,将复杂的程序语言转化成0、1进行输入、输出。了解一些基础的工作可以帮助我们编写效率更高的应用程序。