从 2008 年 12月 ARM 公司第一次 release Trustzone 技术白皮书,已经过去了十年。2013 年 Apple 推出了第一款搭载指纹解锁的 iPhone:iPhone 5s,用以保证指纹信息安全的 Secure Enclave 技术据分析深度定制了 ARM trustzone 架构,印象中这大概是 Trustzone 技术第一次走进大众视线。到如今 Trustzone 技术已经成为移动安全领域的重要基础技术,你也许不了解它的技术原理,但它一直默默为你守护你的指纹信息,账户密码等各种敏感数据。

在公司负责 Trustzone 相关开发的几年中,回答最多的问题大概就是“你能不能先给我解释一下 Trustzone 是什么”。这个问题我也问过自己很多遍,直到现在我还是会把 Arm Trustzone Security whitepaper 拿出来反复看,每次都会有一些新的体会。当初从老板手上接过开发任务,公司没有其他人接触过 Trustzone,经过几个月的摸黑抓瞎交出的初版代码现在看起来都觉得很好笑。再后来遇到各种 CPU hotplug,cache flush 等等各种奇怪问题,每次都是大型崩溃现场。一路艰难走来,越发觉得能够解决现有问题的是一家好公司,能够判断大势所趋,预测问题的出现并能够给出解决方案的才能成为一家伟大的公司。所以在我看来简言之:Trustzone 就是一种解决方案。

再加上多一些的修饰语就是: Trustzone 是 ARM 公司为了解决可能遇到的软硬件安全问题提出的一种硬件解决方案。基于 Trustzone 这种硬件架构设计的软硬件,能在很大程度和范围内保证系统的安全性,使软硬件破解都变得相对很困难。

我认为这套硬件架构的核心设计思想,关键词在于“隔离”。简单描述就是人为将系统运行环境划分为 TEE (Trusted Execution Environment) 和 REE ( Rich Execution Environment),所有的安全资源只能由 TEE 访问,而 REE 根本touch 不到。TEE 中运行的通常被认为是 trusted OS,一般为独立的 binary。REE 中运行的 rich OS 大多是指常用的 Linux 和 Android 操作系统。直观的例子就是 Android 系统下的各个应用是无法直接访问指纹信息的,只有切换到 Trusted OS 下才可以访问。当然这个过程:

- Android 应用如何完成指纹验证可以拿出来单独做一个大 topic;

- Trusted OS 通常由设备厂商提供,跟硬件设计强相关,无法由第三方更新 binary;

- 要做到第二条,secure boot 功能就必不可少。(所以说安全功能都是环环相扣缺一不可)

要实现这样一套硬件架构,首先需要SoC中的各个硬件模块都实现对 Trustzone 的支持,才能称之为完整的 security system。常见大致上需要以下几个模块:

1. Bus

这里涉及的总线分为两种,一种是 AMBA3 AXI system bus(系统总线),一种是 AMBA3 APB peripheral bus(外围总线)。

前面说到 trustzone 技术会将系统划分为两种模式:secure 和 Non-secure。而划分的基础就是 AXI 系统总线一条控制线的电平高低。简单来说,就是 ARM 为 AXI 总线每个信道的读写操作都新增了一个标记位:NS bit。主设备为Non-secure 状态时,发起读写请求,NS bit 必须置为高电平;主设备为 Secure 状态时,发起读写请求,NS bit 必须置为低电平。

APB 外围总线通过 AXI-to-APB bridge 连接到系统总线,可以实现对外设的安全访问管控,这里的外设可以包括 interrupt controller,timer 等。

2. Processor

在 ARM core 的 technical reference manual 中,对 Trustzone 技术的支持一般被描述为 security extension。目前主流使用的 ARM core architecture 主要是 ARMv7 和 ARMv8。两种架构下的 CPU security extension 差异巨大,但总的来说,都是将 CPU 的每个 core 都虚拟出 secure 和 Non-secure 两种模式,当 core 为 Non-secure 时,Secure Configuration Register 的 NS bit 置为 1,为 secure 模式时,NS bit 置为 0。NS bit 默认为 0,也就是说,CPU 上电后每个 core 都默认为 secure mode。

除此之外,两种模式下 CPU core 对中断的处理,MMU / Cache访问,Timer,Debug 等等都做了相应的安全扩展,每个 model 都值得详细研究。

3. Interrupt controller

常见支持 Trustzone 的 interrupt controller IP 有 PL390,GIC-400,GIC-500,简单说就是能够区分 secure interrupt 和 Non-secure interrupt,实现对中断处理的隔离。同样 GIC 的不同版本对 security extension 的设计也不尽相同,常见的 GICv2 和 GICv3 就有着较大差异,同样值得详细说明。

4. Trustzone Address Space Controller

CPU core MMU 的 security extension 主要是针对 CPU 内存空间的安全访问控制,而 TZASC 主要是针对 DRAM。TZASC通常布置在 CPU 和 DRAM controller 之间,通过新增一条地址线表示 NS bit,可以将 DRAM 划分为 secure CPU core 可访问区域和 Non-secure CPU core 可访问区域,实现 DRAM 的隔离。常见的 TZASC IP 有 PL-380 和 TZC-400。针对 on-SoC 的静态内存(ROM 和 SRAM)的区域划分,则需要通过使用 Trustzone Memory Adapter (TZMA)来完成。

5. Trustzone Protection Controller

挂在 AXI-to-APB bridge 上,用以区分外设是 secure 还是 Non-secure。

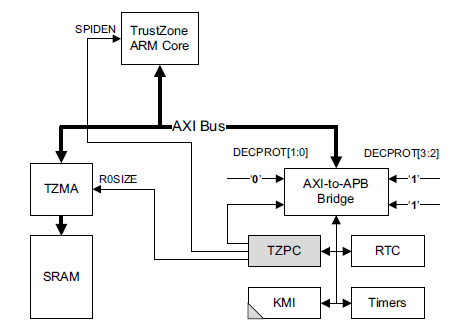

这样介绍可能有些抽象,用白皮书里示例图做个简单说明:

上图中,支持 Trustzone 的 ARM core 通过 AXI 总线和 TZMA,SRAM,AXI-to-APB bridge 相连,其中 AXI-to-APB bridge 上挂了四个外设,TZPC 永远配置为 secure peripheral,timer 和 RTC 是 Non-secure peripheral,而 KMI (Keyboard and Mouse Interface)为 secure peripheral 还是 Non-secure peripheral 是 software programmable。KMI secure 和 Non-secure 的切换,由软件配置 TZPC 来完成,而由于 TZPC always 是 secure 外设,所以 TZPC 的配置只能在 CPU 是 secure mode 下才能实现。从软件层面来看,就是只有 Trusted OS 才能配置 TZPC。那么将 Keyboard 设置为 secure 的一个作用就是可以在安全环境下让用户输入密码。

同样,当有外设需要访问 DRAM 或者 SRAM 的 secure region 时,也需要通过 TZPC 实现对外设的控制。

所以说 Trustzone 技术的实现,并非某个单一模块的功能可以完成,需要参与到整个系统中的所有硬件模块共同协作才能实现一个安全的硬件系统。而 Trustzone 技术面世以来,也并非牢不可破,一方面 IC design 的方案各大厂商都不相同,另一方面 Trusted OS 由各家 OEM 或者第三方 Trustzone vendor 提供,软硬件的漏洞也不断被发现。因此独立的硬件安全单元近年渐成趋势,尤其是 Android 9.0 Keymaster 从对 Trustzone 的支持提升到对独立 Security Elements 的支持,让人感慨技术更新的迅速。然而回顾 Trustzone 技术的发展,还是觉得 ARM 公司的前瞻性和技术实力实在让人很是佩服。

附上系列链接:

ARM Trustzone 技术(一) 综述

ARM Trustzone 技术(二) ARMv7-A Processor modes & registers 的安全扩展

ARM Trustzone 技术 (三)ARMv7-A Exceptions & Interrupts Handling 的安全扩展