亚稳态相关:三种复位方式详解---同步复位/异步复位/异步复位同步释放

常见有三种复位方式:同步复位、异步复位、异步复位同步释放;本文对这几种复位方式进行介绍与分析,详细介绍了各种复位方式的优缺点,并在此基础上着重介绍了异步复位同步释放的工作机理与优势所在。

目录

一、同步复位

1、概念

2、Verilog描述

3、同步复位优缺点

二、异步复位

1、概念

2、Verilog描述

3、异步复位优缺点

三、异步复位同步释放

1、引入

2、原理分析1

3、原理分析2

4、Verilog描述以及仿真验证

四、参考文献

一、同步复位

1、概念

同步复位是指,复位信号只有在时钟上升沿到来时才有效。

2、Verilog描述

由同步复位的概念,即可知道其Verilog描述如下:

always@(posedge clk)

begin

if(!rst_n)

...

else

...

end3、同步复位优缺点

优点:

a、有利于仿真器的仿真;

b、可以使所设计的系统成为100%的同步时序电路,这便大大有利于时序分析,而且综合出来的fmax一般较高。

c、因为他只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺。

缺点:

a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时还要考虑,诸如:clk skew,组合逻辑路径延时,复位延时等因素。

b、由于大多数的逻辑器件的目标库内的DFF都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。

二、异步复位

1、概念

异步复位是指,只要复位信号有效即进行复位操作,而不管时钟上升沿是否到来。

2、Verilog描述

由异步复位的概念,即可知道其Verilog描述如下:

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

...

else

...

end3、异步复位优缺点

优点:

a、大多数目标器件库的DFF都有异步复位端口,因此采用异步复位可以节省资源。

b、设计相对简单。

c、异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。

缺点:

a、在复位信号释放(release)的时候容易出现问题。具体就是说:倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致亚稳态。

b、复位信号容易受到毛刺的影响。

三、异步复位同步释放

1、引入

由上述分析,可以看出同步复位和异步复位两种复位方式有利有弊。但总的来说,还是异步复位用的较多。因此如果改进异步复位电路,使其能避免传统异步复位的缺陷,就理应是一种推荐使用的合理复位方式---即异步复位同步释放;

2、原理分析1

异步复位缺点1:复位信号释放的时候容易出现亚稳态,导致输出异常。

恢复时间与去除时间:

恢复时间(Recovery time):与同步电路中的建立时间类似,是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,异步控制信号在时钟上升沿来临Trecovery时间就要保持稳定,如果保证不了这个最小恢复时间,也就是说“下个时钟沿”来临时,这个异步控制信号不能保证正常执行。

去除时间(Removal time):与同步电路中的保持时间类似,是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。这个时间的意义是,异步控制信号在时钟上升沿后仍需保持Tremoval的稳定时间,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近,那么依旧不能保证这一异步控制信号能正常执行。

解决思路1:

异步复位同步释放,即将复位信号的释放变为与时钟同步,这就避免了异步复位信号释放时和有效时钟沿距离过近的可能;(同步电路中经过STA分析等操作,可以保证复位信号同步释放沿满足恢复时间以及去除时间的要求)

input rst_n;

input clk;

output rst_n_s;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

rst_n_s <= 0;

else

rst_n_s <= 1;

end3、原理分析2

异步复位缺点2:复位信号容易受到毛刺的影响。

毛刺如何影响复位:

异步复位电路中,如果rst_n有一短暂有效期(毛刺),这样可能会导致复位不完全,系统出现混乱。

解决思路1的电路同样具有毛刺问题,如果如果rst_n有一短暂有效期(毛刺),虽然rst_n_s直到时钟上升沿来临时才无效,但是rst_n_s有效的持续时间仍无法保证,毛刺距离时钟上升沿比较近时,rst_n_s也会很快无效,导致复位不完全;测试如下:

测试文件:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: CLL guoliang

//

// Create Date: 2020/03/20 11:50:51

// Design Name:

// Module Name: rst_test_tsb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module rst_test_tsb(

);

reg clk;

reg rst_n;

wire rst_n_s;

initial

begin

clk = 1;

forever #10 clk = ~clk;

end

initial

begin

rst_n = 1;

#13 rst_n = 0;

#5 rst_n = 1;

end

rst_test Uinst(

.clk(clk),

.rst_n(rst_n),

.rst_n_s(rst_n_s)

);

endmodule

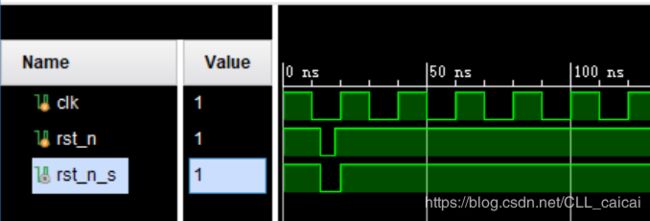

仿真结果:

可以看出,与之前分析一致,如果rst_n的毛刺距离时钟上升沿较近时,虽然 rst_n_s已经同步到时钟上升沿再释放,其也只能维持较短的有效时间;

解决思路:

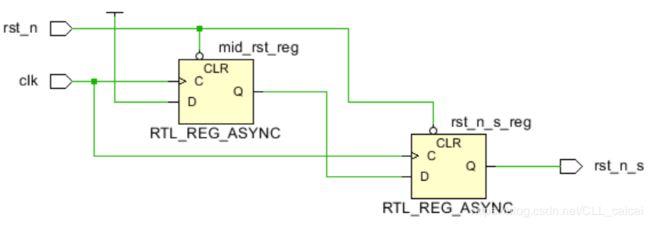

针对毛刺问题,给rst_n_s再添加一级时钟延迟,即可保证rst_n_s的有效时间 > 时钟周期,因而能够避免毛刺带来的复位不完全这一问题。

4、Verilog描述以及仿真验证

通过上述两个问题的分析与相应的解决办法,我们就能得到异步复位,同步释放的最终版本:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: CLL guoliang

//

// Create Date: 2020/03/20 11:49:24

// Design Name:

// Module Name: rst_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module rst_test(

input rst_n,

input clk,

output reg rst_n_s

);

reg mid_rst;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

rst_n_s <= 0;

mid_rst <= 0;

end

else

begin

mid_rst <= 1;

rst_n_s <= mid_rst;

end

end

endmodule

测试文件不变

仿真结果:

可以看出,与之前分析一致,最终版本的异步复位同步释放方式,很好的解决了同步释放以及避免毛刺导致复位不彻底这两个问题;

RTL电路如下:

四、参考文献

三种复位方式: 同步复位、异步复位、异步复位同步释放

异步复位、同步释放

FPGA复位——同步复位和异步复位

FPGA基础知识11(FPGA异步复位同步释放解析)