数字时钟计数器(Verilog HDL语言描述)(仿真和综合)

目录

前言

主题

Verilog HDL设计代码

测试代码

仿真波形

ISE中综合

RTL Schematic

Technology Schematic

前言

数字时钟计数器和我的前一篇博文:级联模60计数器(Verilog HDL语言描述)(仿真与综合)的级联思路几乎一样。

数字时钟计数器的秒、分用的是模60计数器,而时用的是模24计数器,所以呢,这篇博文可以先参考上两篇博文:

模24的8421BCD码计数器(Verilog HDL语言描述)(仿真与综合)

数字时钟计数器就是调用这两个模块组成的,思路我就不在写了,繁琐。直接看级联模60计数器就好了,反正都是级联的。

主题

Verilog HDL设计代码

//数字时钟计数器

module digital_clock(hour,min,sec,clk,rst_n,en);

input clk,rst_n,en;

output[7:0] hour, min, sec;

wire co_sec1,co_sec,co_min,co_min1;

counter60 u1(.clk(clk), .rst_n(rst_n), .en(en), .dout(sec), .co(co_sec1));

and u2(co_sec,en,co_sec1);

counter60 u3(.clk(clk), .rst_n(rst_n), .en(co_sec), .dout(min), .co(co_min1));

and u4(co_min,co_sec,co_min1);

counter24 u5(.clk(clk), .rst_n(rst_n), .en(co_min), .dout(hour));

endmodule

//模60计数器模块

module counter60(clk, rst_n, en, dout, co);

input clk, rst_n, en;

output co;

output [7:0] dout;

wire co10_1, co10, co6;

wire [3:0] dout10, dout6;

count10 U1(.clk(clk), .rst_n(rst_n), .en(en), .dout(dout10), .co(co10_1));

count6 U2(.clk(clk), .rst_n(rst_n), .en(co10), .dout(dout6), .co(co6));

and U3(co, co10, co6);

and U4(co10, en, co10_1);

assign dout = {dout6, dout10};

endmodule

//模10计数器

module count10(clk, rst_n, en, dout, co);

input clk, rst_n, en;

output co;

output [3:0] dout;

reg [3:0] dout;

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

dout <= 4'b0000;

else if(en == 1'b1)

begin

if(dout == 4'b1001)

dout <= 4'b0000;

else

dout <= dout + 1'b1;

end

else

dout <= dout;

end

assign co = dout[0] & dout[3];

endmodule

//模6计数器

module count6(clk, rst_n, en, dout, co);

input clk, rst_n, en;

output co;

output [3:0] dout;

reg [3:0] dout;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

dout <= 4'b0000;

else if(en == 1'b1)

begin

if(dout == 4'b0101)

dout <= 4'b0000;

else

dout <= dout + 1;

end

else

dout <= dout;

end

assign co = dout[0] & dout[2];

endmodule

//8421BCD码计数器,模24

module counter24(clk, rst_n, en, dout);

input clk, rst_n, en;

output[7:0] dout;

reg[7:0] dout;

always@(posedge clk or negedge rst_n) //异步复位

begin

if(!rst_n) //复位信号有效时,输出清零

dout <= 8'b00000000;

else if(en == 1'b0) //计数使能无效时,输出不变

dout <= dout;

else if( (dout[7:4] == 4'b0010)&&(dout[3:0] == 4'b0011) ) //计数达到23时,输出清零

dout <= 8'b00000000;

else if(dout[3:0] == 4'b1001) //低位达到9时,低位清零,高位加1

begin

dout[3:0] <= 4'b0000;

dout[7:4] <= dout[7:4] + 1'b1;

end

else //上述情况都没有发生,则高位不变,低位加1

begin

dout[7:4] <= dout[7:4];

dout[3:0] <= dout[3:0] + 1'b1;

end

end

endmodule

测试代码

//数字时钟计数器的测试代码

module digital_clock_tb;

reg clk,rst_n,en;

wire[7:0] hour,min,sec;

always

begin

#1 clk = ~clk;

end

initial

begin

clk = 1'b0;

rst_n = 1'b0;

en = 1'b0;

#3 rst_n = 1'b1; en = 1'b1;

end

digital_clock u0(.clk(clk),.rst_n(rst_n),.en(en),.hour(hour),.min(min),.sec(sec));

endmodule

我建议看完我的前几篇博文再看这篇,因为这篇博文的模块都是调用前面的,且我都疲惫了,懒着写注释了。

我的测试代码很简单,就是让它计数而已,计数看看对不对。

仿真波形

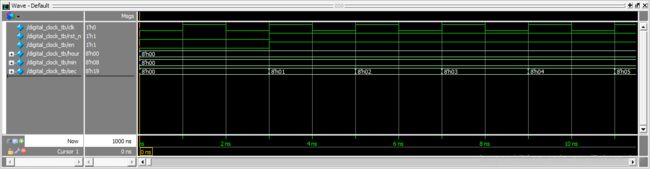

贴出来第一张是为了看开头部分仿真图

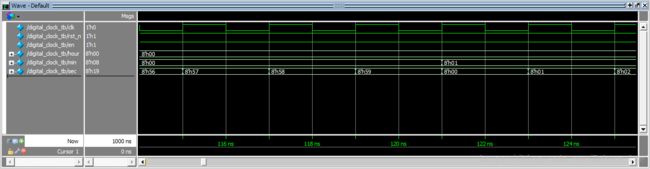

然后就是秒计数到59,分加1:

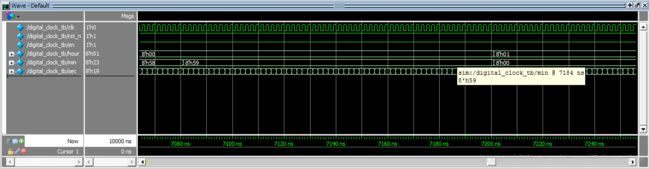

再者就是分计数到59,时加1:

可见,设计功能正确。

ISE中综合

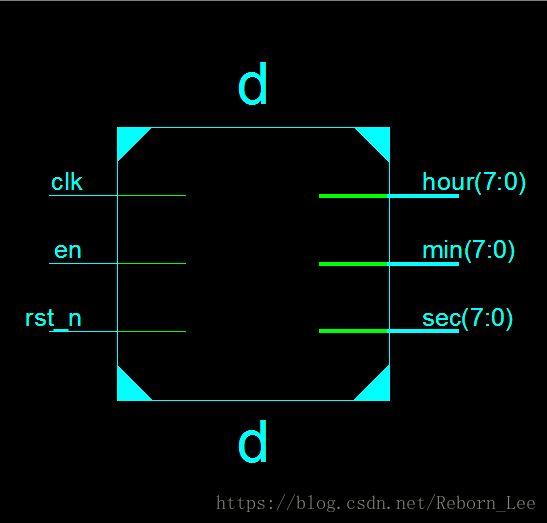

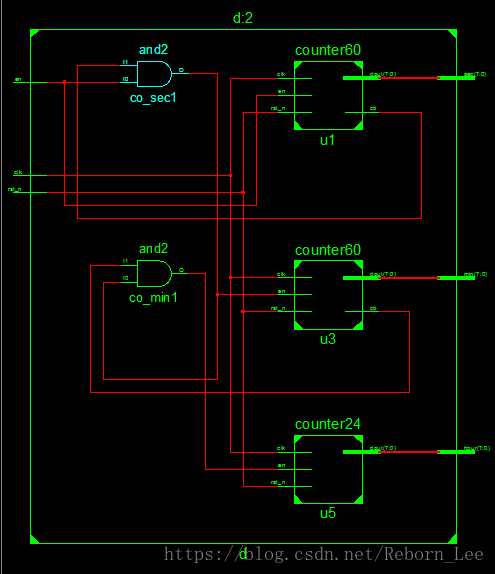

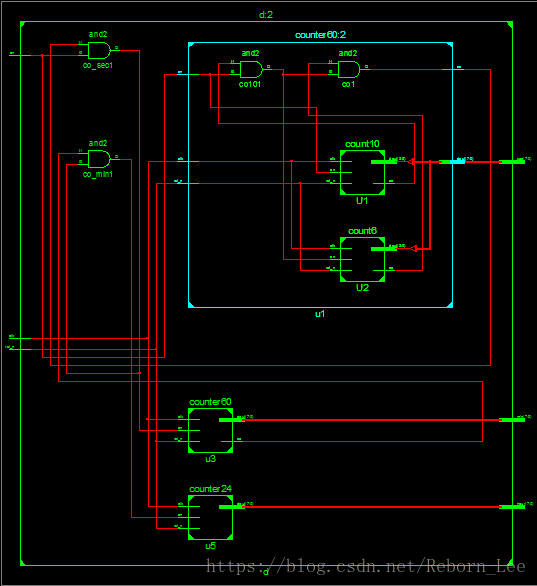

RTL Schematic

展开

再展开

可见,从这个过程中,知道一个大的模块是由各个小的模块组成的,不在赘述了。

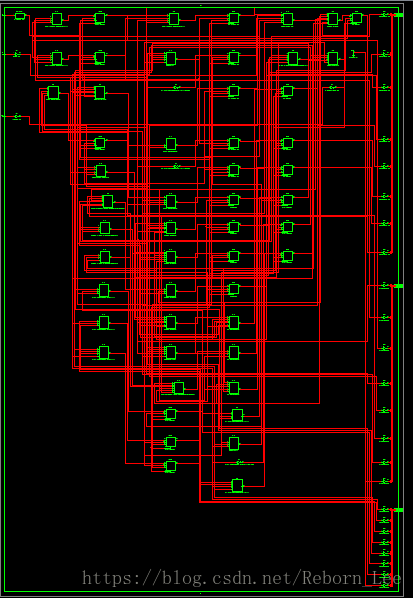

Technology Schematic

这个图是FPGA中的电路图,已经看不清楚了,没关系,仅供参考,也不是给你细看的,它体现了FPGA内部这个电路是如何构成的,是由FPGA的LUT以及其他原件,它特有的方式实现了各种电路,可见是很强大了。