米尔科技ZYNQ -Linux下的DMA驱动

一.目标

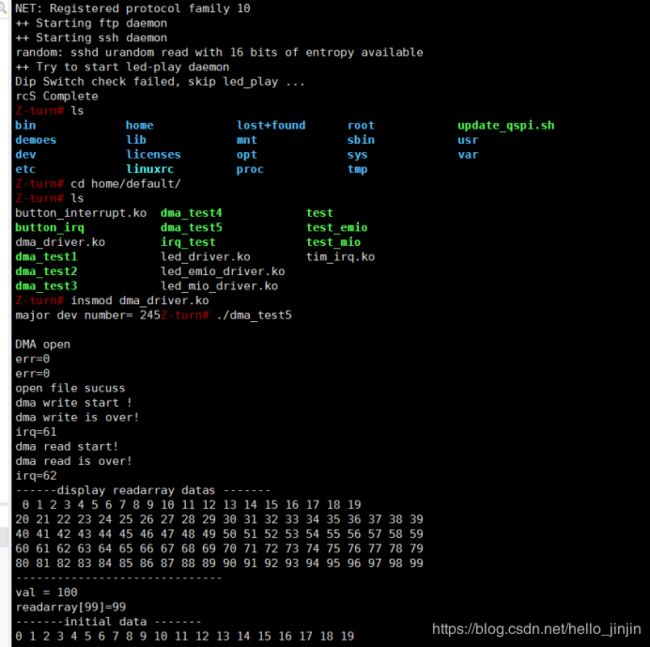

在米尔科技的z-turn板上实现linux下的DMA驱动,同时对DMA中断进行测试。

二.分析

ZYNQ的AXIDMA有Direct Register Mode和Scatter/Gather Mode,本文使用的是Direct Register Mode。

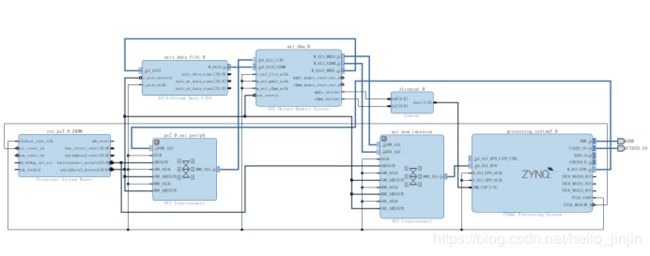

Vivado上PL端的构造如下图所示,开启了DMA中断(PL-PS中断)。对于AXI-DMA来说,CPU通过S_AXI_LITE得出DMA地址,通过GP接口与S_AXI_相连,用于写数据,通过HP接口读入数据。

AXI_DMA_0的物理地址为:0x4040_0000。

对于DMA的操作可以查看手册相关寄存器如下图所示。

这里就不一一说明每个寄存器的功能了,详情请查看手册或查看:

https://www.cnblogs.com/yiwenbo/p/10500060.html

三.代码实现

①驱动代码

#include ②测试代码

#include ③Makefile文件

KDIR = /home/python/Hard_disk_21G/04-Linux_Source/Kernel/linux-xlnx

PWD := $(shell pwd)

CC = $(CROSS_COMPILE)gcc

ARCH =arm

MAKE =make

obj-m:=dma_driver.o

modules:

$(MAKE) -C $(KDIR) ARCH=$(ARCH) CROSS_COMPLE=$(CROSS_COMPLE) M=$(PWD) modules

clean:

make -C $(KDIR) ARCH=$(ARCH) CROSS_COMPLE=$(CROSS_COMPLE) M=$(PWD) clean