- FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)

阿牛的药铺

算法移植部署fpga开发verilog

FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)引言:为什么这个FPGA入门路线能帮你快速上岗?本文设计了一条**"Verilog语法→工具链操作→光学项目实战→岗位技能对标"的阶梯式学习路径。不同于泛泛而谈的FPGA教程,我们聚焦光学类产品开发**核心能力(时序接口设计、图像处理算法移植、高速接口应用),通过3个递进式项目(从LED闪烁到图像边缘检测),

- PyTorch & TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)

阿牛的药铺

算法移植部署pytorchtensorflowfpga开发

PyTorch&TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)引言:为什么算法移植工程师必须掌握框架基础?针对光学类产品算法FPGA移植岗位需求(如可见光/红外图像处理),深度学习框架是算法落地的"桥梁"——既要用PyTorch/TensorFlow验证算法可行性,又要将训练好的模型(如CNN、目标检测)转换为FPGA可部署的格式(ONNX、TFLite)。本文采用"

- FPGA 设计中的 “Create HDL Wrapper“ 和 “Generating Output Products“ 的区别

行者..................

fpga开发

CreateHDLWrapper(创建HDL包装器)目的:为顶层设计模块(通常是BlockDesign/IPIntegrator设计)创建一个HDL包装文件功能:将图形化/框图设计的BlockDesign转换为可综合的HDL代码(Verilog或VHDL)创建一个顶层模块,将所有IP核和连接实例化使用场景:当使用IPIntegrator创建BlockDesign后需要将图形化设计转换为HDL代码以

- STM32与FPGA用FMC进行通讯

weixin_43554366

单片机stm32fpga物联网人工智能

stm32正常按读写SDRAM进行配置,FPGA进行信号采集。FPGA信号采集发现SDWNE是高但H7手册上时序显示是低,造成无法像FPGA模拟的SDRAM无法写入数据FPGA采集信号应该在时钟下降沿,上升沿采集,数据会发生错误。

- Xilinx Vivado开发环境快速导出hdf文件(bat批处理)

XilinxFPGA使用Vivado开发环境创建MicroBlaze软核或ZYNQPS侧SDK逻辑工程时,需要FPGA侧搭建的硬件平台文件,即hdf文件,常规方式是编译完成生成bit流文件后,通过File->Export->ExportHardware菜单来导出,在弹出的菜单再选择要导出的路径和文件名称等,这个过程比较繁琐,通过观察TCL终端窗口:update_compile_order-file

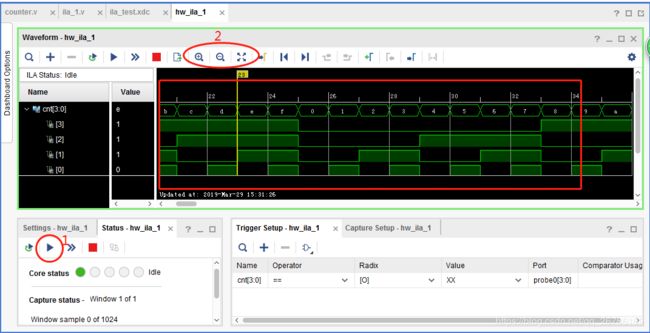

- Xilinx系FPGA学习笔记(三)Vivado的仿真及ILA使用

贾saisai

FPGA学习fpga开发学习笔记

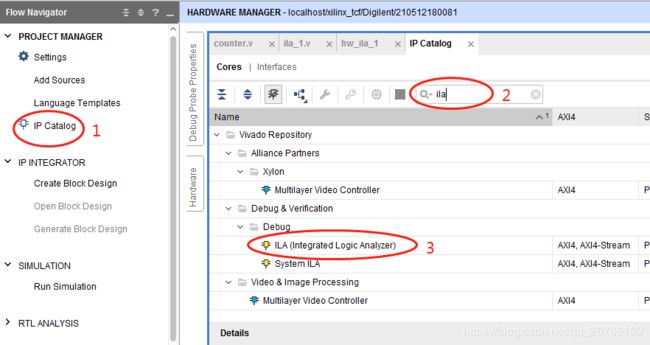

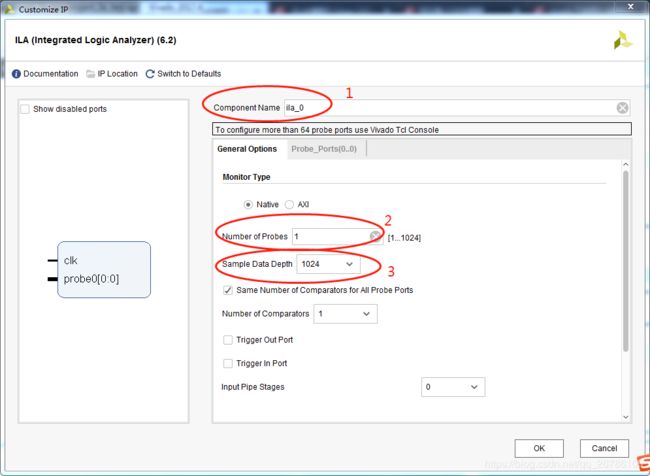

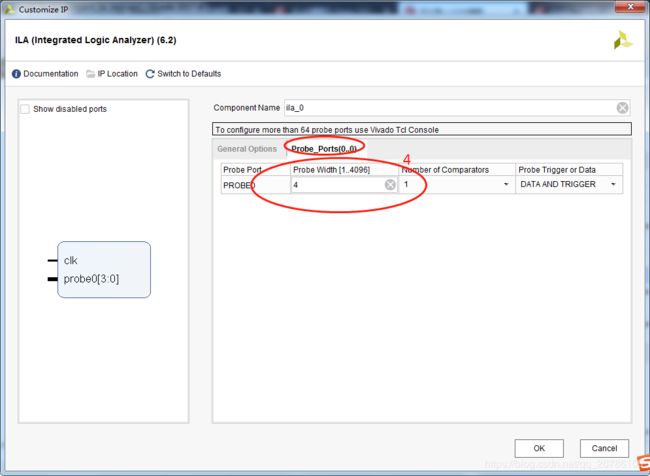

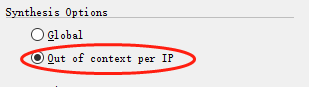

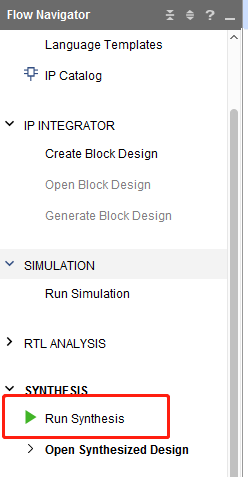

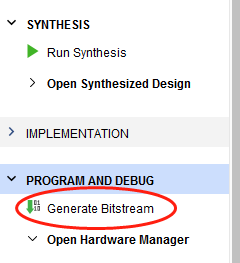

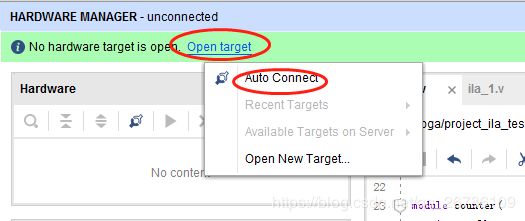

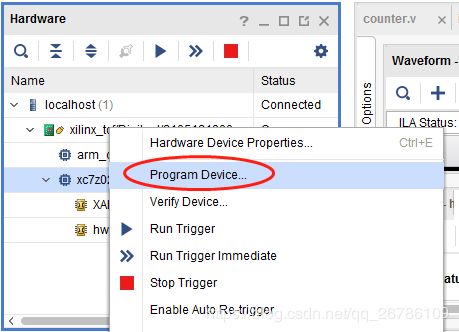

系列文章目录文章目录系列文章目录前言仿真验证(类似modelsim)ILA在线调试工具添加ILAILA的例化ILA的使用前言接着学习vivado的使用方法仿真验证(类似modelsim)首先类似添加.v文件的方法,在File-AddSource中选择Addorcreatesimulationsources或者直接在Sources里面选就行然后就编写testbench,类似之前介绍的modelsim

- FPGA 47 ,MIG 内存接口生成器深度解析( FPGA 中的 MIG 技术 )

北城笑笑

fpga开发fpga

目录前言一、基础理论1.1MIG介绍1.2结构框架1.2.1主要模块①用户接口层(UserInterfaceLayer)②控制逻辑层(ControLogicLayer)③校准逻辑(CalibrationLogic)④初始化与时序控制(Initialization&TimingControl)⑤物理层接口(PHY–PhysicalLayer)⑥IO引脚驱动(引脚分配与IO配置:Pinout&IOSt

- 基于FPGA的数字密码锁

阿智605

fpga开发notepad++

基于FPGA的数字密码锁顶层文件modulelock(inputclk,//时钟inputrst_n,//复位input[3:0]number_in,//输入inputkey_open1,inputkey_lock1,//inputkey_reset1,outputbeep,//蜂鸣器outputlock_flag,//锁标志位output[3:0]dtube_cs_n,//7段数码管位选信号ou

- 基于FPGA的设计:简易电子密码锁嵌入式实现

程序员杨弋

嵌入式开发fpga开发嵌入式

简介:本文介绍了如何使用FPGA(现场可编程逻辑门阵列)来设计和实现一款简易的电子密码锁。电子密码锁是一种常见的安全访问控制系统,通过输入正确的密码来解锁。嵌入式系统采用FPGA作为核心处理器,结合适当的外设和编程逻辑,能够实现密码输入、验证和控制功能。本文将详细介绍电子密码锁的设计和源代码。设计原理:输入设备:本设计采用数字键盘作为密码输入设备。数字键盘通过FPGA的GPIO(通用输入输出)引脚

- 多通路fpga 通信_FMC与FPGA双口ram通讯

weixin_39796752

多通路fpga通信

硬件环境:ARM+FPGA通过FMC互联,STM32F767和EP4CE15F23I7FMC设置,STM的系统时钟HCLK为216MHz1/*FMCinitializationfunction*/2voidMX_FMC_Init(void)3{4FMC_NORSRAM_TimingTypeDefTiming;56/**PerformtheNOR1memoryinitializationsequen

- [硬件接口]HDMI和DP 区别

DisplayPort和HDMI在FPGA应用场景的实现使用与区别概述DisplayPort(DP)和HDMI是两种主流的数字音视频接口,广泛应用于视频传输场景。在FPGA(现场可编程门阵列)应用中,DP和HDMI常用于视频处理、显示驱动和高带宽数据传输。本文档比较两者在FPGA实现中的使用方式、应用场景及主要区别,并以Markdown格式呈现。1.FPGA实现概述1.1DisplayPort在F

- [FPGA工具]FPGA 文件格式转换工具

S&Z3463

FPGA开发工具fpga开发

SZFPGA文件格式转换工具概述SZFPGA文件格式转换工具(版本V1.0.0)是一款专为FPGA文件格式转换设计的工具,旨在帮助用户将基于Vivado的FPGA文档格式转换为适用于XilinxVivado工具链的格式。本工具支持多种FPGA文档格式的转换,包括BIT转BIN、BIT转MCS、MCS转BIN以及SPIFlash加载等功能。本文档将详细介绍工具的主要功能、使用需求、转换要求、SPI使

- [FPGA AXI IP] AXI Crossbar

AXICrossbarIP详细介绍概述AXICrossbar是属于AXIInterconnectIPSuite的一部分,专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过交叉开关(Crossbar)架构实现高效的数据路由,支持多主多从的点对点连接,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联

- [AXI] AXI Interconnect

AXIInterconnectIP详细介绍概述AXIInterconnect专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过模块化架构实现高效的数据路由、协议转换、数据宽度转换和时钟域转换,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联的场景,如多核处理器系统、视频处理、网络通信和硬件加速器

- [FPGA Video IP] Video Processing Subsystem

S&Z3463

FPGAVideoIPfpga开发tcp/ip网络协议Video

XilinxVideoProcessingSubsystemIP(PG231)详细介绍概述XilinxLogiCORE™IPVideoProcessingSubsystem(VPSS)(PG231)是一个高度可配置的视频处理模块,设计用于在单一IP核中集成多种视频处理功能,包括缩放(Scaling)、去隔行(Deinterlacing)、颜色空间转换(ColorSpaceConversion,CS

- 基于FPGA的二维FFT实现

廉连曼

基于FPGA的二维FFT实现【下载地址】基于FPGA的二维FFT实现本项目提供了一种基于FPGA的高效二维FFT实现方案,专为数字信号处理和图像处理领域设计。通过并行使用两个一维FFT单元,本方案显著提升了二维FFT变换的计算效率,并基于Xilinx的FFTIP核,确保易于集成到其他FPGA设计中。该方案适用于各类频谱分析场景,尤其适合图像处理系统。经过Verilog编程和Modelsim仿真测试

- FPGA电子系统设计项目实战VHDL语言第2版王振红:深入掌握FPGA设计

姜奇惟Sparkling

FPGA电子系统设计项目实战VHDL语言第2版王振红:深入掌握FPGA设计【下载地址】FPGA电子系统设计项目实战VHDL语言第2版王振红这是一本专注于FPGA电子系统设计的实战指南,适合初学者和进阶开发者。全书共11章,从FPGA设计基础到VHDL语言应用,再到综合电子系统设计实例,内容全面且实用。通过深入浅出的讲解,读者不仅能掌握FPGA设计方法,还能具备实际应用能力。书中详细介绍了Quart

- 基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码

基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码【下载地址】基于FPGA的Verilog电子密码锁设计资源文件基于FPGA和Verilog语言设计的电子密码锁项目,提供完整的硬件设计原理图、Verilog代码、仿真波形图和硬件描述文档。通过FPGA的可编程特性,实现密码设置、验证及锁定功能,适合学术研究、教学演示或个人兴趣学习。项目文件清晰,包含详细的使用说明,帮助用户快速

- 【FFT】基于FPGA的FFT傅里叶变换和相位计算系统设计

fpga和matlab

★FPGA项目经验板块19:信号发生器fpga开发FFT相位计算

1.软件版本ISE14.7,modeslimSE,10.1c2.系统仿真与分析第1步:信号源的产生主要通过rom将产生的数据保存到rom中,然后,我们再仿真的时候调用即可。这个部分仿真效果如下所示,你给的程序中,这个部分主要有两个数据源,一个是1025,一个是N为1024,我们这里分别将这两个数据量化之后保存到rom中,仿真如下所示:

- 基于FPGA的快速傅里叶变换(FFT)设计在嵌入式系统中的应用

风吹麦很

fpga开发嵌入式

基于FPGA的快速傅里叶变换(FFT)设计在嵌入式系统中的应用快速傅里叶变换(FastFourierTransform,FFT)是一种重要的信号处理算法,在许多领域中都得到广泛的应用,例如通信系统、雷达技术、图像处理等。为了提高FFT的计算性能和实时性,将其设计为硬件加速器常常是一个明智的选择。本文将介绍基于现场可编程门阵列(Field-ProgrammableGateArray,FPGA)的FF

- FPGA电子系统设计项目实战 VHDL语言 第2版 王振红

幸刚磊Thomas

FPGA电子系统设计项目实战VHDL语言第2版王振红【下载地址】FPGA电子系统设计项目实战VHDL语言第2版王振红这是一本专注于FPGA电子系统设计的实战指南,适合初学者和进阶开发者。全书共11章,从FPGA设计基础到VHDL语言应用,再到综合电子系统设计实例,内容全面且实用。通过深入浅出的讲解,读者不仅能掌握FPGA设计方法,还能具备实际应用能力。书中详细介绍了QuartusⅡ工具的使用、VH

- xilinx fpga芯片的结温

hahaha6016

硬件设计fpga开发

xilinxfpga芯片的结温,结温这个含义是啥1.“结温”是半导体器件(比如XilinxFPGA芯片)常用的一个术语,全称是“结温”(JunctionTemperature),指的是芯片内部晶体管结点(PN结)的温度2.结温是芯片内部最关键的温度点,代表晶体管内部结点的实际温度,通常比芯片表面的温度或者散热器的温度要高。3.结温对芯片性能、稳定性和寿命影响很大。如果结温过高,芯片可能会出现性能下

- XILINX FPGA如何做时序分析和时序优化?

InnoLink_1024

FPGAVerilogRTL设计fpga开发

时序分析和时序优化是FPGA开发流程中关键步骤,确保设计在目标时钟频率下正确运行,避免时序违例(如建立时间或保持时间不足)。以下以XilinxKintex-7系列FPGA为例,详细介绍时序分析和时序优化的方法、工具、流程及实用技巧,结合Vivado工具链,力求清晰、全面且实用。1.时序分析概述时序分析的目的是验证FPGA设计是否满足时序约束,即信号在规定时间内正确传递,确保逻辑功能和性能。时序分析

- FPGA设计中的数据存储

cycf

FPGA之道fpga开发

文章目录FPGA设计中的数据存储为什么需要数据存储FPGA芯片内部的载体触发器查找表块存储FPGA芯片外部的资源RAM应用场合ROM特征简介实现载体应用场合FIFO特征简介FIFO使用小技巧之冗余法FIFO写接口缓存FIFO读接口缓存“冗余法”总结根据数据流的稳定性与存储操作的容错性,决定采用RAM模式还是FIFO模式STACK特征简介实现载体应用场合SummaryFPGA设计中的数据存储为什么需

- FDMA读写AXI BRAM交互:FPGA高速数据传输的核心技术

芯作者

D1:ZYNQ设计fpga开发

在图像处理系统中,当1080P视频流以每秒60帧的速度传输时,传统DMA每帧会浪费27%的带宽在地址管理上——而FDMA技术能将这些损失降至3%以内现代FPGA系统中,高效数据搬运往往是性能瓶颈的关键所在。当你在手机上流畅播放4K视频、在自动驾驶系统中实时处理激光雷达点云时,背后都依赖于FDMA(FlexibleDirectMemoryAccess)与AXIBRAM的高效交互技术。本文将深入探讨这

- XILINX Ultrascale+ Kintex系列FPGA的架构

InnoLink_1024

FPGARTL设计芯片fpga开发架构

Xilinx(现为AMD)KintexUltraScale+系列FPGA是基于16nmFinFET工艺的高性能、中等成本的现场可编程门阵列,专为高带宽、低功耗和成本效益的应用设计,广泛用于5G通信、数据中心、视频处理、航空航天等领域。以下详细介绍KintexUltraScale+系列FPGA的架构,结合其关键组件、特性和功能模块,并提供示例代码以展示时序约束的定义。1.KintexUltraSca

- 【技术架构解析】国产化双复旦微FPGA+飞腾D2000核心板架构

Future_Comtech

fpga开发fpga数据采集数据处理

本文就一款基于飞腾D2000核心板与两片高性能FPGA的国产化开发主板进行技术解析,包括系统架构、主要硬件模块、关键接口及软件环境,重点阐述各子系统间的数据路径与协同工作方式,旨在为行业内同类产品设计与应用提供参考。随着国产化要求的加速以及国产处理器芯片的性能不断提升,主板均基本可实现全国产化方案。本方案设计之初主要面向高速网络通信场景,提供高带宽、低延迟的数据收发能力。采用飞腾D20008核处理

- 前沿FPGA开发:技术与管理的有效结合

AI天才研究院

AI大模型企业级应用开发实战AgenticAI实战AI人工智能与大数据fpga开发ai

前沿FPGA开发:技术与管理的有效结合关键词:FPGA开发、技术管理、前沿技术、项目管理、资源优化摘要:本文深入探讨了前沿FPGA开发中技术与管理有效结合的重要性和具体方法。在FPGA技术不断发展的今天,单纯依靠技术或管理都难以实现项目的成功。通过将先进的FPGA技术与科学的管理理念相结合,能够提高开发效率、优化资源配置、降低成本并提升产品质量。文章详细阐述了FPGA开发的核心概念、相关算法原理、

- 基于 STM32+FPGA 的快速傅里叶频域图像在 TFT 中显示的设计与实现(项目资料)(ID:8)

嵌入式资料库

嵌入式项目合集fpga开发stm32嵌入式硬件单片机

目录摘要1绪论1.1研究背景与意义1.2国内外研究现状1.3研究内容与目标2系统方案设计2.1总体架构设计2.2硬件方案设计2.2.1主控模块选型2.2.2FPGA模块选型2.2.3TFT显示模块选型2.2.4通信方案设计2.3软件方案设计2.3.1FFT算法实现方案2.3.2频域图像渲染方案3硬件电路设计3.1STM32最小系统电路3.2FPGA模块电路3.3TFT显示模块电路3.4软件IIC通

- 【优秀文章】7月优秀文章推荐

优秀文章智能自主运动体与人工智能技术——环境感知、SLAM定位、路径规划、运动控制、多智能体协同作者:fpga和matlabC++之红黑树认识与实现作者:zzh_zao【手把手带你刷好题】–C语言基础编程题(十)作者:草莓熊Lotso飞算JavaAI:从“码农”到“代码指挥官”的终极进化论作者:可涵不会debug前端网页开发学习(HTML+CSS+JS)有这一篇就够!作者:一颗小谷粒

- windows下源码安装golang

616050468

golang安装golang环境windows

系统: 64位win7, 开发环境:sublime text 2, go版本: 1.4.1

1. 安装前准备(gcc, gdb, git)

golang在64位系

- redis批量删除带空格的key

bylijinnan

redis

redis批量删除的通常做法:

redis-cli keys "blacklist*" | xargs redis-cli del

上面的命令在key的前后没有空格时是可以的,但有空格就不行了:

$redis-cli keys "blacklist*"

1) "blacklist:12:

[email protected]

- oracle正则表达式的用法

0624chenhong

oracle正则表达式

方括号表达示

方括号表达式

描述

[[:alnum:]]

字母和数字混合的字符

[[:alpha:]]

字母字符

[[:cntrl:]]

控制字符

[[:digit:]]

数字字符

[[:graph:]]

图像字符

[[:lower:]]

小写字母字符

[[:print:]]

打印字符

[[:punct:]]

标点符号字符

[[:space:]]

- 2048源码(核心算法有,缺少几个anctionbar,以后补上)

不懂事的小屁孩

2048

2048游戏基本上有四部分组成,

1:主activity,包含游戏块的16个方格,上面统计分数的模块

2:底下的gridview,监听上下左右的滑动,进行事件处理,

3:每一个卡片,里面的内容很简单,只有一个text,记录显示的数字

4:Actionbar,是游戏用重新开始,设置等功能(这个在底下可以下载的代码里面还没有实现)

写代码的流程

1:设计游戏的布局,基本是两块,上面是分

- jquery内部链式调用机理

换个号韩国红果果

JavaScriptjquery

只需要在调用该对象合适(比如下列的setStyles)的方法后让该方法返回该对象(通过this 因为一旦一个函数称为一个对象方法的话那么在这个方法内部this(结合下面的setStyles)指向这个对象)

function create(type){

var element=document.createElement(type);

//this=element;

- 你订酒店时的每一次点击 背后都是NoSQL和云计算

蓝儿唯美

NoSQL

全球最大的在线旅游公司Expedia旗下的酒店预订公司,它运营着89个网站,跨越68个国家,三年前开始实验公有云,以求让客户在预订网站上查询假期酒店时得到更快的信息获取体验。

云端本身是用于驱动网站的部分小功能的,如搜索框的自动推荐功能,还能保证处理Hotels.com服务的季节性需求高峰整体储能。

Hotels.com的首席技术官Thierry Bedos上个月在伦敦参加“2015 Clou

- java笔记1

a-john

java

1,面向对象程序设计(Object-oriented Propramming,OOP):java就是一种面向对象程序设计。

2,对象:我们将问题空间中的元素及其在解空间中的表示称为“对象”。简单来说,对象是某个类型的实例。比如狗是一个类型,哈士奇可以是狗的一个实例,也就是对象。

3,面向对象程序设计方式的特性:

3.1 万物皆为对象。

- C语言 sizeof和strlen之间的那些事 C/C++软件开发求职面试题 必备考点(一)

aijuans

C/C++求职面试必备考点

找工作在即,以后决定每天至少写一个知识点,主要是记录,逼迫自己动手、总结加深印象。当然如果能有一言半语让他人收益,后学幸运之至也。如有错误,还希望大家帮忙指出来。感激不尽。

后学保证每个写出来的结果都是自己在电脑上亲自跑过的,咱人笨,以前学的也半吊子。很多时候只能靠运行出来的结果再反过来

- 程序员写代码时就不要管需求了吗?

asia007

程序员不能一味跟需求走

编程也有2年了,刚开始不懂的什么都跟需求走,需求是怎样就用代码实现就行,也不管这个需求是否合理,是否为较好的用户体验。当然刚开始编程都会这样,但是如果有了2年以上的工作经验的程序员只知道一味写代码,而不在写的过程中思考一下这个需求是否合理,那么,我想这个程序员就只能一辈写敲敲代码了。

我的技术不是很好,但是就不代

- Activity的四种启动模式

百合不是茶

android栈模式启动Activity的标准模式启动栈顶模式启动单例模式启动

android界面的操作就是很多个activity之间的切换,启动模式决定启动的activity的生命周期 ;

启动模式xml中配置

<activity android:name=".MainActivity" android:launchMode="standard&quo

- Spring中@Autowired标签与@Resource标签的区别

bijian1013

javaspring@Resource@Autowired@Qualifier

Spring不但支持自己定义的@Autowired注解,还支持由JSR-250规范定义的几个注解,如:@Resource、 @PostConstruct及@PreDestroy。

1. @Autowired @Autowired是Spring 提供的,需导入 Package:org.springframewo

- Changes Between SOAP 1.1 and SOAP 1.2

sunjing

ChangesEnableSOAP 1.1SOAP 1.2

JAX-WS

SOAP Version 1.2 Part 0: Primer (Second Edition)

SOAP Version 1.2 Part 1: Messaging Framework (Second Edition)

SOAP Version 1.2 Part 2: Adjuncts (Second Edition)

Which style of WSDL

- 【Hadoop二】Hadoop常用命令

bit1129

hadoop

以Hadoop运行Hadoop自带的wordcount为例,

hadoop脚本位于/home/hadoop/hadoop-2.5.2/bin/hadoop,需要说明的是,这些命令的使用必须在Hadoop已经运行的情况下才能执行

Hadoop HDFS相关命令

hadoop fs -ls

列出HDFS文件系统的第一级文件和第一级

- java异常处理(初级)

白糖_

javaDAOspring虚拟机Ajax

从学习到现在从事java开发一年多了,个人觉得对java只了解皮毛,很多东西都是用到再去慢慢学习,编程真的是一项艺术,要完成一段好的代码,需要懂得很多。

最近项目经理让我负责一个组件开发,框架都由自己搭建,最让我头疼的是异常处理,我看了一些网上的源码,发现他们对异常的处理不是很重视,研究了很久都没有找到很好的解决方案。后来有幸看到一个200W美元的项目部分源码,通过他们对异常处理的解决方案,我终

- 记录整理-工作问题

braveCS

工作

1)那位同学还是CSV文件默认Excel打开看不到全部结果。以为是没写进去。同学甲说文件应该不分大小。后来log一下原来是有写进去。只是Excel有行数限制。那位同学进步好快啊。

2)今天同学说写文件的时候提示jvm的内存溢出。我马上反应说那就改一下jvm的内存大小。同学说改用分批处理了。果然想问题还是有局限性。改jvm内存大小只能暂时地解决问题,以后要是写更大的文件还是得改内存。想问题要长远啊

- org.apache.tools.zip实现文件的压缩和解压,支持中文

bylijinnan

apache

刚开始用java.util.Zip,发现不支持中文(网上有修改的方法,但比较麻烦)

后改用org.apache.tools.zip

org.apache.tools.zip的使用网上有更简单的例子

下面的程序根据实际需求,实现了压缩指定目录下指定文件的方法

import java.io.BufferedReader;

import java.io.BufferedWrit

- 读书笔记-4

chengxuyuancsdn

读书笔记

1、JSTL 核心标签库标签

2、避免SQL注入

3、字符串逆转方法

4、字符串比较compareTo

5、字符串替换replace

6、分拆字符串

1、JSTL 核心标签库标签共有13个,

学习资料:http://www.cnblogs.com/lihuiyy/archive/2012/02/24/2366806.html

功能上分为4类:

(1)表达式控制标签:out

- [物理与电子]半导体教材的一个小问题

comsci

问题

各种模拟电子和数字电子教材中都有这个词汇-空穴

书中对这个词汇的解释是; 当电子脱离共价键的束缚成为自由电子之后,共价键中就留下一个空位,这个空位叫做空穴

我现在回过头翻大学时候的教材,觉得这个

- Flashback Database --闪回数据库

daizj

oracle闪回数据库

Flashback 技术是以Undo segment中的内容为基础的, 因此受限于UNDO_RETENTON参数。要使用flashback 的特性,必须启用自动撤销管理表空间。

在Oracle 10g中, Flash back家族分为以下成员: Flashback Database, Flashback Drop,Flashback Query(分Flashback Query,Flashbac

- 简单排序:插入排序

dieslrae

插入排序

public void insertSort(int[] array){

int temp;

for(int i=1;i<array.length;i++){

temp = array[i];

for(int k=i-1;k>=0;k--)

- C语言学习六指针小示例、一维数组名含义,定义一个函数输出数组的内容

dcj3sjt126com

c

# include <stdio.h>

int main(void)

{

int * p; //等价于 int *p 也等价于 int* p;

int i = 5;

char ch = 'A';

//p = 5; //error

//p = &ch; //error

//p = ch; //error

p = &i; //

- centos下php redis扩展的安装配置3种方法

dcj3sjt126com

redis

方法一

1.下载php redis扩展包 代码如下 复制代码

#wget http://redis.googlecode.com/files/redis-2.4.4.tar.gz

2 tar -zxvf 解压压缩包,cd /扩展包 (进入扩展包然后 运行phpize 一下是我环境中phpize的目录,/usr/local/php/bin/phpize (一定要

- 线程池(Executors)

shuizhaosi888

线程池

在java类库中,任务执行的主要抽象不是Thread,而是Executor,将任务的提交过程和执行过程解耦

public interface Executor {

void execute(Runnable command);

}

public class RunMain implements Executor{

@Override

pub

- openstack 快速安装笔记

haoningabc

openstack

前提是要配置好yum源

版本icehouse,操作系统redhat6.5

最简化安装,不要cinder和swift

三个节点

172 control节点keystone glance horizon

173 compute节点nova

173 network节点neutron

control

/etc/sysctl.conf

net.ipv4.ip_forward =

- 从c面向对象的实现理解c++的对象(二)

jimmee

C++面向对象虚函数

1. 类就可以看作一个struct,类的方法,可以理解为通过函数指针的方式实现的,类对象分配内存时,只分配成员变量的,函数指针并不需要分配额外的内存保存地址。

2. c++中类的构造函数,就是进行内存分配(malloc),调用构造函数

3. c++中类的析构函数,就时回收内存(free)

4. c++是基于栈和全局数据分配内存的,如果是一个方法内创建的对象,就直接在栈上分配内存了。

专门在

- 如何让那个一个div可以拖动

lingfeng520240

html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/1999/xhtml

- 第10章 高级事件(中)

onestopweb

事件

index.html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/

- 计算两个经纬度之间的距离

roadrunners

计算纬度LBS经度距离

要解决这个问题的时候,到网上查了很多方案,最后计算出来的都与百度计算出来的有出入。下面这个公式计算出来的距离和百度计算出来的距离是一致的。

/**

*

* @param longitudeA

* 经度A点

* @param latitudeA

* 纬度A点

* @param longitudeB

*

- 最具争议的10个Java话题

tomcat_oracle

java

1、Java8已经到来。什么!? Java8 支持lambda。哇哦,RIP Scala! 随着Java8 的发布,出现很多关于新发布的Java8是否有潜力干掉Scala的争论,最终的结论是远远没有那么简单。Java8可能已经在Scala的lambda的包围中突围,但Java并非是函数式编程王位的真正觊觎者。

2、Java 9 即将到来

Oracle早在8月份就发布

- zoj 3826 Hierarchical Notation(模拟)

阿尔萨斯

rar

题目链接:zoj 3826 Hierarchical Notation

题目大意:给定一些结构体,结构体有value值和key值,Q次询问,输出每个key值对应的value值。

解题思路:思路很简单,写个类词法的递归函数,每次将key值映射成一个hash值,用map映射每个key的value起始终止位置,预处理完了查询就很简单了。 这题是最后10分钟出的,因为没有考虑value为{}的情