基于Qsys的DDR2内存驱动

目录

基于Qsys的DDR2内存驱动

1、建立Qsys系统

1.1、时钟

1.2、NIOS II

1.3、系统ID

1.4、片上RAM

1.5、JTAG调试器

1.6、DDR2控制器

1.7、连接

2.2、顶层代码

2.3、引脚分配

2.4、NIOS程序编写测试

基于Qsys的DDR2内存驱动

按照正常步骤建立Quartus工程,新建一个顶层的Verilog文件用于调用Qsys系统。

此处有一个疑问:板卡上的芯片型号为EP4CGX75CF23I7,但参考板卡给的例程,发现其选用的芯片型号为EP4CGX75CF23C8,所以此程序也使用C8型号的芯片。

1、建立Qsys系统

了解DDR的基本知识,参考的是小梅哥电子的AC6102开发板的视频及PDF文档教程。建立Qsys的系统参考的是小梅哥AC6102和黑金电子的AX530教程。

1.1、时钟

设置输入时钟为100MHz。

1.2、NIOS II

选择NIOS II/f类型的软核,设置复位向量地址(程序代码存放的位置)和异常向量地址(程序运行的地址),因为DDR2存储器上电工作前需要对前几个地址的进行反复的数据读写操作,用来协商一个最佳的数据传输速率,所有需要设置一段偏移地址,设置地址偏移的大小参考Intel官方的文档,此处设置为0x100,同样异常地址的偏移量为0x120。

经过实际测试,发现不额外设置那0x100的偏移量,系统照样可以正常运行。

设置系统的Cache大小,可以使用默认大小,最下面的红框应取消勾选,因为使用的DDR2的位宽为128bits(64bits+双速率数据接口),所以需要“使处理器中的最高有效地址位绕过数据缓存”。

其余的部分均采用默认设置。

1.3、系统ID

此模块是用来给当前的Qsys系统一个唯一的编号,因为有些SOPC系统中可能会出现多个NIOS II处理器的情况。此处随意设置一个数值即可。

1.4、片上RAM

此处需要片上RAM,为了在系统建立初期验证,排除系统中除去DDR2控制器之外的错误给系统造成影响。

1.5、JTAG调试器

直接采用默认设置即可

1.6、DDR2控制器

设置部分与第一章中的配置界面相同,按照同样的参数设置。需要改变的是输入时钟为clk的100MHz。

应该注意复位信号的连接。

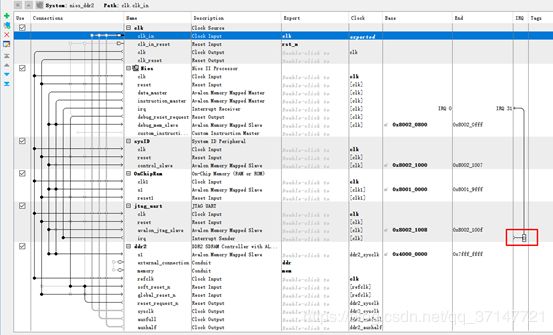

1.7、连接

参考下图中的连接,重新分配基地址,分配中断号。

2.2、顶层代码

顶层代码代码,用于调用Qsys核

module DDR2_Systems

(

clk, rst_n, key_in,

mem_odt, mem_clk, mem_clk_n,

mem_cs_n, mem_cke, mem_addr,

mem_ba, mem_ras_n, mem_cas_n,

mem_we_n, mem_dq, mem_dqs,

mem_dm,

led

);

input clk;

input rst_n;

input key_in;

output reg [3:0] led;

output [1:0] mem_odt;

inout [1:0] mem_clk;

inout [1:0] mem_clk_n;

output [1:0] mem_cs_n;

output [1:0] mem_cke;

output [13:0] mem_addr;

output [1:0] mem_ba;

output mem_ras_n;

output mem_cas_n;

output mem_we_n;

inout [63:0] mem_dq;

inout [7:0] mem_dqs;

output [7:0] mem_dm;

nios_ddr2 u0 (

.clk_clk (clk), // clk.clk

.ddr2_local_refresh_ack (), // ddr2.local_refresh_ack

.ddr2_local_init_done (), // .local_init_done

.ddr2_reset_phy_clk_n (), // .reset_phy_clk_n

.mem_mem_odt (mem_odt), // mem.mem_odt

.mem_mem_clk (mem_clk), // .mem_clk

.mem_mem_clk_n (mem_clk_n), // .mem_clk_n

.mem_mem_cs_n (mem_cs_n), // .mem_cs_n

.mem_mem_cke (mem_cke), // .mem_cke

.mem_mem_addr (mem_addr), // .mem_addr

.mem_mem_ba (mem_ba), // .mem_ba

.mem_mem_ras_n (mem_ras_n), // .mem_ras_n

.mem_mem_cas_n (mem_cas_n), // .mem_cas_n

.mem_mem_we_n (mem_we_n), // .mem_we_n

.mem_mem_dq (mem_dq), // .mem_dq

.mem_mem_dqs (mem_dqs), // .mem_dqs

.mem_mem_dm (mem_dm), // .mem_dm

.rst_n_reset_n (rst_n) // rst_n.reset_n

);

endmodule2.3、引脚分配

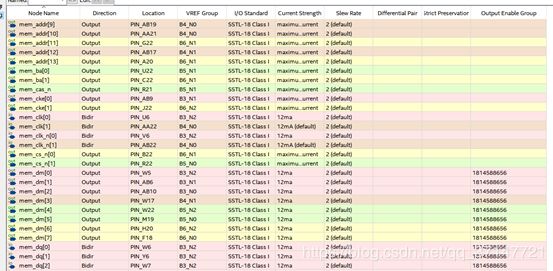

此次使用的PCIE板卡上有两个晶振,一个为100MHz,一个为25Mhz,注意引脚分配的时候注意不要分配错。

在给DDR2信号分配引脚的时候,不仅要分配引脚的号,还要选择引脚的电平标准,电流大小。还需要设置输出信号的分组,否则会在编译时出现错误。最好的方式是一次配置完成后export出一个tcl脚本文件,以后配置起来就方便很多了。

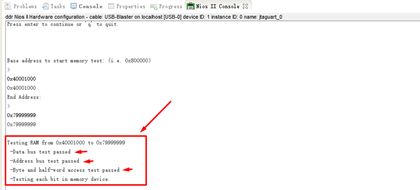

2.4、NIOS程序编写测试

打开Eclipse的NIOS开发环境,选择正确的sopcinfo文件,新建一个基于memtest_small模板的工程,直接编译,无需更改任何代码,然后下载运行。

此时程序已经成功运行起来了,按照提示的步骤进行测试。

可以看到测试均通过,说明DDR2已经成功得被驱动了。