FPGA verilog HDL 呼吸灯及呼吸流水灯实现

项目一:FPGA的呼吸灯实现

项目介绍:呼吸灯,就是想人们呼吸频率的一种led灯亮灭的一种表现形式。过程是慢慢变亮,然后变亮以后又慢慢变灭的一种过程。很多初学者会认为硬件逻辑语言怎么能控制电流的高低呢,让灯有多亮就调多亮,所以觉得不好实现,其实不用担心,呼吸灯捅破窗户纸就知道,其实是一个很简单的一个小项目,下面我将一步一步的讲解,并且实现。

项目小知识讲解:本次项目会用到计数器,计时器在我上一个文章里有介绍,这里就不多说了。此外再回顾一下占空比的小知识,PWM(Pluse Width Modulation)脉冲宽度调制,是一种对模拟信号电平进行数字编码的方法。通过高分辨率计数器的使用,方波的占空比被调制用来对一个具体模拟信号的电平进行编码。并广泛应用在从测量、通信、功率控制与变换及LED照明等许多领域中。顾名思义,就是占空比可调的信号,那么什么是占空比呢?

占空比(Duty Cycle or Duty Ratio),可以解释为,在一脉冲序列中(方波),正脉冲序列的持续时间与脉冲总周期的比值。也可理解为,电路释放能量的有效时间与总释放时间的比值。PWM是怎样实现调光呢?想要调节LED的亮度变化,实则是调节控制流经LED的电流。电流增大则LED亮度增强,反之减弱。但由于电流为模拟信号,所以这时就用到了PWM。

假设刚开始时占空比为1%,慢慢的占空比为2%、3%、4%……56%、57%……98%、99%、100%。

这就是LED灯亮的一个过程,我们可以让占空比为1%时,令LED灯亮,其余的部分让LED灭,慢慢的占空比越来越大,亮的部分也越来越多,这就是一个由灭到亮的一个过程。

假设刚开始时占空比为100%,慢慢的占空比为99%、98%、97%……64%、63%……2%、1%、0%。

这就是LED灯灭的一个过程,我们可以让占空比为99%时,令LED灯灭,其余的部分让LED亮,慢慢的占空比越来越小,灭的部分也越来越多,这就是一个由亮到灭的一个过程。

项目设计:

首先我们要思考,如何设计这样描述的一个过程,很多人应该想到了用计数器,没错,确实要用到计数器。下面我们可以先画一下项目构思前的时序图。

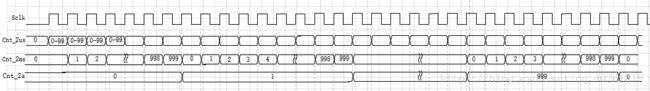

自己手动画的,有点粗糙,就凑合的看一下吧.......时钟的线只是为了对齐,真实的时钟只对着2us计数的一个时钟周期的;比如说晶振为50MHZ,那么每一个时钟周期相当于1/50M=20ns,故第一个计数器为一个2us的计数器,每计100次之后清零;第二个计数器为2ms计数器,每当2us计数器计数100次时,2ms就会增加一次。同理2s计数器也是一样。

我们可以看出,当cnt_2s>=cnt_2ms的部分刚好是我们上面所说的占空比的位置,而且当cnt_2s加到999的时候刚好占空比为100%,所以我们就会多了一个条件,当cnt_2s>=cnt_2ms,我们让LED亮,cnt_2s

一个完整的呼吸灯时间为2s,也就是,由亮变暗需要2s,由暗变亮需要2s;将 2s分为1000等份,也就是由亮变暗,需要1000次的变化,每次为2ms,将,2ms分为1000等份,占空比100%过渡到0%,需要100次的变化,每次为2us;

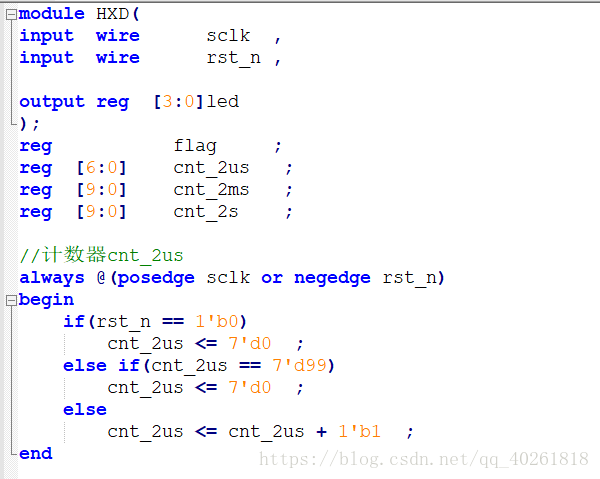

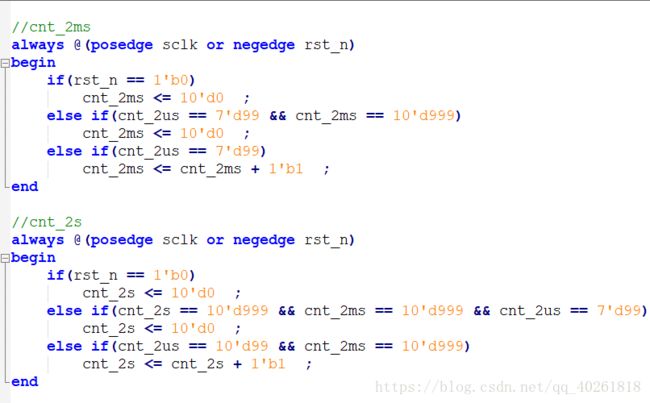

既然原理差不多有了解,下面我们就开始编程环节了:

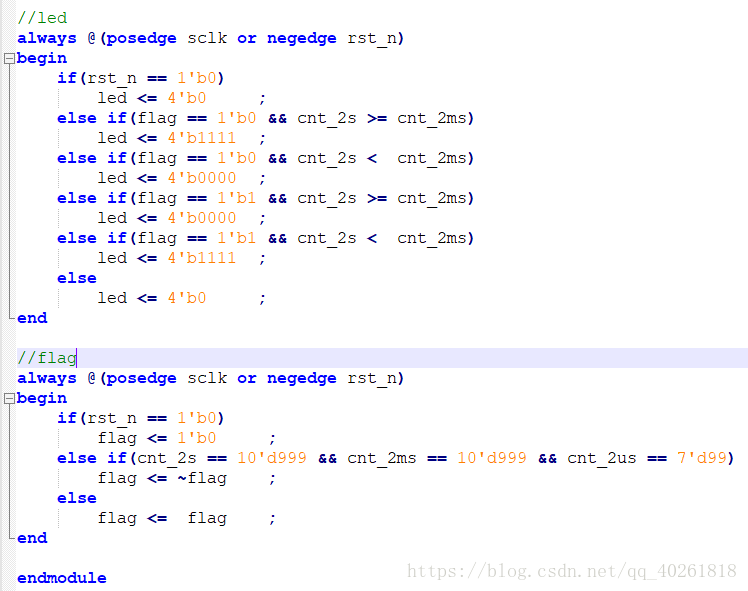

上半段只是一个由灭到亮的一个过程,我们下面开始下下半段(有亮到灭的过程),很多人都会觉得那岂不是和上面一样再写很多程序嘛!!!!就不卖关子了,只需要加一个标志位flag就可以了。

记得加了标志位flag的时候,要把标志位flag的判断条件写在LED模块当中。

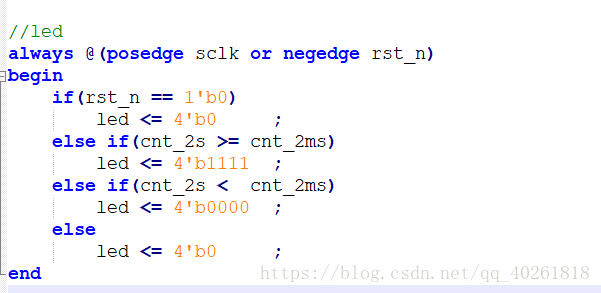

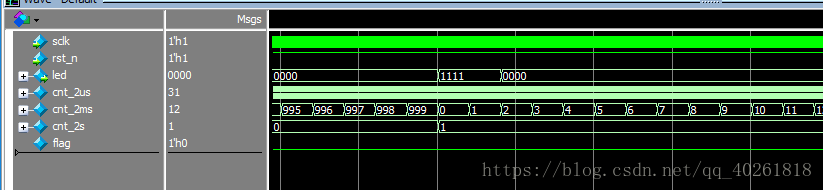

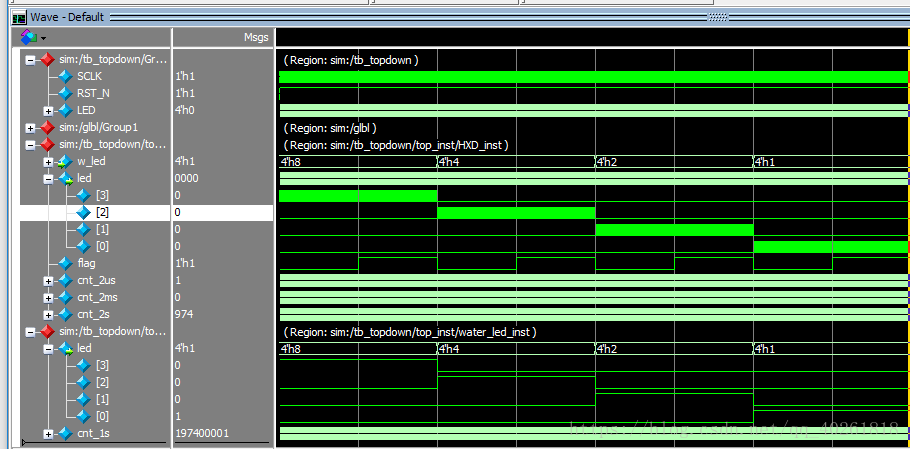

下面是仿真图

根据仿真图我们可以看到灯只在一小段是亮的,其余的时间都是灭的,故后面也是一样的结果。

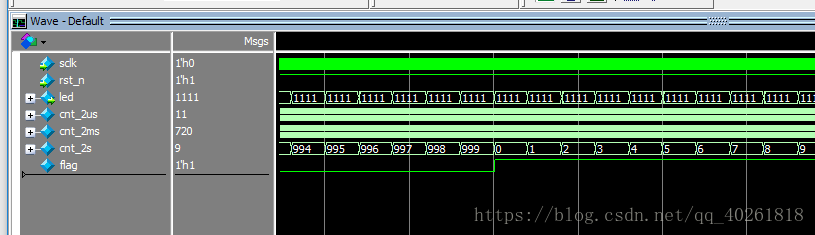

上图是全亮的时候准备进行由亮到灭的过程。

项目二:双向流水呼吸灯的实现

项目设计:实现流水灯的现象,并且在流水的时候每个LED灯都实现呼吸灯的效果。为了实现这个效果,本次的设计是像踏步一样的小项目,第一个LED灯准备从最亮到灭的那个临界点,第二个LED灯就开始准备由灭到亮的一个过程,全程实现一个双向流水灯的效果,流水到最右边再返回。也就是说0S时第一个LED灯开始亮,到2S时再慢慢熄灭,此时第二个LED灯准备开始慢慢变亮到4S时慢慢熄灭,此时第三个LED灯准备慢慢变亮,以此类推..........

程序设计:流水呼吸灯的方法多种多样,仁者见仁,智者见智。比如将呼吸灯模块例化到顶层模块去设计;用状态机控制每个灯的过程;设置标志位信号,用位拼接的方法去完成呼吸流水灯。此次设计为了方便初学者理解,用一种最简单的方法,加一个计数器,去控制每个灯的变化。

让它每次在每个2S末尾处触发+1,在7的时候清零,共计8个2s;思路在项目设计处有说,只有在每块加一个条件,即可以实现效果,但是在每个cnt计数的时候,要注意第一个项目程序中的flag是1还是0;

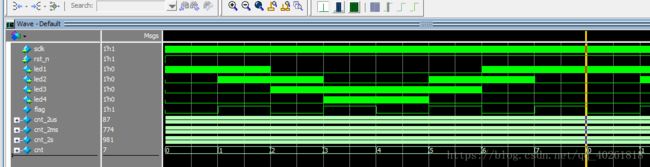

效果大概和仿真时一样的(踏雪寻梅的效果),仿真图如下:

下面是用例化到顶层文件实现的流水呼吸灯的仿真:

一般很多人看着仿真图便可以将程序写出,若新手不懂的,可以自行下载一下程序,因为程序过长,我将源程序和仿真程序打包上传了,有兴趣的可以自行下载一下:

https://download.csdn.net/download/qq_40261818/10580989

写博客是为了方便学弟学妹们学习以及初学者学习,也欢迎大家交流,请勿盗用,感谢尊重原创!

谈合作项目等请加V zhanghs1313