Altera DDR2控制器使用IP的方式实现,一般很少自己写控制器代码。

ddr22 ddr22_inst

(

.aux_full_rate_clk (mem_aux_full_rate_clk),

.aux_half_rate_clk (mem_aux_half_rate_clk),

.global_reset_n (global_reset_n),

.local_address (mem_local_addr),

.local_be (mem_local_be),

.local_burstbegin (local_burstbegin_sig),

.local_init_done (),

.local_rdata (mem_local_rdata),

.local_rdata_valid (mem_local_rdata_valid),

.local_read_req (mem_local_read_req),

.local_ready (mem_local_ready),

.local_refresh_ack (),

.local_size (mem_local_size),

.local_wdata (mem_local_wdata),

.local_write_req (mem_local_write_req),

.mem_addr (mem_addr[12 : 0]),

.mem_ba (mem_ba),

.mem_cas_n (mem_cas_n),

.mem_cke (mem_cke),

.mem_clk (mem_clk),

.mem_clk_n (mem_clk_n),

.mem_cs_n (cs_n),

.mem_dm (mem_dm[1 : 0]),

.mem_dq (mem_dq),

.mem_dqs (mem_dqs[1 : 0]),

.mem_odt (mem_odt),

.mem_ras_n (mem_ras_n),

.mem_we_n (mem_we_n),

.phy_clk (phy_clk),

.pll_ref_clk (clock_source),

.reset_phy_clk_n (reset_phy_clk_n),

.reset_request_n (),

.soft_reset_n (tie_high)

);

以mem开头的一堆信号,是直接导出为顶层引脚,去连接PCB板上的DDR2芯片的。

以local开头的一堆信号,是ddr2控制器导出给用户的接口信号,用户要向ddr2存储器中写入数据或者从ddr2中读出数据,只需要操作local接口即可。

local信号,可以分为以下几组:

控制组

local_init_done:DDR2控制器初始化完成标志信号,DDR2控制器上电需要经过一系列的初始化操作,包括DDR2芯片的初始化和DDR接口的时序校准,整个过程耗时较长。待该信号拉高之后,local接口上才能进行读写操作。

local_refresh_ack:ddr2控制器对ddr2芯片执行刷新操作后的应答信号,一般用户读写时,不用关心该信号。

用户写接口

local_address :用户希望将数据写入到的DDR2存储器的地址,该地址为DDR2芯片片选、行地址、bank地址、列地址的组合,{CS、ROW、BA、COL}。

local_be:写入时候的字节使能,例如对于DDR2是16位硬件接口,则用户数据接口为32位,为4个字节,所以local_be的位宽为4,每一位对应一个字节,如果写入时候用户端32位的数据中有一个字节不希望被写入,则对应的be位设置为0即可。

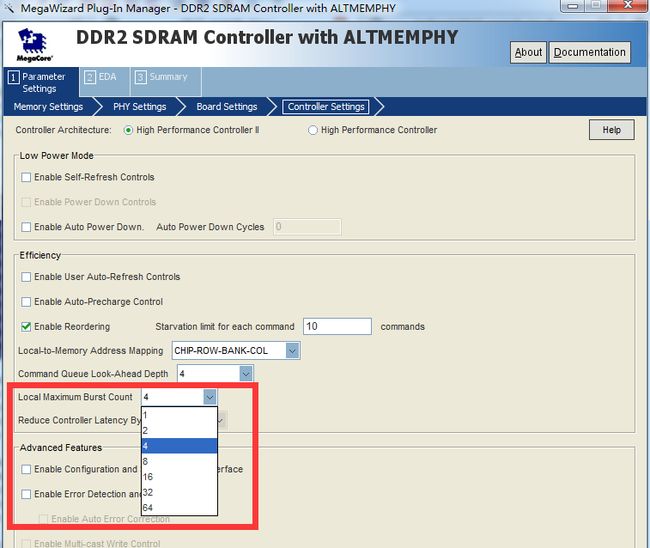

local_size:用户接口的突发长度,指定每次用户发起一次写入请求会写入多个数据。该长度最大值在DDR IP的配置界面可以配置,如下图所示。注意该值是控制器的最大突发长度设定值,不等于DDR2芯片支持的最大突发长度,DDR2芯片最大只支持8个长度。

local_burstbegin:用户接口的突发启动信号,该信号每一个高脉冲会启动一次突发传输,每次传输长度为local_size指定的长度

local_ready:ddr控制器就绪标志信号,该信号有效则表明当前数据被成功写入了ddr2控制器中,为0则表示ddr控制器无法接受当前操作,用户需要保持当前地址、数据和控制信号不变直到ready信号再次拉高

local_wdata:用户需要写如到ddr中的数据,位宽为ddr芯片数据线位宽的2倍

local_write_req::写数据请求信号为1则local_wdata端口上的数据允许被写入ddr控制器,(具体能否成功写入,还得看local_ready的状态)

local_address:用户希望从DDR2存储器读取数据的地址,该地址为DDR2芯片片选、行地址、bank地址、列地址的组合,{CS、ROW、BA、COL}。

local_be:读出时候的字节使能,例如对于DDR2是16位硬件接口,则用户数据接口为32位,为4个字节,所以local_be的位宽为4,每一位对应一个字节,如果读出时候用户端32位的数据中有一个字节不希望被读出,则对应的be位设置为0即可。

local_burstbegin:用户接口的突发启动信号,该信号每一个高脉冲会启动一次突发传输,每次传输长度为local_size指定的长度

local_rdata:读取到的数据内容,位宽为ddr芯片数据线位宽的2倍

local_rdata_valid:读取数据有效标志信号,当该信号有效时,表明local_rdata上的数据是读到的有效内容

local_read_req:读请求信号

local_size:用户接口的突发长度,指定每次用户发起一次读取请求会读出多少个数据。该长度最大值在DDR IP的配置界面可以配置,如下图所示。注意该值是控制器的最大突发长度设定值,不等于DDR2芯片支持的最大突发长度,DDR2芯片最大只支持8个长度。