FPGA实践教程(三)系统搭建与烧录

本文档系列是我在实践将神经网络实现到Xilinx 的zynq的FPGA上遇到的问题和解决方法。

背景:我们用vivado HLS对相关软件生成了相应的IP core,现在我们需要将IPcore集成为系统模式,集成为系统才能烧录到FPGA上。

目的:用vivado软件搭建相应的系统,生成比特流并烧录入FPGA

可以参考文档UG871中Chapter9.10.11中的部分。

参考与相关内容:

实践教程(一)用HLS生成IPcore

实践教程(二)连接片上ARM

实践教程(三)系统搭建与烧录

实践教程(四)片上ARM运行程序

实践教程(五)PS用MIG调用DDR

目录

1.用vivado打开工程

2.搭建系统

2.1添加IP

2.2连接相应的IP

2.3 生成比特流

3.比特流烧录入FPGA

4.启动arm运行程序并验证

1.用vivado打开工程

1.1解压文件夹(是否每次都要打开新的工程,才能保证烧写成功?)

解压后的工程包含的processing system正是我们的FPGA对应的,所以必须用此文件夹

1.2打开vivado,打开解压后的文件夹的位置,并打开工程

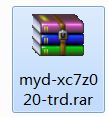

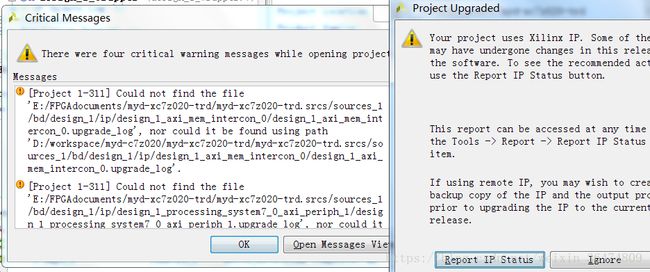

由于版本问题会缺失一些文件,此问题不大,会出现一些提示信息,这些提示信息都是正常的,我们把相应的IP更新,更新为当前版本的IP。

是否out-of-context,我们选择per IP

2.搭建系统

2.1添加IP

vivado可能在添加IP时候闪退,所以我们要保持良好的习惯,一是时时crtl+s,二是加完IP再改管脚。

2.1.1导入IP库,我们创建的IPcore就在这个库里面(注意点进去solution2这个文件夹添加,下面这种可能添加不进去)

2.1.2在block design中加入IP

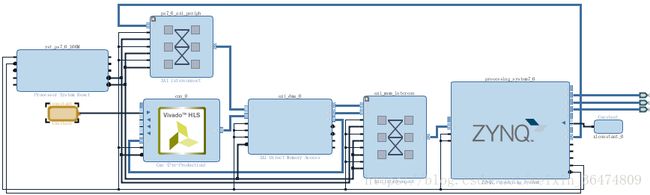

需要加入三个,一个是axi direct memory access,一个是我们的IPcore cnn

2.1.3 修改system IP管脚

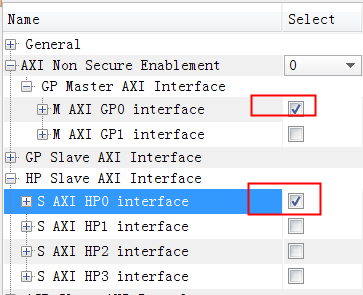

首先system里面AXI通信用的这两个,GPmaster和HP slave,master与slave分别是主与从,master与

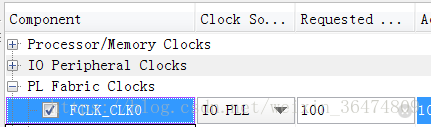

然后是clock configuration中的fabric clock,几乎所有的输出用的都是这个clk,100MHz

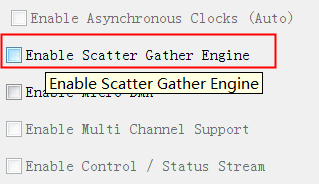

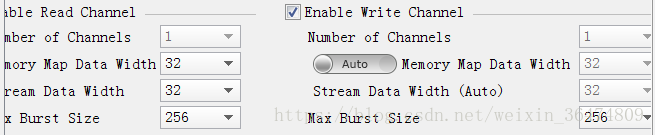

2.1.4修改DMA的管脚

取消勾选scatter gather engine,这个没有用并且能减少很多管脚。

最大并行两个都改成256,上面BufferLength改为23,这样能够更快的实现数据的传输。

2.2连接相应的IP

bug容易出现在这一步,所以这一步一定要小心,在之前工程的基础上最好把相应的连线都去掉,然后重新连接。

2.2.1 点击run connection automation

2.2.2 连好后cnn的出连DMA入,DMA入连cnn出,用的axis通信

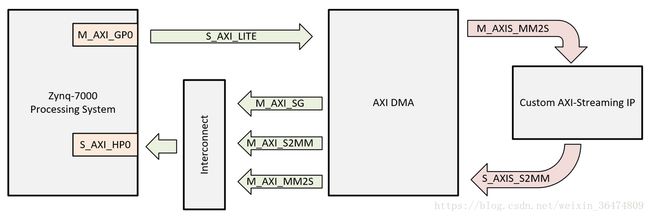

- DMA的内存方式为MM:memory map, IPcore的内存方式为S:stream,所以S2MM与MM2S一定要搞清楚。

- FPGA的DMA与AXI总线

- 虽然接口的综合被自动进行,但是我们还是需要了解下,PS的GP输出数据流给AXI Interconnect,这个AXI Interconnect的出连接DMA的AXI Lite入

- DMA的M_S2MM与MM2S都连在AXI Interconnect进而接入PS的HP

- 我们看到cnn与DMA相连,DMA的入与出都与PS之间接了AXI Interconnect

2.2.3 cnn的clk和rst连到对应的位置

- ProcessorSystemReset的ext_reset_in连系统rst的出,

- ProcessorSystemReset的出有两个,一个interConnectRst一个peripheralRst,分别表示内部连接与外设的复位

- cnn算外设,连在peripheralRst,DMA,两个AXI interconnect都与peripheralRst相连

- interConnect的两个reset只连在两个interconnect的IPcore上

2.2.4 给ap_start加入constant,值为1保证工作

2.3 生成比特流

2.3.1 validate不报错和警告,然后regenerate layout

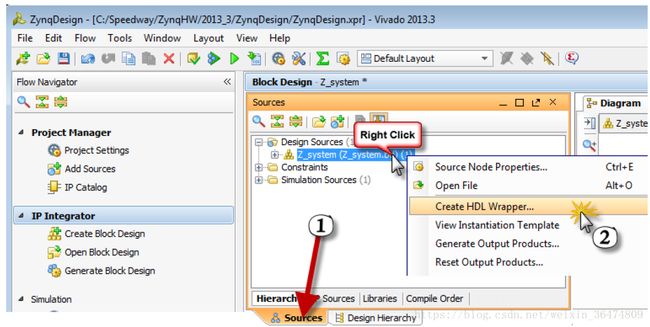

2.4 create HDL wrapper,点击生成比特流,这个过程大概耗费20分钟

3.比特流烧录入FPGA

3.1在工程目录里面找到刚刚生成的.bit文件,然后拷贝到SD卡里面,命名为7z020.bit,把SD卡插入FPGA,然后FPGA一旦启动就会自动根据相应的.bit文件进行烧写。

3.2可以不看。另一种方法是用SDK软件,这种方法暂时不用(Export the hardware to SDK)

参见实践教程(五)PS用MIG调用DDR 中的目录五SDK

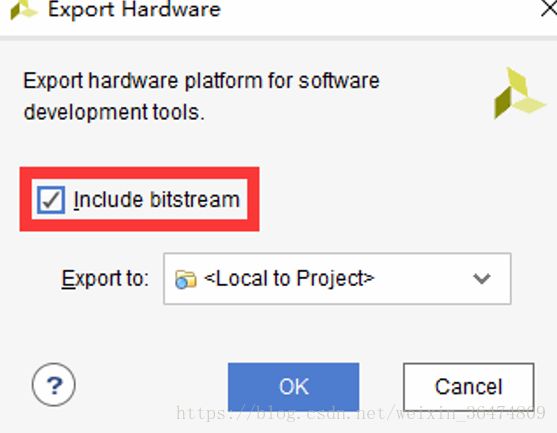

5.1 file-export-export hardware,需要包括相应的比特流

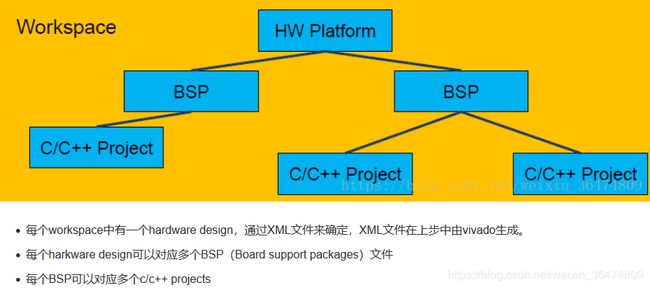

5.2 打开SDK,我的电脑用vivado直接打开SDK总是死机,所以我们直接打开SDK,目录改到之前vivado的目录下面,创建新的applicaiton project (这里非常需要注意,workspace、BSP、application project是很不同的)

FPGA基础知识(九)SDK相关知识

这里注意点击new,添加之前的wrapper进入,wrapper在vivado生成的文件夹的xxx.sdk之中。

6.1 编译工程

6.2 连接FPGA,注意要用JTAG线来连,并且也要连USB。

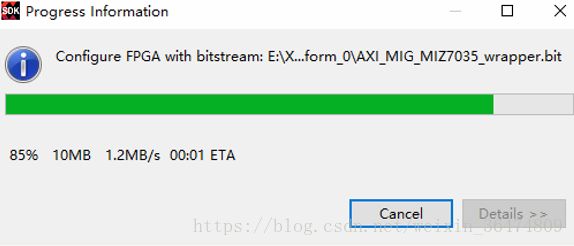

6.3 烧写比特流进入FPGA(FPGA每断电一次,就要重新烧写一次)或者在右键HW创建。

6.4 运行及结果

当比特流生成之后,硬件设计就完成了,我们我们就可以在processor上运行相应的code了。这部分工作会在Xilinx SDK(Software Developer Kit)上运行。所以我们先要从vivado上将相应的项目export到SDK上。(SDK有点liscence问题打不开,并且直接通过SD卡可能更加简单一些,所以我们用SD卡来进行相应的比特流操作)

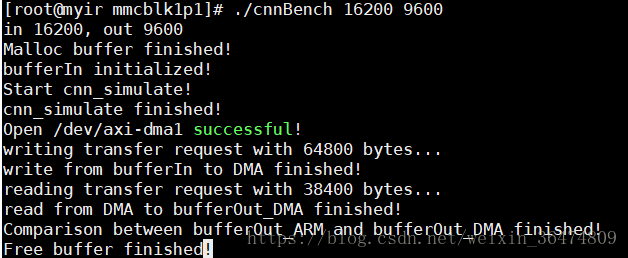

4.启动arm运行程序并验证

先启动FPGA并连接片上ARM,运行相应的arm程序进行验证,这部分工作见:

FPGA实践教程(四)片上ARM运行程序

相应linux指令:

cd /mnt/mmblk1p1

./dmabench 16200 9600

表明运行成功。

实践教程(一)用HLS生成IPcore

实践教程(二)连接片上ARM

实践教程(三)系统搭建与烧录

实践教程(四)片上ARM运行程序

实践教程(五)PS用MIG调用DDR