Vivado2018.2联合Matlab的FIR滤波器设计与仿真

Introduction

目录

Introduction

新建工程(Create a New Porject)

输入正弦波叠加IP核实现

FIR低通滤波器设计

引出

matlab进行滤波器参数设计

窗函数法设计FIR滤波器

FIR滤波器系数量化

FIR滤波器系数导出

将.coe文件导入FIR IP核

Block Design连线&生成顶层模块

联合Modelsim波形仿真

之前用过ISE和Quartus II一段时间,给我感觉二者界面并不是特别的友好,而且最近版(2018.2 Update)的ISE14.7最高支持Virtex-6系列,如图1:

Virtex-7系列Xilinx公司推荐使用Vivado,因为Xilinx公司的高端系列芯片基本都是基于Vivado开发的;另外一点,基于老师那边的项目用到了Virtex-7系列下的XCKU115, 因此这次就使用Vivado2018.2进行项目学习与开发,而且最近(2018.10)更新的Vivado2018.2安装之后发现它的界面风格是我比较喜欢的,如图2和3:

不得不说,IP核是一个很神奇的东西,通过它可大大减少我们的开发时间,而且Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等),IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便。

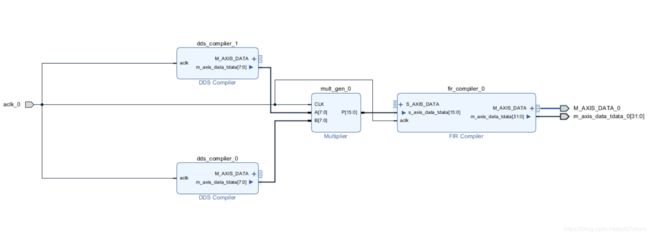

本次也是基于FIR的IP核进行低通滤波器设计,滤波器参数由matlab的工具箱FDATool设计给出,输入波形为4MHz和5MHz的正弦波叠加,叠加过程由乘法器IP核实现,正弦波由DDS IP核实现,系统整体过程见下:

新建工程(Create a New Porject)

打开Vivado2018.2,点击Create Project选项,如图4:

点击Next,如图5:

命名工程(Project name)以及工程存储路径(Project Location),注意路径不要含空格和中文,空格用下划线替代,这里我取名为FIR_blog,勾选上Create project subdirctory(创建工程子目录),点击Next

选择工程类型(Project Type),如图6,一般对于普通的项目我们选择RTL Project(在设计PCB会用到I/Oplanning这种类型,用在原理图和封装兼容性设计),同时不勾选Do not specify sources at this time,后续再添加源文件就行,点击Next

添加源文件(Add Sources)和物理&时间约束引脚文件(Constraints),如图7和8,现在先不添加,直接点击Next就Ok

选择芯片型号,因为老师的项目用到了Xilinx公司的V7系列XCKU115,我们选择该芯片型号,直接搜索就可以,

芯片封装型号:flvf1924 速度等级:3 ,点击Next

最后生成Project Summary,这里可以查看上一步选择的芯片型号以及添加的源文件,由于我们没有添加源文件,因此显示No Source files...,点击Finish创建New Project成功。

输入正弦波叠加IP核实现

首先利用Vivado的DDS IP核生成两个正弦信号(频率分别为4MHz和5MHz)

- 点击创建Block Design,命名Design name,这里命名为dds_fir,如图12:

- 点击Add IP,如图13,直接搜索dds,双击DDS Compiler生成一个dds IP核,如图14所示

- 选中DDS IP核双击,打开设置界面,对相关参数进行设置(Re-customize IP),如图15

Configuration界面设置如下图16:

Implementation设置如图17:

Detailed Implementation界面如图18所示:

Output Frequencies设置,如图19,这里我们仅用到一个通道,输出信号频率设置为4MHz,其他默认为0就行。

按上述步骤设置完后的Summary如图20,点击OK

- 选中DDS IP核点击鼠标右键copy,或者再次点击界面中的加号“+”添加一个新的DDS IP核,如图21,我们使用Ctrl+V复制粘贴原来的DDS IP核,将输出频率Output Frequencies设置中的通道1频率改为5MHz,点击OK

- 调用乘法器IP核将两路正弦信号进行混频,如图22

按上述方法添加一个乘法器IP核,搜索multiplier,双击Multiplier添加进去。

双击乘法器IP,进入Re-customize IP界面对IP核进行参数设置,输入位宽(A和B)选择8,其他参数默认即可。

FIR低通滤波器设计

引出

两路正弦信号(4MHz和5MHz)经混频后积化和差得到1MHz和MHz的混合信号,我们再设计一个FIR低通滤波器将高频的9MHz信号滤除掉,按上述添加IP核操作添加一个FIR IP核(搜索fir即可),如图25:

添加完FIR IP核后,那么我们如何对FIR低通滤波器的参数进行设计呢??

matlab进行滤波器参数设计

窗函数法设计FIR滤波器

窗函数法设计滤波器的基本思想是:选择一种合适的理想频率选择性滤波器,然后将它的冲激响应截短以获得一个具有线性相位和因果的FIR滤波器,因此这种方法的关键是选区某种较好的窗函数,在滤波器性能给定的情况下,尽量选择主瓣窄,旁瓣峰值小的窗函数。

这里我们利用matlab的工具箱FDATool(当然也可以利用其他工具进行Filter设计,比如Filter Solutions等软件),打开matlab,在Command窗口输入fdatool打开滤波器设计界面,如图26所示:

在弹出的窗口中,在Response Type(滤波器响应类型)一栏中选择Lowpass(低通),Desgned Method(实现方法)选择Window(窗函数实现),即基于窗函数法设计FIR滤波器,我们在Options中选择Hamming窗,Filter Order中选择Special Order,滤波器阶数选择128(阶数越高,滤波效果越好,占用的芯片资源会更多些),Frequency Specializations中单位Units选择MHz,采样频率Fs选择100MHz(根据奈奎斯特低通信号采样定理,采样频率至少高于信号的2倍,实际工程上一般得高于低通信号频率的5-10倍,如果信号频率过高的话,实际的AD采样频率核精度无法达到,所以工程上一般把低通信号经调制后搬到频率很高的载波上,再下变频到中频上用带通采样定理进行AD采样),之前提到采样频率高于信号频率的5-10倍就可以,因为我们这里FIR滤波器时钟是和板卡时钟连接在一起的,没有编写时钟分频模块,所以这里采样频率直接设置为100MHz(一个周期点数为100MHz/2MHz=50,板卡资源会浪费一些,但是不影响),截止频率Fc设为2MHz(1MHz的正弦波通过,9MHz的被滤除),点击View和Design Filter按钮,设计的滤波器时域和频域波形(Time Domain and Frequency domain)以及幅相响应(Magnitude and Phase Response)如图27所示:

FIR滤波器系数量化

点击如下图所示的Set quantization parameters按钮后,界面变为图29所示,选择Fixed Point(定点)

因为FPGA只能进行定点操作,而matlab可以进行浮点计算也可定点计算

按如图30所示进行设置,分子字长(Numerator word length)量化为16,这里涉及到FIR滤波器的知识,滤波器可以看出一个有输入有输出的黑盒子,其系统函数可表示为:

![]()

实际中常用的基本是在有用频率内(本设计中即0-2MHz为有用频率,我们希望得到1MHz的正弦波)具有线性相位的FIR滤波器,因为如果不是线性相位,滤波器对有用信号的不同频率响应产生的相移不一致,便会造成输出信号失真的现象。

FIR滤波器系数导出

点击Filter Design菜单栏的Targets选项下拉菜单的Generate C Header和XILINX Coefficient(.COE) File,分别导出的是C的头文件和.coe文件(滤波器系数文件),C的头文件源码如图31所示,.coe文件如图32所示(因为滤波器阶数为128,所以系数个数为:阶数+1=129,这里参见滤波器知识,N阶滤波器系数为a0,a1,...,an,有N+1个系数)。

将.coe文件导入FIR IP核

Vivado中的FIR IP核支持.coe文件导入,C文件暂时无法导入,双击FIR IP核,打开Re-customize IP界面,如图33所示,左边是滤波器的频率响应。

- Filter Options选项卡

Filter Coefficient中Select Source选中COE File,点击Browse按钮,添加.coe文件路径后Vivado自动将滤波器系数导入IP核中,Filter Specialization中Filter Type选择单速率型(Single Rate),抽取型(Decimation)和插值型(Interpolation)常用于特殊场合,抽取型一般多用于数字前端下变频抽取样值降低AD采样速率,插值型用于常用于提高采样速率,,这里我们选择Single Rate即可,如图34:

- Channel Specialization选项卡

由于只使用一个通道,因此交织通道序列(Channel Sequence)选择Basic,通道数(Number of Channels)为1;板卡硬件过采样初始化(Hardware Oversampling Specialization中,输入该滤波器数据的采样速率(Input Sampling Frequency)为100MHz,IP核的工作时钟频率(Clock Frequency)为100MHz(即板卡时钟)

- Implementation选项卡

导入系数后Vivado会根据导入的系数自动识别是何种类型的滤波器,根据滤波器的特点对FIR滤波器结构做性能优化,比如导入的是HalfBand Filter,Coefficient Structure中会出现Half Band一栏,在Coefficient Structure选项卡中会出现软件识别出的滤波器类型,这里软件识别为Inferred,我们也可设置为其他类型,如图36(1)所示

为使输出数据位宽位32,Output Rounding Modes(输出舍入模式)选择Truncate LSBs(截断最低有效位),这里我们保留了高32位,舍弃了低四位,若选择Full Precision(全精度输出),则输出数据位宽位36位,如图36(2)所示

- Detailed Implementation和Interface选项卡

Detailed Implementation和Interface选项按默认设置就可以,如图37(1)和(2)所示

- Summary选项卡

在Summary栏中对之前设置的滤波器参数进行总览,如图38,这里我们可以看到,输出位宽位32位,而非全精度输出Full Precision(36位),因为之前我们对它进行了截断(Truncate LSBs),把最低有效位LSB截断,保留了高32位。

Block Design连线&生成顶层模块

- 按上述步骤对FIR滤波器参数设置完成后,将所有的IP核模块连接起来

选中aclk时钟端口,如图39,点击鼠标右键,选择Make external命令引出时钟端口线,再将所有IP核模块的时钟线连接起来,如图40

将所有的模块按下图41所示进行物理连接,并引出输出端口(Make external),Ctrl+S保存

- 生成top模块

如图42所示,选中左侧Sources栏中的bd文件(Block Design File)dds_fir,即图41所示的模块化框图,点击鼠标右键选择Create HDL Wrapper进入如图43所示的Create HDL Wrapper界面,选择Let Vivado manage wrapper and auto-update(让软件自动完成Top Module and IP核包装和更新)

完成该操作后生成如图44所示的.v顶层文件(dds_fir_wrapper.v)和IP核接口例化文件(dds_fir.v),双击文件打开,如图45和图46所示,且IP核接口文件属性为只读(Read-Only),顶层文件可以修改,

联合Modelsim波形仿真

- 编写testbench测试文件

我们编写一个仿真测试文件对上述Block Design进行功能/行为仿真,如图47所示,点击左侧Flow Navigator栏中的Add Sources添加源文件,

选择Add or create simulation sources(添加或者创建仿真源文件),点击Next

添加源文件(Add Sources),这里我们创建一个新的file(Create File),如图49

仿真文件命名:这里命名为fir_tb,如图50所示

添加完成后,我们双击fir_tb打开,编写如下代码:

- 设置Modelsim仿真环境

完成上述操作后,我们可以选择第三方仿真工具Modelsim进行功能仿真,关于Vivado2018.2如何设置与Modelsim10.5的联合仿真参见我的下一篇博客。

- Run Simulation

点击左侧的Simulation->Run Simulation,如图52

- Modelsim仿真结果

我们可以在Modelsim中添加想要观察的信号波形,操作方法见下图52所示,在左侧栏中为我们使用到的模块,选中该模块即可在Object窗口栏下看到该模块的输入和输出以及有效位,鼠标右键Add Wave即可添加,注意:由于这里采用的是Vivado自带DDS模块,输出正弦波,需要将Format更改为Analog(Automatic),如图54;同时,点击Modelsim工具栏中的Run All图标可以看到如下所示的完整波形。

由上图可知,4MHz和5MHz的正弦混频信号经过FIR低通滤波器后将9MHz的高频正弦信号滤除掉了,输出为我们需要的1MHz低频信号。

参考博客:https://blog.csdn.net/chinkwoyu/article/details/80262273

https://blog.csdn.net/weiweiliulu/article/details/40151053

https://blog.csdn.net/shichaog/article/details/50677386?tdsourcetag=s_pctim_aiomsg

欢迎一起学习交流,我的E-mail:[email protected]

为方面大家学习交流,现把我的工程文件放至Google云盘,链接如下:

https://drive.google.com/open?id=1k6wJdU0KU36cdTvAdeM6qWVWsu7csPIG