基于FPGA的千兆以太网设计

今天给大侠带来基于FPGA的千兆以太网设计,话不多说,上货。

一、设计概述

由于设计比较复杂,本篇带来设计流程以及设计思路,仅供各位大侠参考。

本篇通过管理数据输入输出MDIO配置PHY寄存器,使其工作在千兆通信模式下。FPGA通过ddio_out的IP核将数据单沿转双沿通过TX发送到PHY-A,PHY—B把收到的数据RX通过ddio_in的IP核双沿转单沿给FPGA采集,实现FPGA与PHY的交互通信。通过FPGA的SDRAM控制模块对SDRAM进行读写和刷新的操作,从而进行数据的存储与读取的操作。

根据UDP/IP协议将数据打包,并且通过IP源地址以及目的地址等来计算IP头部checksum和UDP头部checksum,在PC机上通过上位机软件Wireshark获取FPGA发送的1024byte的数据包,并且上位机显示通过UDP协议接收数据,数据位打包时加上CRC32冗余校验码,在FPGA的接收端可以加上CRC32解码操作,用来验证数据在传输过程中是否出错。

二、设计框架

整体模块比较复杂,自顶向下设计流程,分模块较多,需要注意各个端口信号,最好可以做成端口信号表,以免自己搞混淆。

注:复位省略,_t后缀表示数据或标志信号经过一级寄存器打拍操作。输入时钟25M,PLL倍频输出sclk125M,tx_data是偏移90度125M时钟。

三、数据流框图描述

四、DDIO模块简单描述

DDIO模块描述:

1、DDIO为调用的FPGA内部IP核;

2、ddioin是将双沿数转为单沿数据,ddioout是将单沿数据转化双沿数据。

ddioin时序图:

五、ram64模块时序描述

ram64模块描述:

ram64是深度为64位宽为8的LCs分布式RAM。

作用:

同频异相的同步化操作。

write时序图:

RAM64的Read控制模块描述:

rx_clk时钟域下的start_en和CRC_en转化到sclk时钟域下,都要先进行打三拍操作之后在被引用。(数据跨时钟域处理可以用双口RAM或FIFO,一般的标志信号有打拍法就可以)

1、 在start_ttt为高时,产生一个rd_flag信号,rd_flag信号在rd_cnt == batch_data – 1 时拉低,rd_flag信号为高时,rd_cnt开始计数自加1,在rd_cnt == batch_data – 1并且rd_flag=1时清零。

2、 Rd_en在CRC_en_ttt==1时拉高,否则为低。Rd_addr在rd_en=1时自加,在rd_cnt == batch_data – 1并且rd_flag=1时清零。

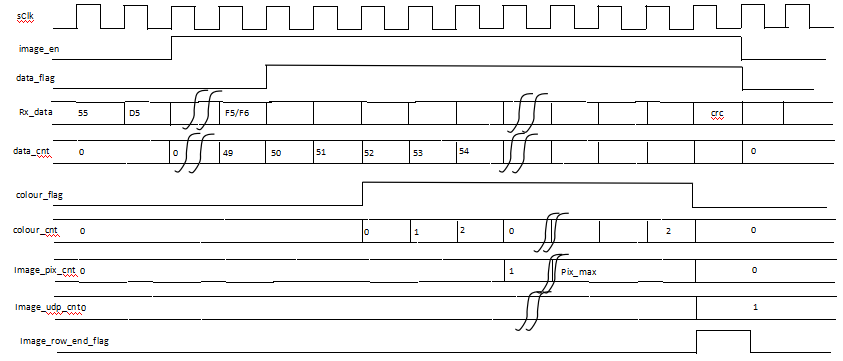

六、image模块时序描述

image模块描述:

por_img_pixel_cnt:像素点计数器;

por_img_pixel_max:像素点最大值;

por_img_udp_cnt:udp包计数器;

por_img_udp_max:UDP包最大值;

por_img_row_max:图片行最大值;

por_img_row_cnt:图片行计数器。

头包时序:

在mac_cnt=50时,取出image_w_h;

等于51时,取出image_w_l;

等于52、53、54时,分别取出image_h_h、image_h_l、image_type。

数据包时序:

Image_row_end_flag信号在por_img_pixel_cnt == por_img_pixel_mux&& por_img_udp_cnt == por_img_udp_mux&&colour_cnt == 2时拉高一个时钟周期。

Image_end_flag信号在por_img_row_cnt == por_img_row_mux&&por_img_pixel_cnt == por_img_pixel_mux&& por_img_udp_cnt == por_img_udp_mux&&colour_cnt == 2时,拉高一个时钟周期。

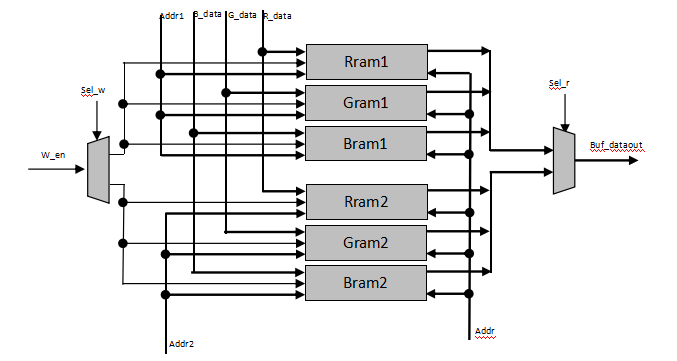

七、TWO_buffer模块时序描述

TWO_buffer模块描述:

two_buffer:乒乓操作。

作用:

使得SDRAM每次都能读到一行完整的图片数据。

1、 解决包间隔时间问题;

2、 分时、交替存储和读取,起到缓冲作用;

3、sel_w在image_row_end==1时进行反转;sel_r在sdram_read_ack ==1时进行反转。

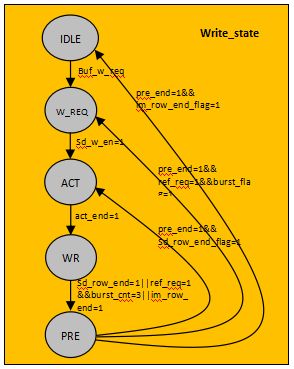

八、SDRAM控制模块描述

SDRAM控制模块描述:

1、512Kbit*32bit*4bank(64Mbit);

2、模式寄存器设置:0032,潜伏期3,突发长度4;

3、自刷新时间间隔:15us。

Sdram状态EBD描述:

Arbit_state:

Write_state:

读写模块状态机基本相似,自刷新模块状态机直接用线性序列机就可实现。这里不做重复概述。

九、RAM_2k模块描述

RAM_2k模块描述:

1、位宽24位,深度2K;

2、作用:缓存从SDRAM读出的图片的一行数据;

3、等待数据头包的发送和包间隔,并且进行图像一横数据的分包成帧发送。

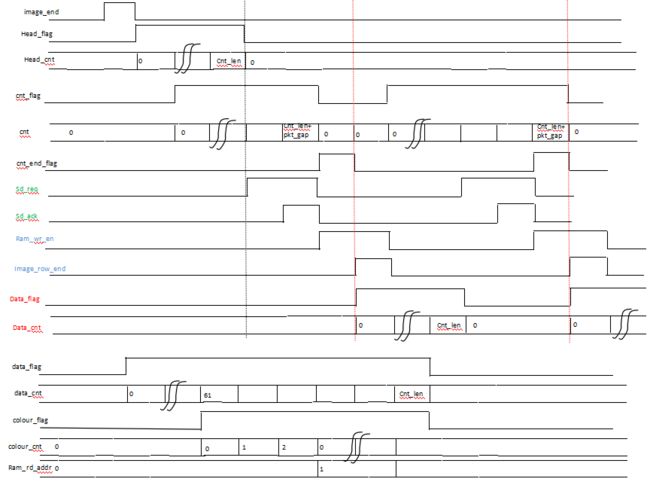

十、frame(成帧)模块的描述

frame(成帧)模块的描述:

根据千兆以太网协议(附录)进行帧包的配置,以太网(IEEE 802.3)帧格式:

1、前导码:7字节0x55,一串1、0间隔,用于信号同步 有的说是AA;

2、帧起始定界符:1字节0xD5(10101011),表示一帧开始 有的说是AB;

3、DA(目的MAC):6字节 如果设置为全1 为广播包;

4、SA(源MAC):6字节;

5、类型/长度:2字节,0~1500保留为长度域值,1536~65535保留为类型域值(0x0600~0xFFFF);

6、数据:46~1500字节;

7、帧校验序列(FCS):4字节,使用CRC计算从目的MAC到数据域这部分内容而得到的校验和。

注释:

1、head_flag在image_end=1时拉高,在head_cnt=cnt_len时拉低。

2、cnt_flag在head_flag=1||data_flag=1时拉高,在cnt=cnt_len+pkt_gap时拉低

3、sd_req在head_flag=1&&head_cnt=cnt_len||por_img_udp_cnt=por_img_udp_max&& data_flag=1&&data_cnt=cnt_len时拉高,在sd_ack=1时拉低。

4、ram_wr_en在sd_req=1时拉高,在image_row_end=1时拉低。

5、data_flag在cnt_end_flag=1 时拉高,在data_cnt=cnt_len时拉低。

6、colour_flag在data_cnt=60时拉高,在data_cnt=cnt_len时拉低。

7、ram_rd_addr在por_img_udp_cnt=por_img_udp_max && data_cnt=cnt_len清零。

十一、check_sum模块描述

check_sum模块描述:

check_sum是将成帧数据进行指定算法计算后的结果,用于数据校验。上位机会对接收到的数据做check_sum计算并且与成帧模块的check_sum计算结果进行比较,做出正确或错误提示。(wireshark数据包监控软件)

Chueck_sum部分波形图:

注释:

1、实现方法:将从frame模块输入到check_sum的数据进行check_sum计算,同时将输入data_in先存入一个深度为2k的RAM中,在所有chenck_sum算完之后,在建数据一个一个读出,在协议的相应位置加入check_sum值。

十二、crc模块描述

crc模块描述:

1、crc:循环冗余校验码,8位输入,32位输出。

算子方程式:

![]()

2、将输入数据进行crc运算,在crc校验运算完的同时,将32位校验码补在数据流的后四位。

总结

上位机软件:

1、receive_image上位机与从机通信软件;

2、wireshark数据包监控软件。

总结:

1、先进行DDIO的回环测试;

2、模块化设计编程实现,测试通过之后在进行top装配测试;

3、时序未出现违规时,查看slack是否大于0.3ns,注意时序约束;

4、注意assign语句的使用,尽量用时序进行操作,避免不必要的时序违例;

5、注意标志信号的使用,尽量避免运算式在判断条件里出现且进行多重判断逻辑嵌套;

6、 了解上位机与从机之间通信的基本原理;

7、 熟悉wireshark数据包监控软件的使用。

本篇大概分享了设计框架及思路,给各位大侠做设计学习参考,若想要详细学习,可阅读以下推文,系统性学习。

“FPGA产品设计与研发 ” 零基础入门及就业

END

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

往期推荐

-

荐读:基于FPGA的千兆以太网设计

-

简谈基于FPGA的千兆以太网设计

-

简谈 SDRAM的工作原理

-

如何操作SDRAM的自刷新命令而不影响正常读写操作?