Verilog HDL (6)结构化建模

前言:先说这节课听得不是很懂,没学数电,直接学verilog其实很难。但就像弹幕说的自己打开的视频,跪着也要看完。结构化建模优点之一是连线型变量与模块的连接关系很清楚。

3.3结构化建模

结构描述方式就是将硬件电路描述成一个分级子模块系统,通过逐层调用这些模块构成功能复杂的数字逻辑电路和系统的一种描述方式。在这种描述关系,组成硬件电路的各个子模块之间的相互层次关系以及相互联系关系都需要得到说明。

根据子模块的不同抽象级别,可以将模块的结构描述方式分成如下三类:

(1)模块级建模:通过调用用户设计生成的低级子模块对硬件电路结构进行说明,这种情况有低级模块的实例组成,可以被更高的层次模块调用,形成层次化

(2)门级建模:调用verilog内部的基本门级元件进行描述

(3)开关级建模:用基本开关元件来说明

3.3.1模块级建模

一个是设计模块,另一个是调用模块。

顶层模块不被任何模块调用(就像搭积木一样),必定有而且只有顶层模块。

1、模块的调用,调用模块实际上试讲模块所描述的电路复制并连接,格式是:

模块名<参数列表>实例名<端口列表>;实例名很重要,他指的是被调用模块在当前模块的名字

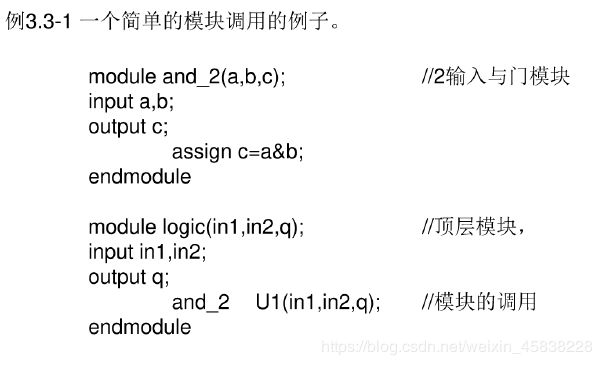

定义和调用模块,很像c中的定义和调用函数一样。上面这简单的例子没有参数列表,可以看出使用了位置对应方式,也就是in1是连接在a port的信号值,in2是连接在b port的信号值。实例名的好处之一就是在大文件中方便定位

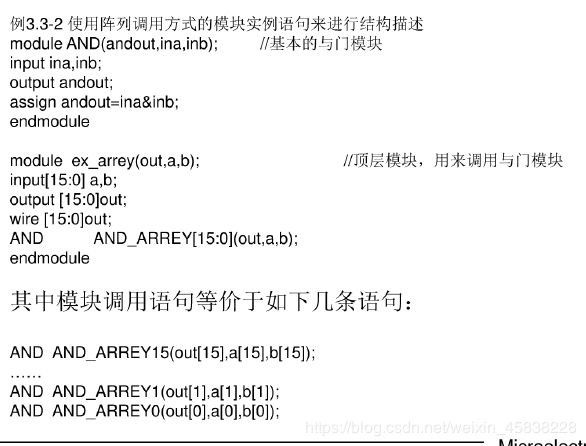

调用多个模块很少用,但我们想重复调用一个模块该如何操纵呢,通过阵列调用的方式格式为:

<被调用模块名><实例阵列名>[阵列左边界:阵列右边界](<端口连接表>)下面这个例子

2.模块端口对应方式

(1)端口位置对应方式

(2)端口名对应方式

模块名<参数值列表>实例名(端口名1<信号名1>, 端口名2<信号名2>,…, 端口名n<信号名n>))

(3)不同端口位宽的匹配

我们知道电路中不允许位宽不一样的信号进行操作,但当对应位宽不一样时,采用右端对齐,高位舍掉的原则:

在端口月端口表达式之间存在着一种隐含的连续赋值语句。因此当端口的端口的表达式的位宽不一致时,会进行端口的匹配,采用匹配规则与连续赋值时使用的规则相同。在上面的例子可以看出在模块ex1中in和out分别是6比特和4比特,但是调用的时候连线型变量c为3比特对应a,d5比特对应4比特b,出现了位宽不一致的情况下,所以右端对齐,高位舍掉的原则。

4.模块的参数值

首先明确一个概念,参数的存在方便我们在文件的top层进行数据的更改。在verilo hdl中用带有参数模块的实例语句修改参数值或者使用定于参数语句(defparam语句)修改参数值。

(1)使用带参数的模块实例语句修改参数值

在这种方法下,模块实例的本身就能指定的参数,语法格式是:

模块名<参数列表>调用名(端口名列表);

其中参数值列表又分为位置对应和名称对应

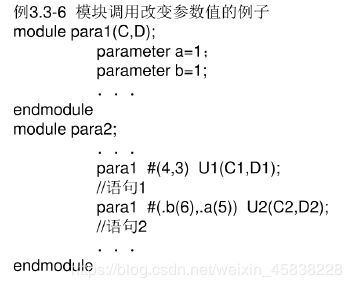

上面的例子可以看出,先设计para1模块,其中设定参数a,b都等于1。接下来调用模块para1。"#(4,3)"就是参数列表,U1位实例名,后面接端口列表。意思是将4赋给参数a,3赋给参数b,采用位置对应方式。名称对应方式略。

(2)使用定义参数语句defparam语句修改参数值

这种方法是独立于模块调用时的一种参数调用方式,格式为:

defparam 参数名1=参数值1.

..........

参数名n=参数值n;

这块很重要但我目前理解的不全,就不说了,可以看链接的视频,从30分钟开始看到34分34秒

https://www.bilibili.com/video/BV1zb411s7bY?p=7

3.3.2门级建模

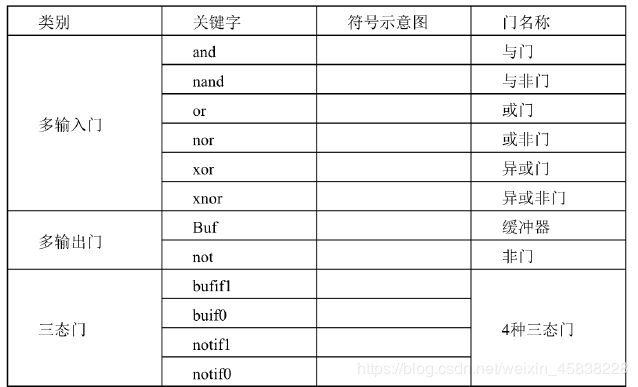

VERILOG HDL内置26个基本元件,14个门级元件,12个开关元件,26个基本元件如下图:

再加上

| 上拉、下拉电阻 | 允许定义drive strength | pullup、pulldonwn |

稍作解释三态门中buff0就是低电平控制,buf(buffer)代表驱动强度,加入电流不强,添加buffer。

这里重点介绍门级元件

(2)门级模块调用

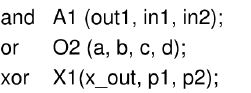

输入门元件调用的格式:

门类型<实例名>(<输出端口>,<输入端口1>,.....<输入端口n>);

注意输出端口只有一个,输入端口至多9个

多输入元件调用的格式为:

元件名<实例名>(<输出端口1>,<输出端口2>,.....,<输入端口>);

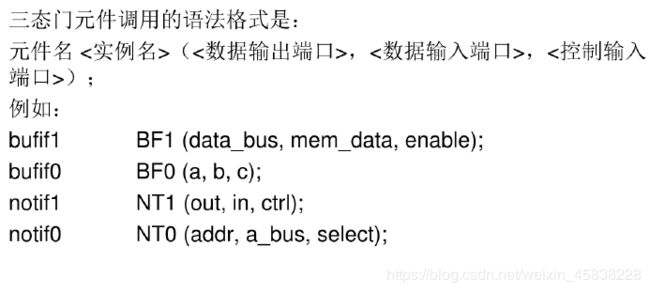

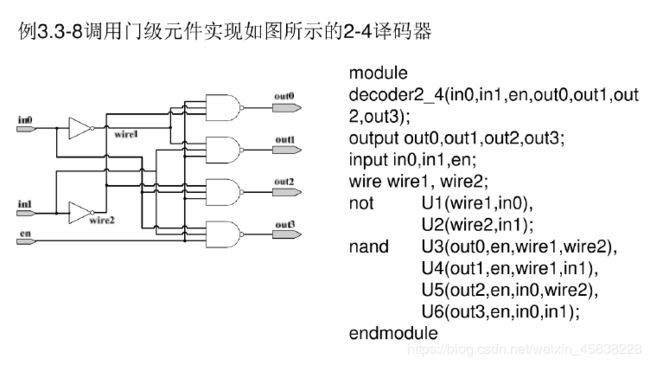

00,out0=1;01,out1=1;10,out2=-1;11,out3=0;

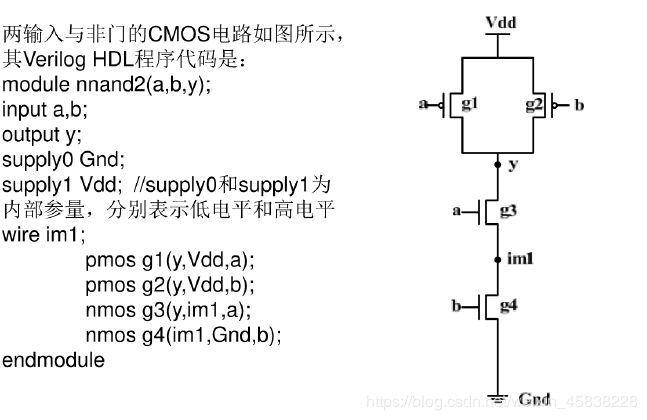

3.3.3开关级建模

Verilog HDL语言提供了十几种开关级基元, 它们是实际的MOS管的抽象表示。 这些开关级基元分为两大类:一类是MOS开关,一类是双向开关。每一大类又可分为电阻型(前缀用r表示)和非电阻型。在这主要讲以非电阻型开关为例, 介绍MOS开关和双向开关。

(1) MOS开关

MOS开关模拟了实际的MOS器件的功能, 包括nmos、 pmos、 cmos。

nmos和pmos的实例化语言格式是:

nmos或pmos 实例名 C out, data, control) ; corns开关的实例化语言格式是:

cmos 实例名 C out, data, ncontrol, pcontrol) ;

(2)双向开关

MOS开关只提供了信号的单向驱动能力, 为了模拟实际的具有双向驱动能力的门级开关, Verilog HDL语言提供了双向开关。 双向开关的每个脚都被声明为inout类型, 都可以作为输入驱动另一脚, 也可以作为输出

被另一脚驱动。

双向开关包括无条件双向开关 (tran) 和有条件双向开关 (tranif0、tranif1)。

无条件双向开关的例化语言格式是:

tran 实例名 (inout1 , inout2) ;

有条件双向开关示例化语言格式是:

tranifO或tranif1 实例名 Cinout1, inout2, control) ;

由于没有数电基础,最后一个例子以后学了再看,但第一个可以理解。写了两天终于写完了