学会Zynq(2)Zynq-7000处理器的配置详解

上篇中介绍了Xilinx FPGA嵌入式开发的基本概念和软件特性,并以Hello World为例给出了一个操作流程,熟悉该流程相当重要。上一篇中只是简单说明了每一步应该执行哪些操作,本文将详细介绍每一步的具体含义和涉及到的相关概念。

Zynq-7000配置

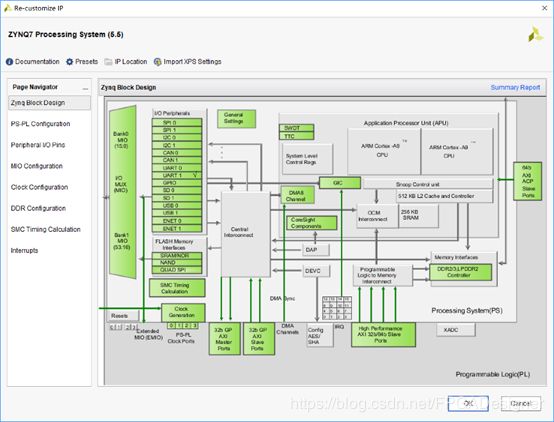

添加好ZYNQ7 Processing System IP核后,需要对其进行配置,双击弹出如下窗口。绿色部分表示ZYNQ PS部分中可配置的项目,可以双击转向相应的设置界面,也可以直接在左边的导航列表中选择。

顶部有4个按钮,Documentation查找与Zynq相关的文档;Presets保存或导入一些预设配置;IP Location显示了该IP所在路径;Import XPS Settings导入由XPS工程产生的XML文件,该文件包含对Zynq处理器的配置。XPS是老版ISE使用的嵌入式开发工具。

1. MIO与EMIO配置

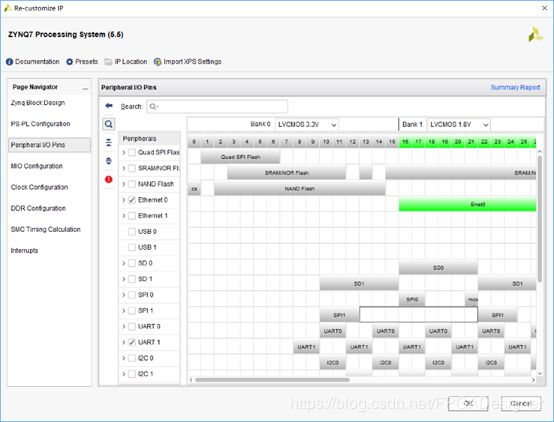

在Peripheral I/O Pins(如下图)或MIO Configuration中可以查看和配置I/O管脚。Zynq-7000器件的PS部分有超过20种可选的外设,设计者可以将这些外设直接与专用的复用I/O相连,通常称为MIO;也可以使用扩展的复用I/O,通常称为EMIO。

设计者可以配置MIO的电平标准,如果要使用某个外设,选中复选框即可(会感觉和STM32 CubeMX软件的使用有些相似)。PS的MIO划分在Bank0(pin0-15)和Bank1(pin16-53)两个电压域内,每个bank内的MIO可以独立编程,支持1.8、2.5、3.3V的CMOS单端模式,1.8V的HSTL差分模式。我们都知道每个bank的电压必须相同,但是不同管脚可以有不同的I/O标准。

2. 闪存接口

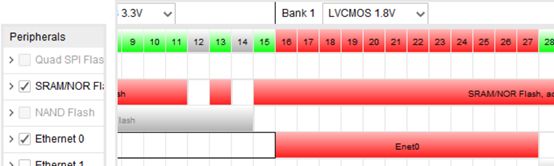

Zynq-7000支持Quad-SPI Flash、SRAM/NOR Flash和NAND Flash三种闪存,配置时只能选择其中一个。注意外设之间如果发生管脚冲突,会用红色提示。如下图SRAM和Enet0之间发生了冲突:

3. 时钟配置

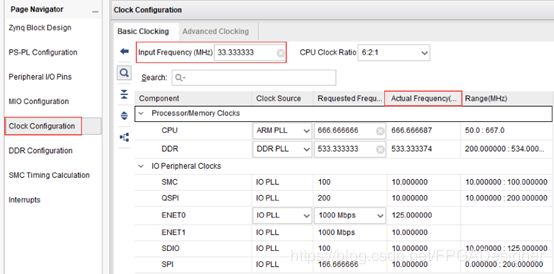

Clock Configuration中进行Zynq-7000器件的时钟配置。这里可以设置外设的时钟,PS上外设的时钟源可以由内部PLL生成,也可以来自外部时钟源。同一个PLL可能要产生多个频率,导致得到的频率不是完全准确,在Actual Frequency列中查看能够实现的实际频率。PS的输入频率范围限制在30~60MHz之间,通常都会选择33.33MHz,便于产生内部所需的时钟频率。

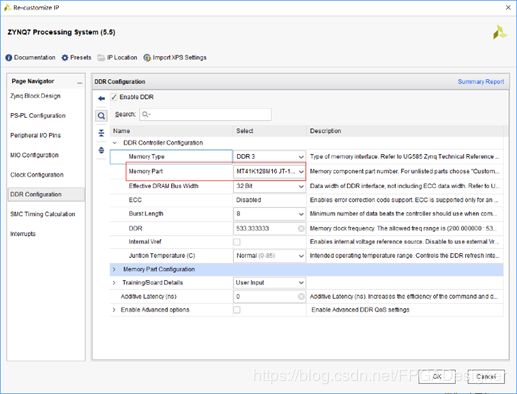

4. DDR配置

Zynq-7000的内存控制器支持DDR2、DDR3、DDR3L和LPDDR2,主要由三部分组成:

- DDRI:DDR接口,AXI内存端口接口。DDRI有4个64位同步AXI接口,可以同时为多个AXI主机提供服务。每个AXI接口都有一个专用FIFO。一个AXI端口专用于CPU和ACP的L2缓存;两个端口专用于AXI_HP接口;AXI互联网络上的其它主机共享第四个端口。

- DDRC:带有事务调动程序的核控制器,包含两个内容寻址存储器(CAMs),用于执行DDR数据服务调度,最大化DDR内存的效率。同时包含一个低延迟的“fly-by”通道,允许在不通过CAM的情况下访问DDR内存。

- DDRP:带有数字PHY(物理层)的控制器。PHY处理来自控制器的读、写请求,在目标DDR内存的时序约束下转换为特定信号。PHY利用来自控制器的信号产生内部信号,通过数字PHY连接到引脚。Zynq的DDR管脚在PCB上直接与DDR器件相连。

PS中DDR的大致工作流程为:根据请求等待时间、请求的紧急性、请求是否与前一个请求在同一页内,DDRI对来自8个端口(4个读、4个写)的请求进行仲裁,选择一个请求通过一个读写流接口传递到DDRC中,同时DDRP驱动DDR的事务。

在DDR Configuration中完成DDR控制器的配置,DDR型号要与开发板相符:

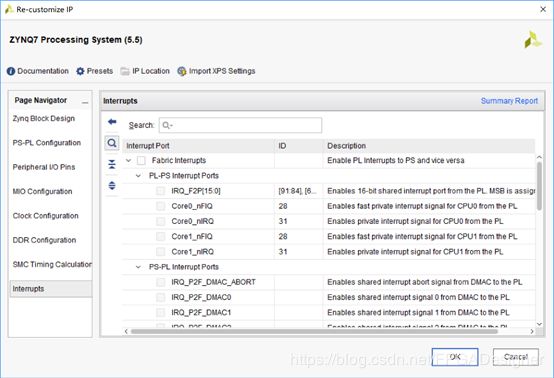

5. GIC中断控制器

在Interrupts中对通用中断控制器GIC(Generic Interrupt Controller)进行配置。GIC用于管理从PS和PL发送到CPU中的终端。当CPU接口接收一个新中断时,GIC以编程的方式启用、禁用、屏蔽与优先处理中断源,并将其发送到选定的CPU。此外,GIC还支持安全扩展,以实现安全感知系统。

目前,控制器基于ARM®GIC架构版本1.0。独立总线通过避免互联网络中出现临时阻塞访问寄存器,以实现快速读、写响应。中断分配器集中所有中断源,再将最高优先级的中断源分配到CPU。

当把一个中断定向到多个CPU时,GIC可以确保每次只有一个CPU接收中断。所有中断源包含一个独一无二的中断ID号,都有自己的可配置的优先级和目标CPU列表。

6. AXI_HP接口

4个AXI_HP接口为PL总线主程序提供了到DDR和OCM内存的高带宽数据通道,每个接口有两个用于读写通信的FIFO缓冲区。内存互连的PL将高速AXI_HP端口布线到两个DDR内存端口或OCM。AXI_HP接口也可以用作AXI_FIFO接口,利用其缓冲能力。

在PS-PL Configuration中的HP Slave AXI Interface中可以启用这些接口:

简而言之,这种接口为PL主机和PS内存(DDR或OCM)之间提供了一种高吞吐量数据通道。

7. AXI ACP接口

ACP接口允许对PL主机进行低延迟访问,带有可选的coherency和L1、L2缓存。从系统角度来看,ACP接口具有与APU CPU类似的连通性,因此ACP可以直接在APU块争取资源。在PS-PL Configuration中的ACP Slave AXI Interface中可以启用该接口:

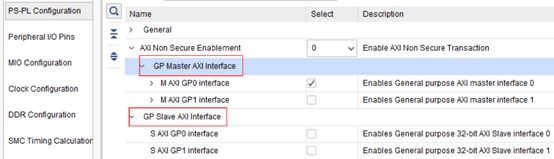

8. AXI GP接口

这种接口将主机与从机端口直接相连,不需要额外的FIFO缓冲。AXI_HP接口带有精心设计的FIFO缓冲,以提高性能和吞吐量。与其不同,由于没有FIFO,AXI_GP接口的性能受到主机和从机端口的限制。这种接口用于往往不会太关注性能的一般用途。在PS-PL Configuration中的GP Master/Slave AXI Interface中可以启用该接口:

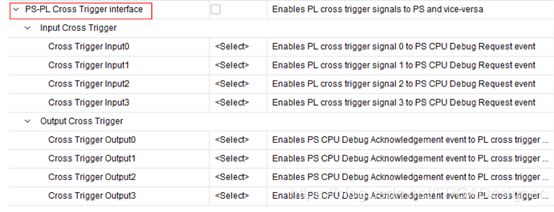

9. PS-PL交叉触发接口

Zynq内部有个基于交叉触发机制的嵌入式交叉触发器ECT。该组件基于CoreSight技术,通过发送触发器和接收触发器来和其它组件交互。ECT主要由交叉触发矩阵(CTM)和交叉触发接口(CTI)组成。

一个或多个CTM组成一个具有多个频道的广播网络,一个CTI在一个或多个通道上监听某一事件,将接收到的事件映射到触发器,然后将触发器发送到一个或多个与CTI相连的CoreSight组件中。CTI也可以组合和映射来自多个CoreSight组件的触发器,并将其作为事件在一个或多个频道中广播。

在PS-PL Configuration中的PS-PL Cross Trigger Interface中可以启用该功能:

Zynq中的PL部分

我相信不少人在没接触Zynq前会产生这样的疑问:Zynq能否当作一个纯FPGA来使用?答案当然是可以的。如果不用Zynq中的ARM处理器,则开发流程与7系列FPGA完全相同。但Zynq的闪存接口是与PS部分相连的,因此我们不能将“纯FPGA”程序固化到板子上,必须由处理器来引导。

Zynq中的可编程逻辑部分(PL)采用的也是与7系列相同的架构,下面还是给出其中包含的资源种类:

- 可配置逻辑块(CLB),包含带有存储功能的6输入查找表(LUT)、寄存器与移位寄存器功能、可级联的加法器。

- 36Kb的块RAM,双端口,最高支持72bits位宽,可配置为双18Kb,带有可编程的FIFO逻辑电路和内部错误纠正电路

- 数字信号处理DSP48E1 Slice单元,12×18的2进制补码乘法器、累加器,高分辨率(48bit)的信号处理器,带有25-bit的预加器以优化对称结构滤波器应用。此外还包括可选的流水线、ALU和专用级联总线等高级特性。

- 时钟管理单元,超高速缓冲器与低斜率时钟分布的布线,实现频率综合和相移功能,产生低抖动时钟,还带有抖动滤波。

- 可配置I/O,基于高性能SelectIOTM技术,封装内有高频去耦电容,以增强信号完整性;数控阻抗,可配置为三态以实现最低功耗,或满足高速I/O操作;HR(大范围) I/O支持1.2V到3.3V;HP(高性能)I/O支持1.2V到1.8V,如7z030、7z045、7z100系列。

- 模数转换器XADC,双12-bit、1MSPS,多达17个灵活的、用户可配置的模拟输入,可用于片内或片外测量。带有片内温度传感器(±4℃)和电源供应传感器(±1%)。通过JTAG可获取ADC测量结果。

除了这些基本单元,7z030、7z045、7z100等高端器件内部还集成了低功率的Gbit收发器、PCI-E接口。

根据上文的实验,我们知道在用SDK进行软件设计前先要在IP Integrator中完成硬件设计。设计者可以使用IP Packager工具将自己的设计封装为IP,导入到IP Catalog中,之后便可以在设计中调用该IP。