System Generator从入门到放弃(二)-Digital Filter

System Generator从入门到放弃(二)-Digital Filter

文章目录

- System Generator从入门到放弃(二)-Digital Filter

- 一、Digital Filter

- 1、简介

- 2、产生正弦信号

- 2.1 本部分设计使用到的block

- 3、数字滤波器的设计

- 3.1 本部分设计使用到的block

- 3.2 数字滤波器设计

- 3.3 FPGA系统配置

- 3.3 开始仿真

- 3.3 将设计导出到FPGA

- 3.3 打开Vivado示例工程

- 4、FDATool block的使用

- 5、生成说明文档与testbench

- 5.1 生成说明文档

- 5.2 生成testbench

- 6、资源分析与时序分析

- 6.1 查看分析结果

- 6.2 时序分析

- 6.3 资源分析

- 6.4 资时序/资源分析失败的说明

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

一、Digital Filter

1、简介

数字滤波器的功能是对输入离散信号的数字代码进行运算处理,以达到改变信号频谱的目的。

数字滤波一般分为时域滤波和频域滤波。频域滤波是将时域变换到频域,对相应频率做调整,然后反变换到时域,抛开FFT的话过程相对简单。在这里我们主要说时域滤波。

时域滤波器分为无限脉冲响应IIR和有限脉冲响应FIR两种。IIR滤波器的优点是可以用较低的阶数(相比同样指标的FIR滤波器)实现滤波器。缺点一:不是线性相位,只能用于对相位信息不敏感的信号(如音频信号)。缺点二:有可能是不稳定的。在设计的过程中为了保持稳定性和因果性,要求z变换所有的极点都必须位于单位圆内。但即使是这样,也可能由于量化舍入等因素引起的误差最终导致IIR滤波器不稳定。FIR滤波器的优点是可以设计成具有线性相位的,并且是稳定的(FIR滤波器除原点处外没有极点),缺点是阶数高,也就是说计算量大。

具体介绍大家可以查阅相关资料。

2、产生正弦信号

2.1 本部分设计使用到的block

Xilinx block

- 无

其它block

- Sin Wave(Simulink->Sources):生成正弦波

- Add(Simulink->Math Operations):加法器

- Scope(Simulink->Commonly Used Blocks):示波器

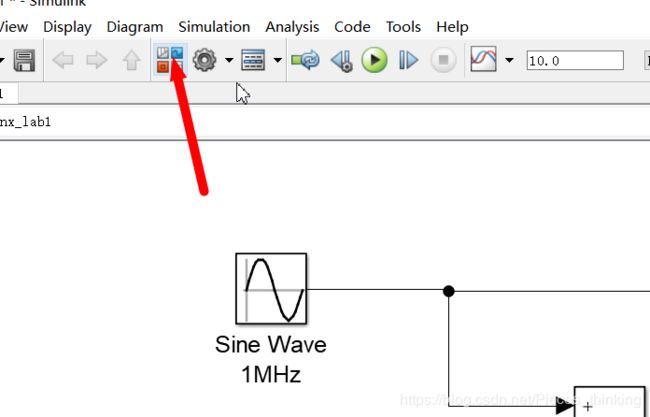

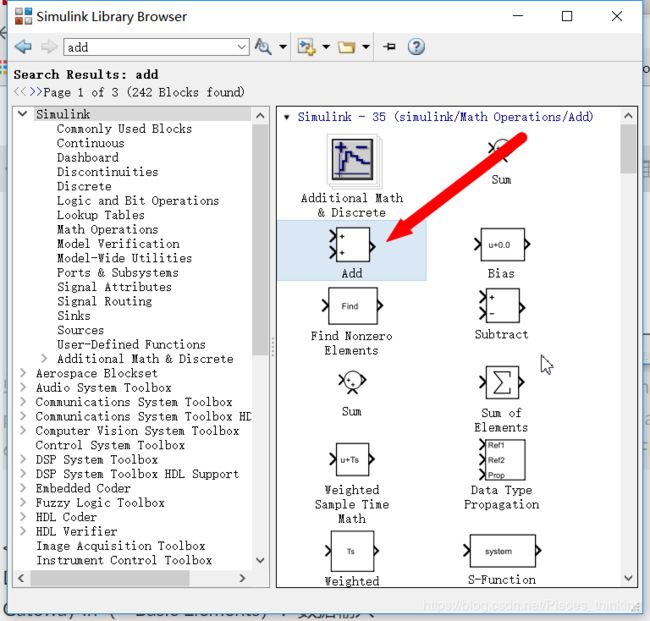

在库中在库中找到Sine Wave、add、scope,分别添加带哦model中,如下:

添加完后如下:

修改相关属性:

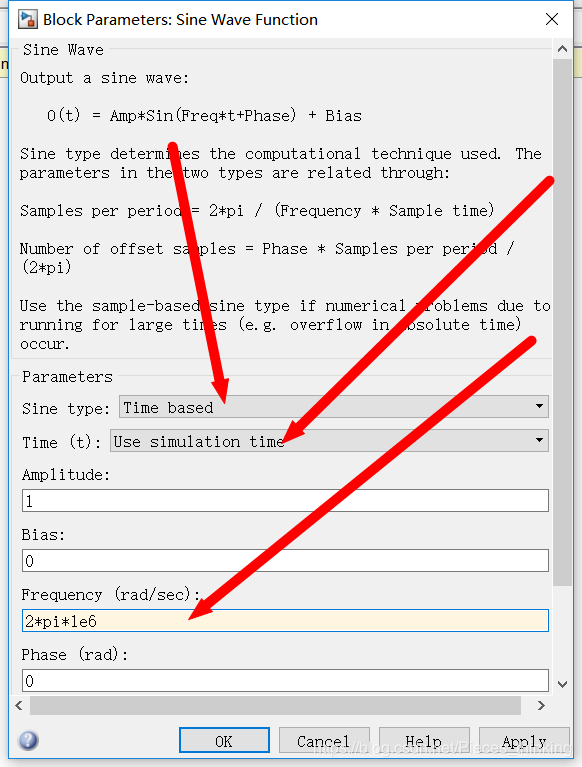

双击Sine Wave,可以设置正弦波的幅度、电平偏置、频率、初相、采样时间等信息。这里只需要将频率分别设置为1MHz(2pi1e6)和9MHz(2pi9e6)。

双击Add,“List of signs”设置加法器的输入端口,“++”表示两个输入相加(“±”则表示A-B)。

双击打开示波器窗口,在View->Configuration Properties:Scope中(或者如下图方式进行设置),将Number of input ports设置为3(观察3路信号);点击Layout,选择3*1排列方式(每路信号分开显示):

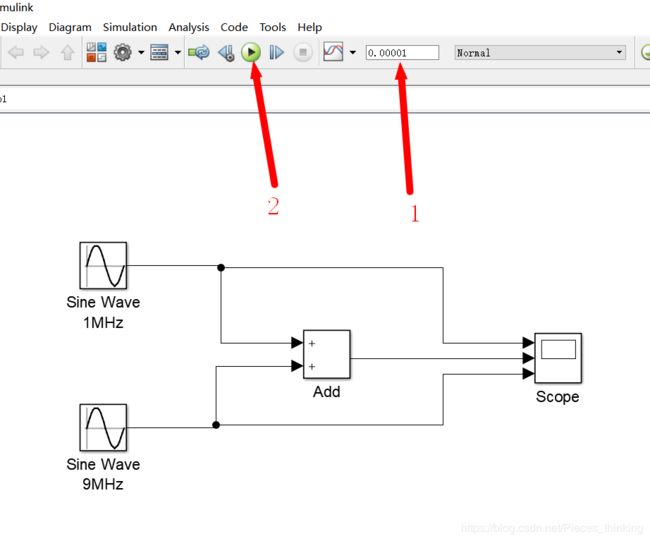

连线,结果如下。 将Simulink仿真时间设置为0.00001(时间太长会导致仿真很慢),点击运行,Simulink窗口的右小角可以观察到运行状态。运行结束后打开Scope:

第一个为1Mhz信号,第三个为9MHz信号,中间为两路信号叠加。接下来设计一个LPF滤除掉9MHz频率分量。

PS:双击Scope可能看到的波形如下,是三路信号混合在了一起,想要分开三路进行查看,View->Layout,设置成三行模式。

最终的结果如下,第一个为1Mhz信号,第三个为9MHz信号,中间为两路信号叠加。接下来设计一个LPF滤除掉9MHz频率分量。

3、数字滤波器的设计

3.1 本部分设计使用到的block

Xilinx block

- Digital FIR Filter(->DSP):数字滤波器

- Gateway In(->Basic Elements):数据输入

- Gateway Out(->Basic Elements):数据输出

- System Generator(->Basic Elements):系统管理

- FDATool(->DSP):滤波器设计

其它block

- Sin Wave(Simulink->Sources):生成正弦波

- Add(Simulink->Math Operations):加法器

- Scope(Simulink->Commonly Used Blocks):示波器

- Zero-Order Hold(Simulink->Discrete):零阶保持器

- Spectrum Analyzer(DSP System Toolbox->Sinks):频谱分析仪

3.2 数字滤波器设计

我们知道,Simulink中的仿真模型为连续时间系统,数据格式多种多样;而FPGA中为离散时间系统,数据必须用一定的位数进行量化。两者之间必须要进行从连续到离散的转换、数据格式的转换,否则无法进行正确的FPGA设计。Xilinx Blockset中提供了相应的解决方案。

添加一个Gateway In和一个Gateway Out模块到model中,再添加一个Digital FIR Filter模块。按照加法器输出->Gateway In->Digital FIR Filter->Gateway Out的顺序依次连接。

添加如下block到model并按图中方式进行连线。

双击打开Gateway In模块的属性窗口:

这个模块可以Simulink到FPGA之间的数据转换。将Sample period设置为“1/20e6”(20MHz采样率),完成连续时间到离散时间的转换;设置Out Type完成数据格式的转换。这里保持为默认的二进制带符号数补码、定点数的设置。Quantization中可以设置量化方式为Truncate(截断)或者round(四舍五入)。

Gateway In的设置会自动传递到Gateway In和Gateway Out之间的整个系统中,因此不需要再设置其它模块的采样率与数据格式。

Digital FIR Filter设置

频率参数

- Units = MHz

- Fs = 20

- Fpass = 1.5

- Fstop = 8.5

Magnitude Specifications

- Units = dB

- Apass = 0.01

- Astop = 100

两种方式,其中第一种方式,在其他模块没有FDATOOL工具时,需要使用第二种方式。

第一种方式

双击Digital FIR Filter: 选中“Use FDA Tool as coefficient source”,点击“FDA Tool”按钮,会弹出FDATOOL窗口,设置采样率为20Mhz,通带截止频率1.5MHz,阻带截止频率8.5Mhz,通带衰减0.01dB,阻带衰减100dB,点击“Design Filter”设计后退出。

第二种方式

第二种方式是使用FDATool,这部分会在后面介绍。

3.3 FPGA系统配置

以上仅仅是完成了数字滤波器的设计,但是仍然没有建立起模型与FPGA之间的实质联系。添加System Generator模块到model中,这个block便是配置与FPGA相关的系统参数。这个block的配置会应用到Gateway In和Gateway Out之间的所有模块中。双击打开,切换到Clock标签:

- a. Specify an FPGA clock Period of 50 ns (1/20 MHz).

- b. Specify a Simulink system period of 1/20e6 seconds.

- c. From the Perform analysis menu, select Post Synthesis and from

Analyzer type menu select

FPGA clock period设置为50ns,Simulink system period设置为1/20e6(都是20Mhz)。Perfor analysis设置为Post Sythesis,Analyzer type设置为Resource,在系统综合后会进行资源使用情况的分析。

3.3 开始仿真

使用Simulink完成FPGA中的DSP系统设计,最大的好处就是仿真极其方便(包括后面文章会用到的ModelSim协同仿真、硬件协同仿真等特性)。

添加一个Scope观察Gateway Out输出的波形(滤波后波形),再添加两个Spectrum Analyzer观察滤波前后的信号频谱。Spectrum Analyzer这个block必须输入离散的数据,因此在加法器输出后需要经过一个零阶保持器Zero-Order Hold,转换为离散数据后再输入到Spectrum Analyzer中。零阶保持器的采样率设置为1/20e6(20Mhz)。

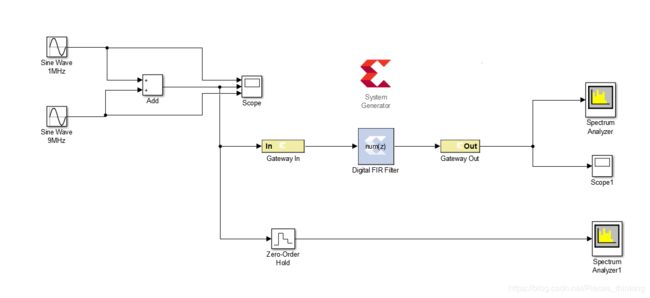

系统的整体连接框图如下:

注意,虽然Gateway In转换后的数据也是离散的,但是Spectrum Analyzer不能接入到这里,否则会出现错误。Gateway In和Gateway Out之间只能连接其它Xilinx Blockset中的模块。

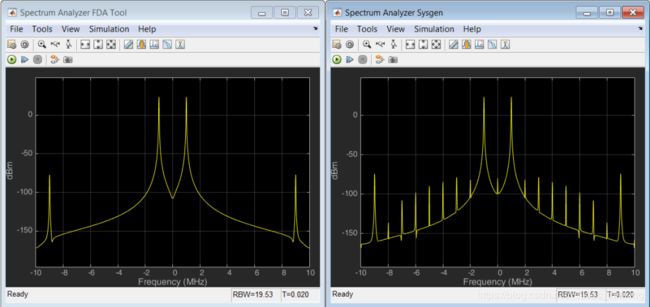

将仿真时间设置为0.0005(Spectrum Analyzer必须有足够多的采样数据才能计算出频谱),输出信号的波形如下所示,经过滤波后仅剩下1MHz的单频分量,且数据为离散值。

可以看到经过滤波后,9Mhz的频率分量有大约100dB的衰减(频谱呈对称性),设计符合预期。

3.3 将设计导出到FPGA

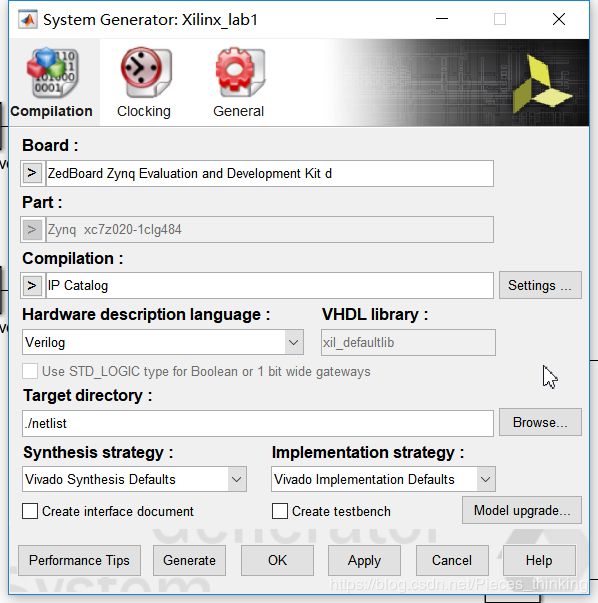

仿真验证功能正确后,需要将设计导出到FPGA中,这个步骤仍然要借助System Generator这个block。双击打开,切换到Compilation标签下,这里可以设置使用的开发板(Board,只能选择Xilinx官方开发板)、FPGA芯片(Part),也可以设置导出设计的硬件描述语言(Verilog或VHDL)。点击“Generate”,System Generator会将Gateway In和Gateway Out之间的模块导出到FPGA中。运行结束后,根据前面的设置,弹出了资源分析报告:

在slx同文件夹下,生成netlist文件夹。其中sysgen子文件夹包含了导出的Verilog或VHDL设计文件;ip子文件夹是设计导出的IP核形式;ip_catalog子文件夹包含一个调用该IP核的Vivado的示例工程。

3.3 打开Vivado示例工程

在ip_catalog文件夹下打开Vivado工程,其中顶层文件如下:

//Copyright 1986-2017 Xilinx, Inc. All Rights Reserved.

//--------------------------------------------------------------------------------

//Tool Version: Vivado v.2017.4 (win64) Build 2086221 Fri Dec 15 20:55:39 MST 2017

//Date : Sun Nov 4 02:06:37 2018

//Host : LAPTOP-8E6RLG3I running 64-bit major release (build 9200)

//Command : generate_target xilinx_lab1_bd.bd

//Design : xilinx_lab1_bd

//Purpose : IP block netlist

//--------------------------------------------------------------------------------

`timescale 1 ps / 1 ps

(* CORE_GENERATION_INFO = "xilinx_lab1_bd,IP_Integrator,{x_ipVendor=xilinx.com,x_ipLibrary=BlockDiagram,x_ipName=xilinx_lab1_bd,x_ipVersion=1.00.a,x_ipLanguage=VERILOG,numBlks=1,numReposBlks=1,numNonXlnxBlks=1,numHierBlks=0,maxHierDepth=0,numSysgenBlks=1,numHlsBlks=0,numHdlrefBlks=0,numPkgbdBlks=0,bdsource=SYSGEN,synth_mode=OOC_per_IP}" *) (* HW_HANDOFF = "xilinx_lab1_bd.hwdef" *)

module xilinx_lab1_bd

(clk,

gateway_in,

gateway_out);

(* X_INTERFACE_INFO = "xilinx.com:signal:clock:1.0 CLK.CLK CLK" *) (* X_INTERFACE_PARAMETER = "XIL_INTERFACENAME CLK.CLK, CLK_DOMAIN xilinx_lab1_bd_clk, FREQ_HZ 100000000, PHASE 0.000" *) input clk;

(* X_INTERFACE_INFO = "xilinx.com:signal:data:1.0 DATA.GATEWAY_IN DATA" *) (* X_INTERFACE_PARAMETER = "XIL_INTERFACENAME DATA.GATEWAY_IN, LAYERED_METADATA undef" *) input [15:0]gateway_in;

(* X_INTERFACE_INFO = "xilinx.com:signal:data:1.0 DATA.GATEWAY_OUT DATA" *) (* X_INTERFACE_PARAMETER = "XIL_INTERFACENAME DATA.GATEWAY_OUT, LAYERED_METADATA xilinx.com:interface:datatypes:1.0 {DATA {datatype {name {attribs {resolve_type immediate dependency {} format string minimum {} maximum {}} value {}} bitwidth {attribs {resolve_type immediate dependency {} format long minimum {} maximum {}} value 37} bitoffset {attribs {resolve_type immediate dependency {} format long minimum {} maximum {}} value 0} real {fixed {fractwidth {attribs {resolve_type immediate dependency {} format long minimum {} maximum {}} value 33} signed {attribs {resolve_type immediate dependency {} format bool minimum {} maximum {}} value true}}}}}}" *) output [36:0]gateway_out;

wire clk_1;

wire [15:0]gateway_in_1;

wire [36:0]xilinx_lab1_1_gateway_out;

assign clk_1 = clk;

assign gateway_in_1 = gateway_in[15:0];

assign gateway_out[36:0] = xilinx_lab1_1_gateway_out;

xilinx_lab1_bd_xilinx_lab1_1_0 xilinx_lab1_1

(.clk(clk_1),

.gateway_in(gateway_in_1),

.gateway_out(xilinx_lab1_1_gateway_out));

endmodule

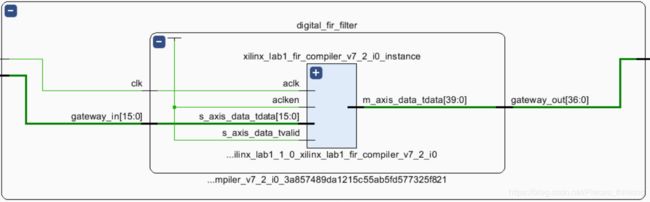

sysgen_filter_bd是调用System Generator导出的IP核的子模块。16Bits输入数据经过滤波后得到36Bits的输出结果。运行RTL ANALYSIS,打开RTL视图,找到最底层:

可以看到其本质上仍然是调用了FIR Compiler IP核来实现数字滤波,只不过我们是在Simulink中完成的设计。在其它工程中可以像示例工程一样调用这个System Generator导出的IP核,来完成特定的DSP系统功能。

理论上经过Simulink中的仿真,已经可以确定设计的正确性。但这是使用System Generator完成的第一个实验,本文仍然在Vivado中进行一次仿真,增强使用者对System Generator设计的信心。使用MATLAB产生一个1MHz+9Mhz的正弦叠加信号,导入到TXT文件中。编写testbench读取txt文件,对信号进行滤波。Vivado中的仿真结果如下图所示:

可以看到经过滤波后,只剩下1Mhz的单频信号,与Simulink中的仿真结果完全一致。

总而言之,从这个实验出发,博主认为在System Generator中完成DSP系统设计与直接在Vivado环境下进行DSP系统设计相比,有两个优点:

- 更强大、更方便的仿真环境;

- 系统级设计角度,无需关心RTL设计细节以及一些IP核的具体使用方法。

4、FDATool block的使用

前文中我们在Digital FIR Filter block的配置界面直接调用FDATool工具完成FIR滤波器的设计。但是有一些滤波器block,如2n-tap MAC FIR Filter,并没有提供这样一个接口。Xilinx Blockset中单独提供了一个FDATool block,可以提供更广泛的使用。

添加FDATool block到model中,配置完成后点击“Design Filter”。其它模块调用这个FDATool设计的滤波器可以借助两个函数:

- xlfda_numerator(‘FDATool’):提取滤波器系数的分子

- xlfda_denominator(‘FDATool’):提取滤波器系数的分母

对于FIR滤波器而言,分母为1,只提取分子即可。如下图所示:

所有滤波器block的系数都可以用这种方式设置。

5、生成说明文档与testbench

5.1 生成说明文档

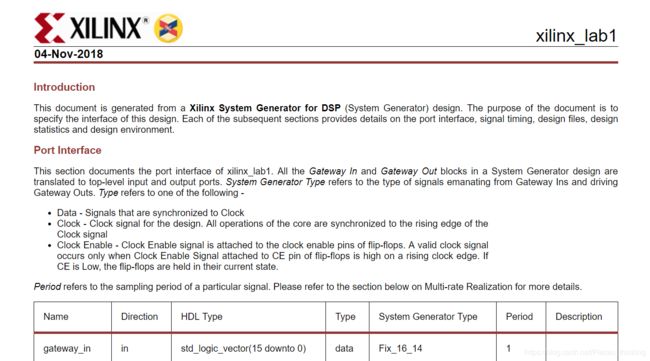

本文在上一篇设计的数字滤波器模型基础上进行修改。打开System Generator这个block,在Compilation标签下:

选中“Create interface document”,在点击Generate导出设计后,在netlist/sysgen文件夹下会生成一个HTM文件。用浏览器打开如下:

5.2 生成testbench

在System Generator block的Compilation标签下选中“Create testbench”,如第一幅图所示。在点击Generate导出设计时,软件会根据选择的硬件描述语言生成对应的testbench(在netlist/sysgen文件夹下):

●“Verilog“对应”name_tb.v“文件

●“VHDL“对应”name_tb.vhd“文件

name为simulink模型的名字,我这里为“sxilinx_lab1_tb“。在生成的Vivado示例工程中会自动添加这个testbench文件:

在这个testbench中包含4个子模块:时钟生成模块xlclk、测试数据输入模块xltbsource、模块数据输出模块xltbsink和IP核设计文件sysgen_filter_0。最后在顶层模块中调用4个子模块,组成一个完整的测试平台(在“Testbench编写指南系列”中会解析这种testbench编写方式)。

仿真结果与上一部分完全一致。这是因为System Generator工具在生成testbench文件时将simulink环境中接入到Gateway In block的数据存储到dat文件中,在testbench中调用。而我们自己编写testbench时需要设计M文件产生信号,再用HDL语言设计仿真过程。可见System Generator的便利与强大。

6、资源分析与时序分析

6.1 查看分析结果

这部分继续在上面设计的数字滤波器模型基础上运行分析。System Generator集成了时序分析和资源分析功能,以确保在simulink中设计的DSP系统导出到FPGA环境中能够正确运行。其本质上仍然是在后台调用Vivado进行分析,System Generator只是读取了分析结果并显示出来。

设计完成并且Simulink运行完毕后,打开System Generator这个block,切换到Clock标签下:

Perform analysis中可以设置

- None:不进行分析;

- Post Synthesis:综合后进行分析;

- Post Implementation:实现后进行分析。

Analyzer type中可以设置

- “Resource”(进行资源分析)

- “Timing”(进行时序分析)

注意在Perform analysis设置好,并且导出设计到FPGA后,可以切换Analyzer type,并且点击右边的“Launch”查看两种报告。但修改设计和修改Perform analysis参数后必须重新运行才能生成最新的报告。

综合后和实现后的资源分析和时序分析分别如下。时序报告中可以看到每一条时钟路径的情况(本设计中只有一条);资源报告中可以看到每一个模块的资源消耗(本设计只有一个模块)。可以看到综合后与实现后的资源消耗情况、时序情况有些差异:

6.2 时序分析

System Generator集成的静态时序分析功能提供了如下特性:

- 点击每一列的指标名称,可以选择升序/降序排列;

- 时序不满足时,相应的路径Slack值为负数,且显示为红色;

- 交叉定位功能:时序报告中选中某一路径,Simulink模型中对应的部分会高亮显示(时序满足为绿色;不满足为红色),这可以帮助设计者更快的找到和修改时序错误。

如下图:

- 时序不满足时,可以考虑修改设计(如增加一些单元的Latency,以资源换速度),或者更换综合策略/实现策略。

在System Generator block的Compilation标签下可以设置“Synthesis strategy”和“Implementation strategy”。列表中有几种Vivado提供的策略,也可以在Vivado中添加好用户自定义的策略,在System Generator中调用。

6.3 资源分析

System Generator集成的资源分析功能提供了如下特性:

- 点击每一列的指标名称,可以选择升序/降序排列;

- BRAMs(包括RAMB36E、FIFO36E、RAMB18E、FIFO18E0资源);DSPs(包括DSP48E、DSP48E1、DSP48E2资源);Registers(包括寄存器和触发器,以FD和LD开头的资源);LUTs(所有的查找表);

- 交叉定位功能:资源报告中选中某一模块,Simulink模型中对应的部分会高亮显示(黄色),如下图:

- 资源消耗超过FPGA芯片总资源时,可以考虑修改设计,或者更换综合策略/实现策略。这里与时序分析部分相同。

6.4 资时序/资源分析失败的说明

绝大多数情况下,时序分析和资源分析都能得到正确的结果,但有时在Generate生成结束后,会提示一个Error,无法获取结果数据。

失败的原因一般都是如下情况:在同一目录下有多个slx文件,但是所有的slx文件设置的输出目录都相同(比如都是默认的./netlist)。在导出第一个slx文件时是可以正确运行时序/资源分析的;但在导出第二个slx文件的设计时,就会报错。原因便是不同的模型向同一目录下导出设计。在设置路径时要注意。