基于Quartus Prime Std 18.0的FPGA基础开发流程

基于Quartus Prime Std 18.0的FPGA基础开发流程

本文原始文档及代码工程上传至https://download.csdn.net/download/botao_li/10797443

也许对新入门FPGA的朋友有所帮助

软件版本

Quartus Prime Standard Edition 18.0 Windows

安装

进入Intel官方网站,打开左上角的产品菜单

选择FPGAs和可编程的设备

选择设计工具和软件

在页面下方选择下载

在下载页面根据器件选择版本,最好选择直接下载

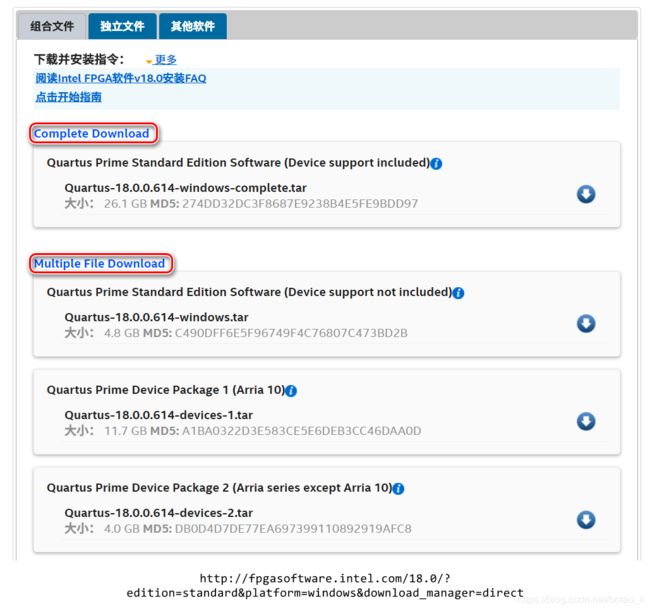

一般情况在“组合文件”中选择Complete Download就可以了,但是如果为了节约磁盘空间,可以在Multiple File Download中选择Quartus软件和必要的Device Package。如果对Quartus软件非常了解,根据开发需要在“独立文件”和“其它软件”中选择下载。

下载完成后将所有文件解压至同一文件夹下,运行QuartusSetup*.exe可执行文件,根据提示安装。该安装文件会自动查找同一文件夹下的软件组件和Device Package。(下图内容中的软件组件可能与默认的安装包不同)

流程

1. 建立工程

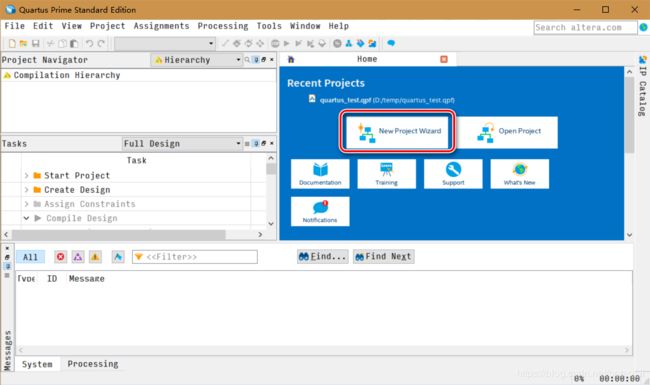

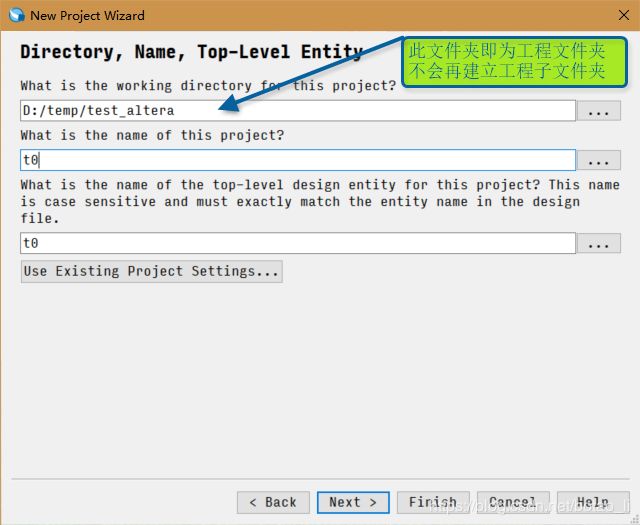

启动Quartus,在Home项面或者File菜单项打开New Project Wizard

后续配置依照提示完成,选择Finish完成。

2. 配置多处理器编译

在Assignments菜单选择Settings项,弹出对话框后进入Compilation Process Settings页,选中Use all available processors或者设置Maximum Processors allowed

2. 添加HDL文件

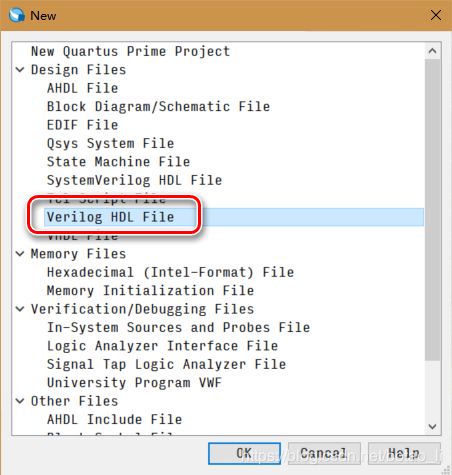

在File菜单选择New或者用Ctrl+N打开新建对话框,选择Verilog HDL File

弹出文本编辑器

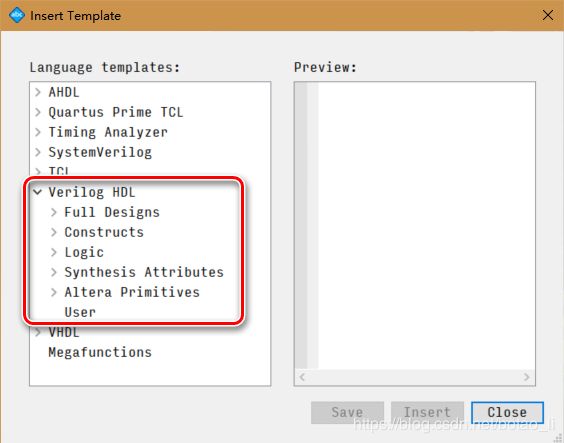

右键菜单中可以选择Inser Template添加模板

写入Verilog代码,并且将文件保存为与顶层实例相同的名称

3. 添加IP

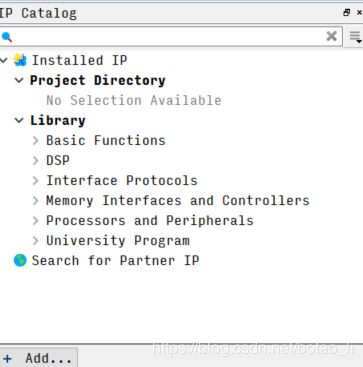

在Tools菜单打开IP Catalog

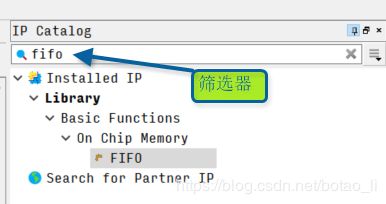

选择需要添加的IP,以FIFO为例,可以在筛选器中输入fifo

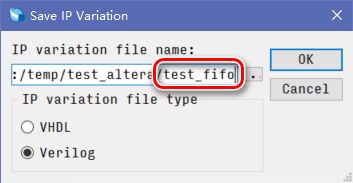

双击IP名称,弹出对话框,输入IP名称

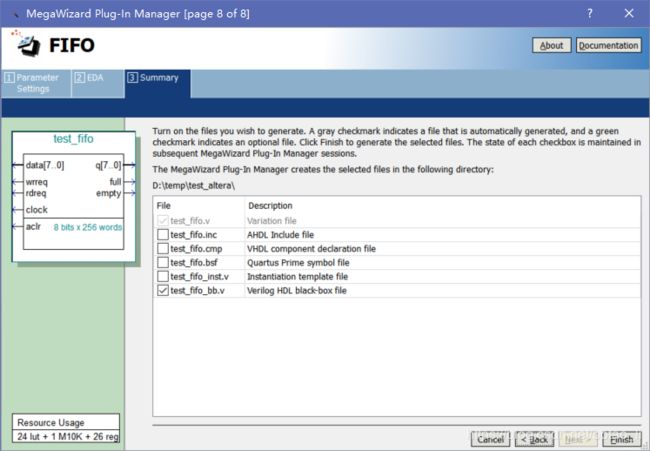

在随后弹出的MegaWizard中配置IP

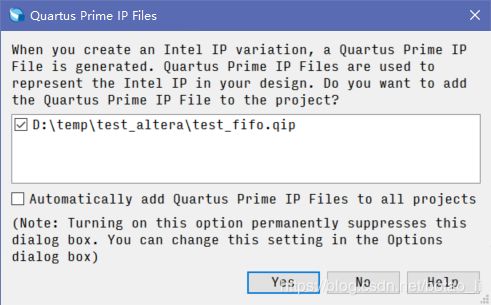

根据提示将IP添加至工程

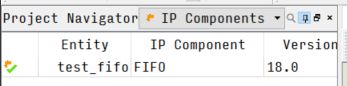

之后在Project Navigator框的IP Components页可以看到刚才生成的IP

在Project Navigator框内右键菜单点击IP选择Edit in Parameter Editor或者双击IP将打开MegaWizard配置对话框

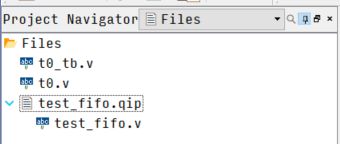

在Project Navigator框的Files页可以查看IP文件,包括qip和v,其中v文件可以用于查看IP例化端口

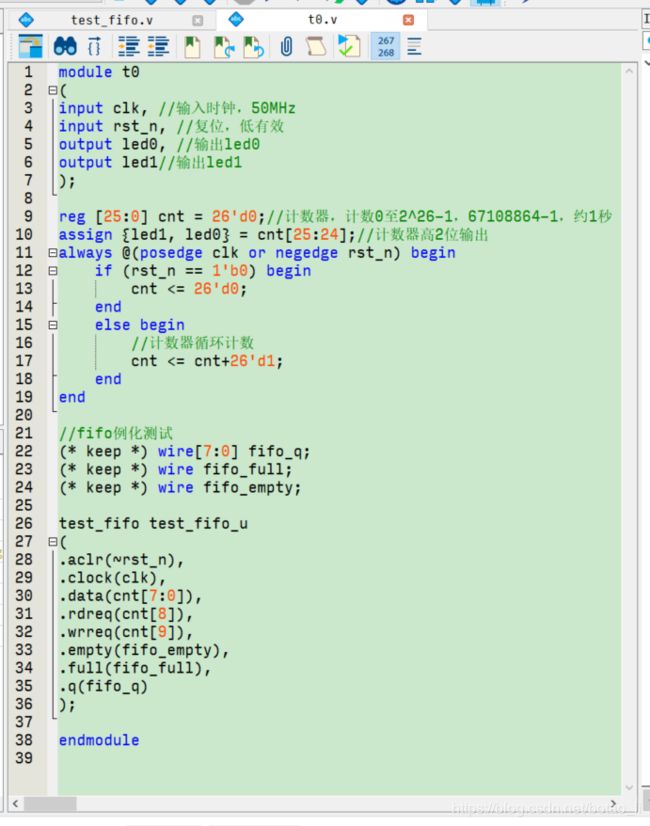

在HDL文件中加入fifo例化测试代码

4. 仿真

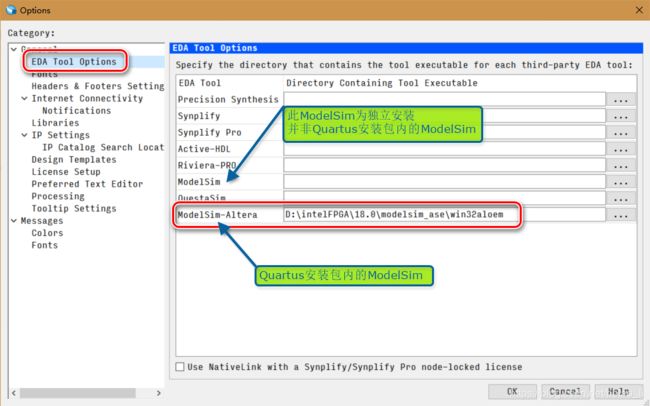

打开Tools菜单的Options对话框,设置ModelSim路径

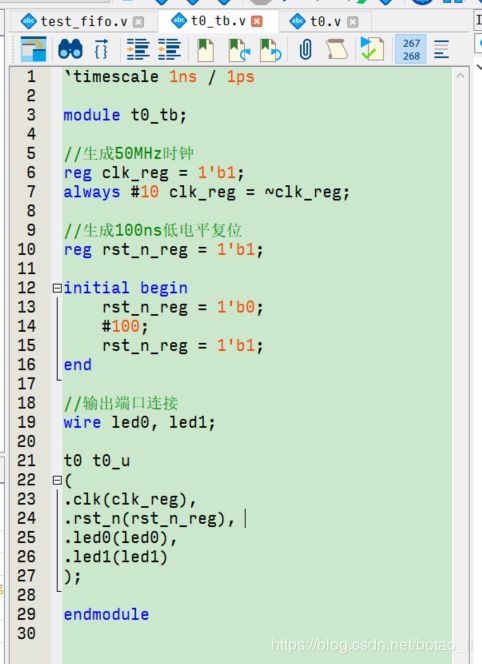

在新建对话框添加Verilog HDL File作为Test Bench

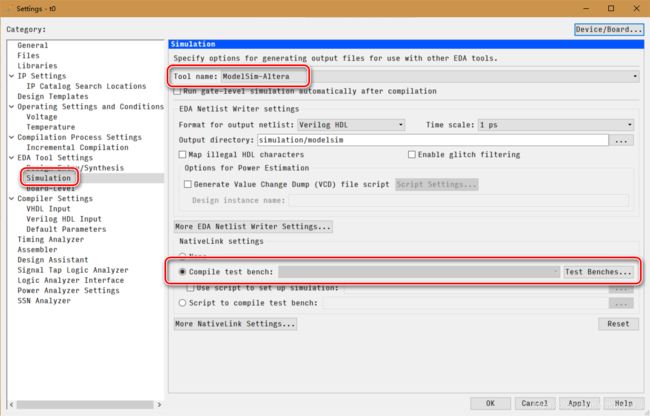

在Assignment菜单的Settings对话框,进入Simulation页设置仿真工具及Test Bench

点击Test Benches按钮弹出对话框,按下New按钮

设置Test Bench

Tools菜单选择Run Simulation Tool的RTL Simulation,启动ModelSim执行仿真。此处不再具体说明ModelSim的使用方法。

7. 综合

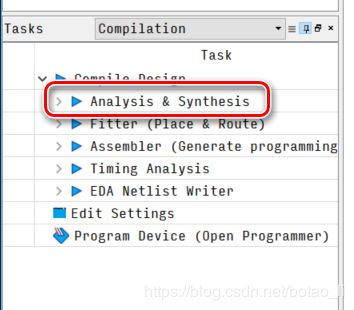

在Task框内双击Compile Design下的Analysis & Synthesis

完成综合后左侧出现绿色勾

![]()

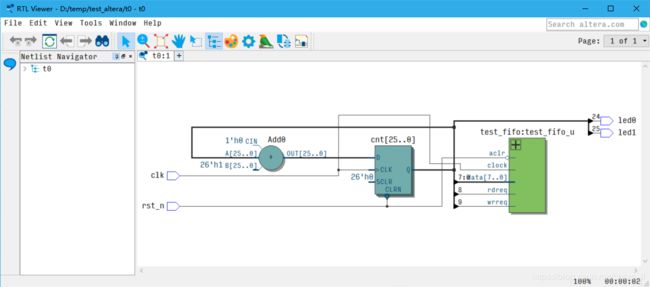

在Tools菜单Netlist Viewers项中的RTL Viewer可以查看生成网表

5. 管脚约束

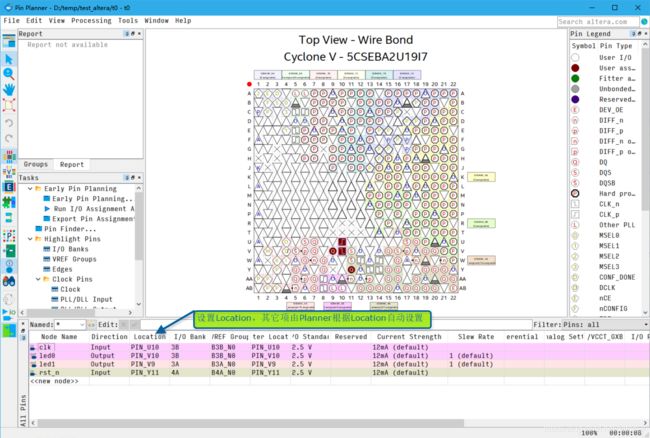

选中Assignments菜单Pin Planner项,设置顶层管脚的位置

6. 时钟约束

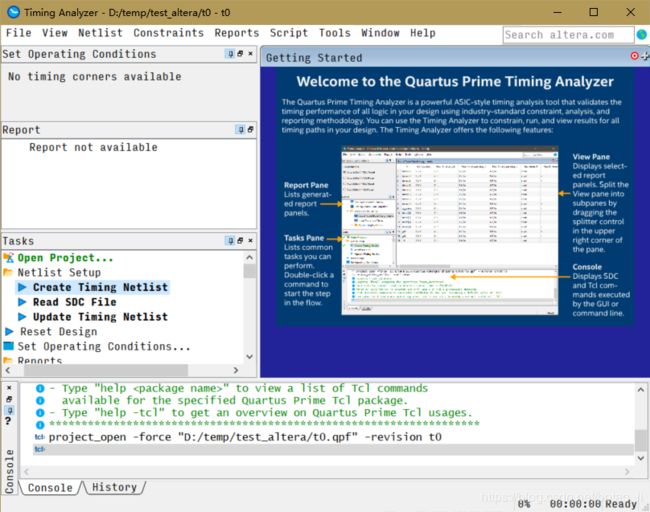

在Tasks框的Timing Analysis内打开Timing Analyzer或者在Tools菜单中打开

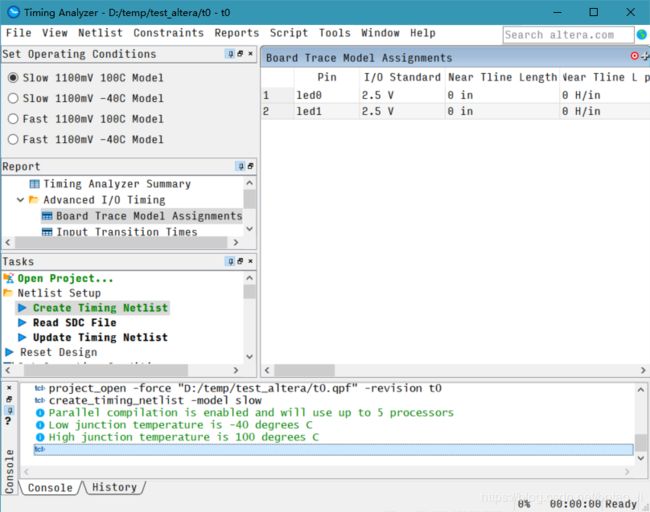

在Timing Analyzer的Tasks框内双击Create Timing Netlist,生成Timing网表

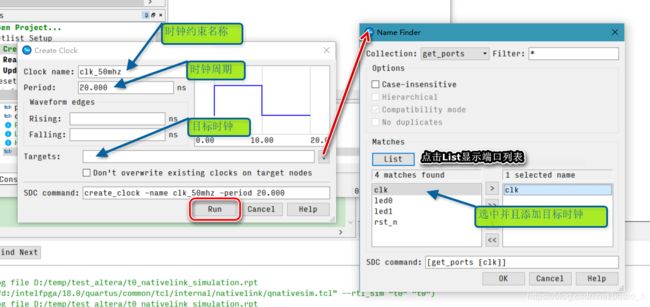

在Contraints菜单打开Create Clock对话框,添加时钟约束后点击Run按钮

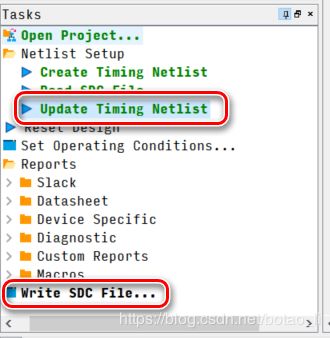

在Tasks框内双击Update Timing Netlist,更新Timing网表后双击Write SDC File,写入SDC文件

关闭Timing Analyzer后,回到Quartus界面

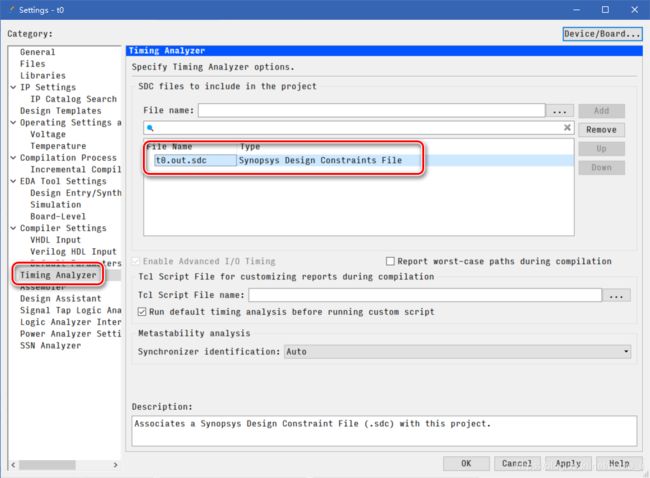

在Assignments菜单打开Settings对话框,进入Timing Analyzer页,添加刚才生成的SDC文件

之后需要对工程进行完全编译,包括综合

8. 编译

在Processing菜单选择Start Compilation,会完成Tasks框中Compile Design内所有未完成项。也可手动按顺序在Tasks框内逐项执行。

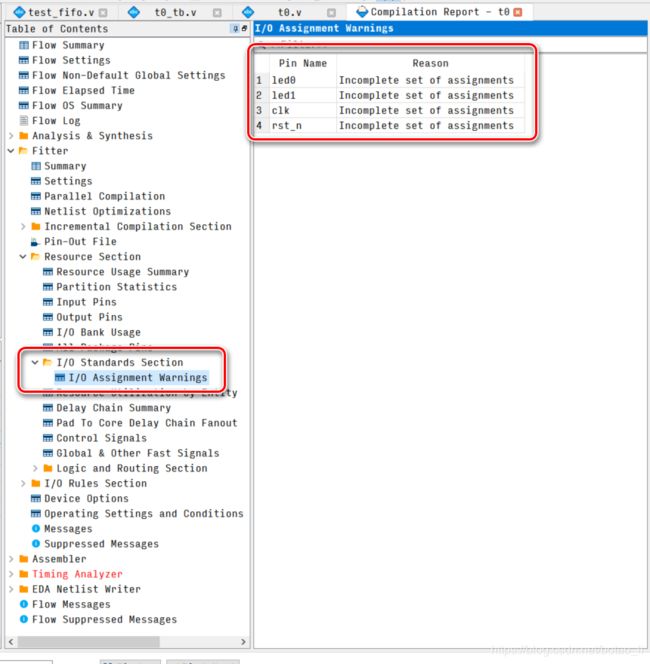

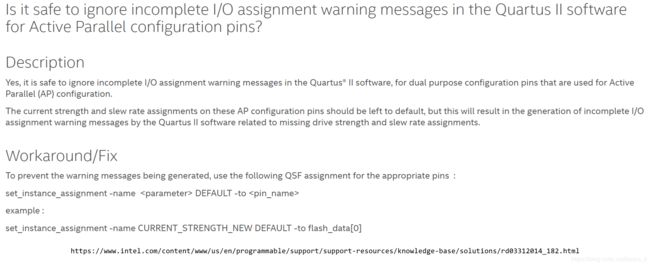

注意:在Fitter编译完成后会出现warning

根据官方解释,此warning可以忽略

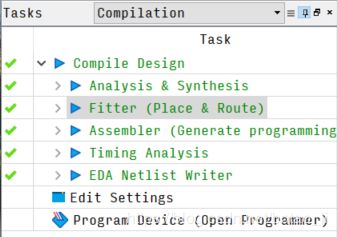

完成编译后,Tasks框显示如下

9. 下载

安装USB Blaster加载器

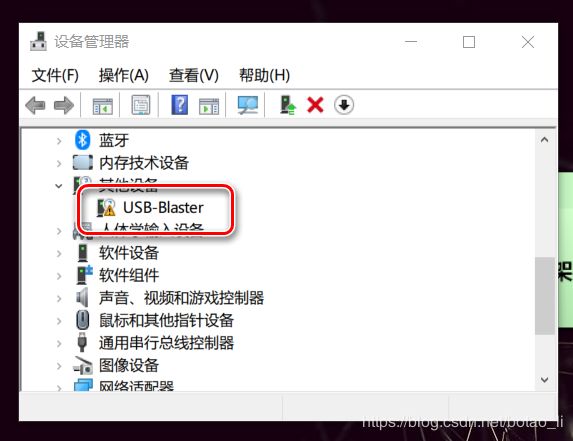

将USB Blaster加载器的USB端与主机USB口连接,打开Windows设备管理器找到USB-Blaster项,右键菜单选择更新驱动程

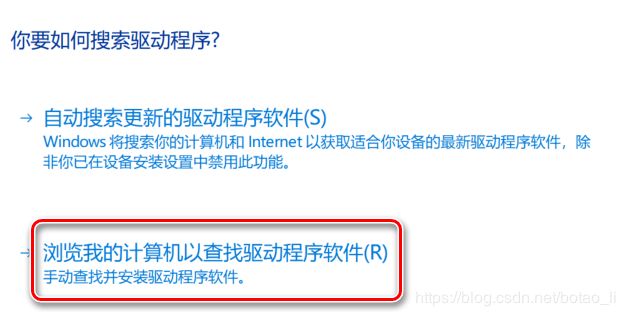

弹出更新驱动程序窗口中选择浏览我的计算机以查找驱动程序软件

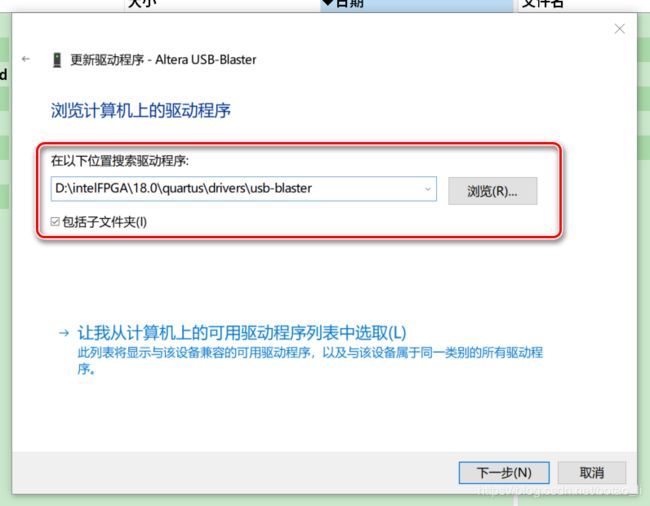

在Quartus安装目录下找到下图所示路径,并点击下一步

在弹出窗口中选择安装

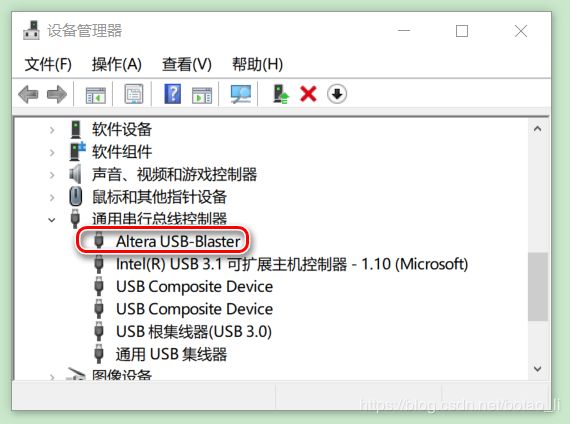

完成安装后在设备管理器中找到Altera USB-Blaster

烧写程序

在Quartus的Tools菜单选择打开Programmer

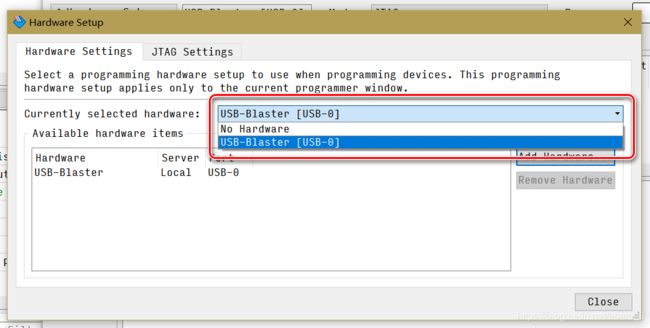

在Hardware Setup弹窗中的下拉列表选择USB-Blaster

由于Programmer的JTAG Chain是根据工程设置自动生成,与实际硬件连接可能不同,因此需要重新建立JTAG Chain

在Programmer窗口的Processing菜单中选择Auto Detect

选择FPGA型号

弹出窗口选择Yes

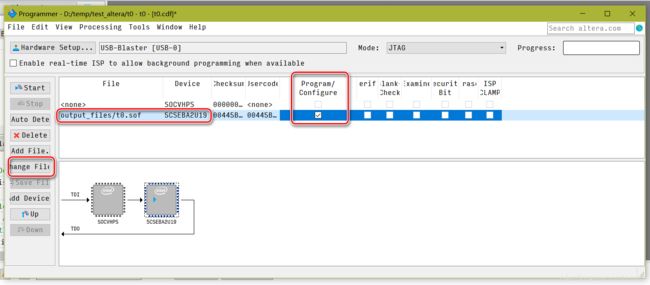

在Programmer窗口选择FPGA芯片,用右键菜单或者窗口左侧按钮选择Change File后,选择编译生成的sof文件,并勾选Program/Configure

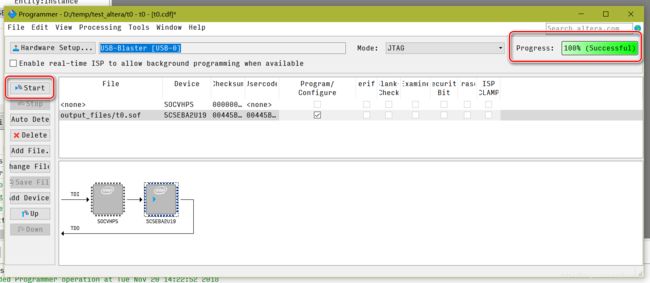

按下Start按钮完成烧写

10. 调试(Signal Tap)

Quartus的在线调试工具有许多,与Xilinx最相似的是Signal Tap Logic Analyzer

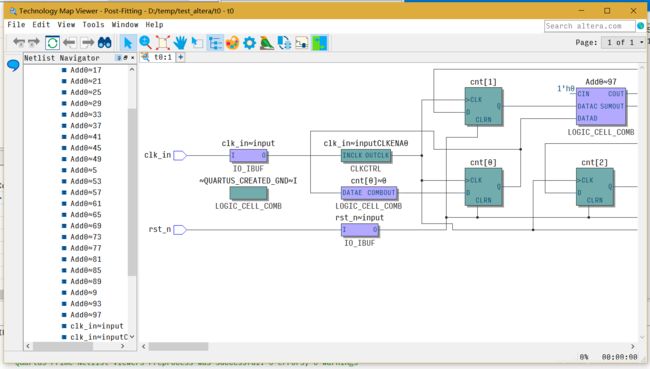

在开始调试之前最好确认网表内信号自动生成的名称,可以通过Tools菜单Netlist Viewer查看

同于是在线调试最好选择Post-Fitting

打开的网表如下所示

在Tools菜单选择Siganl Tap Logic Analyzer

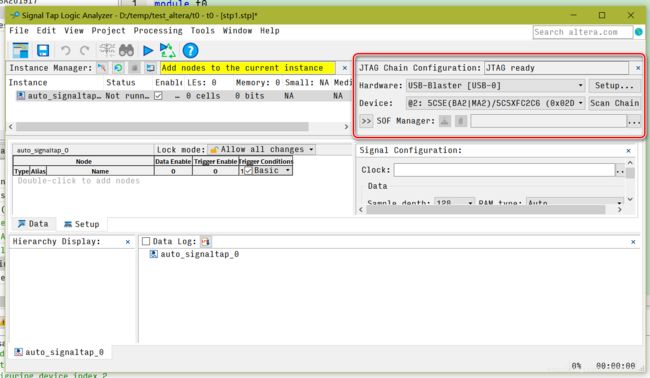

在Signal Tap窗口确认USB-Blaster和FPGA都已正常连接

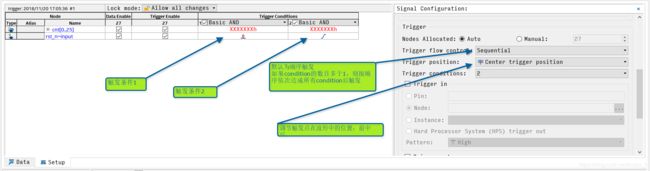

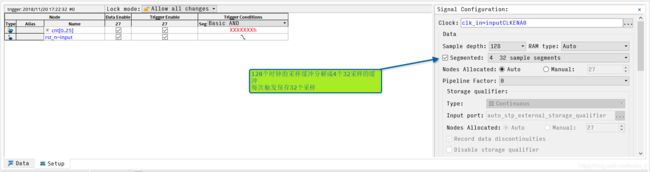

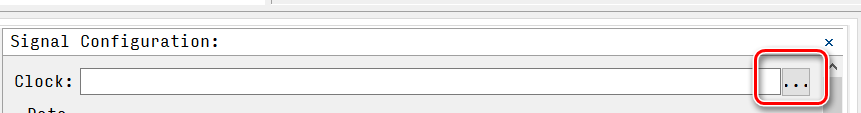

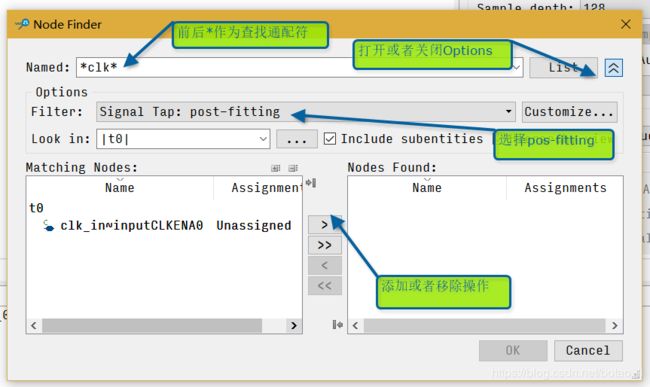

在Signal Configuration页添加时钟

选择采样深度

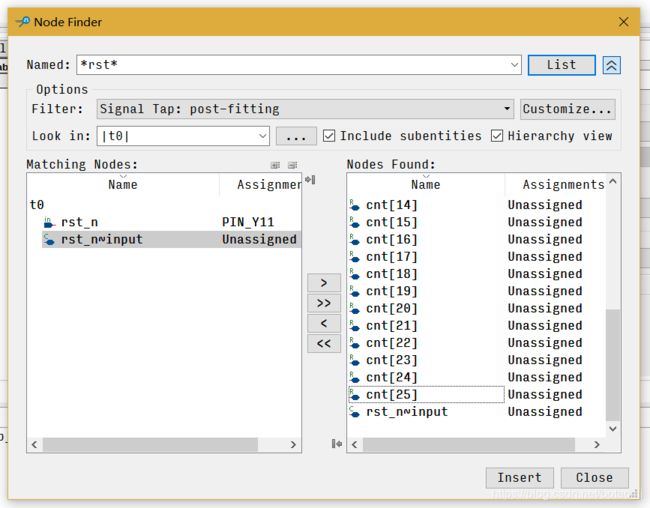

在Setup页根据提示双击弹出添加信号窗口

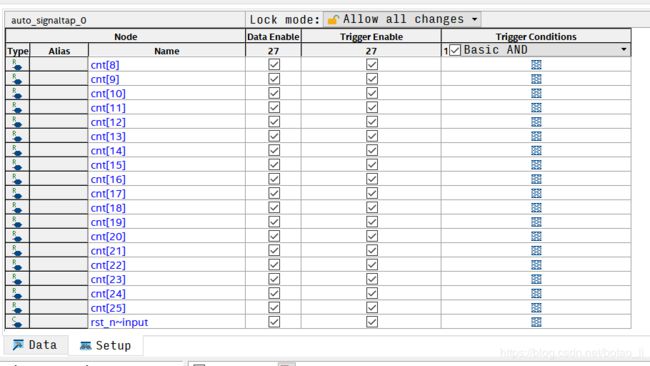

添加后的Setup可以根据需要选择信号是作为数据还是触发

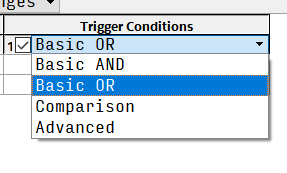

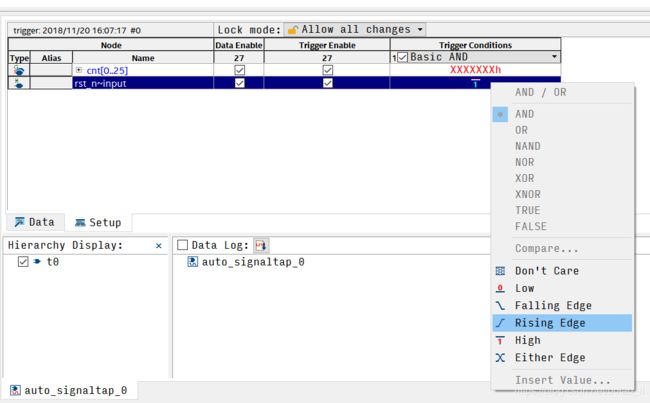

触发条件列表选择多个信号联合触发的方式==(如果在线调试过程中修改,需要重新编译)==

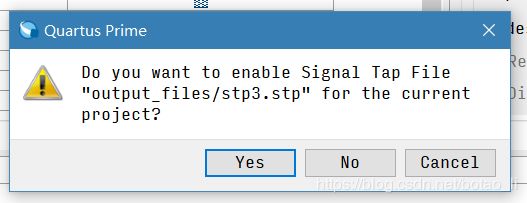

选择保存当前设置弹出确认窗口,选择Yes

重新编译工程

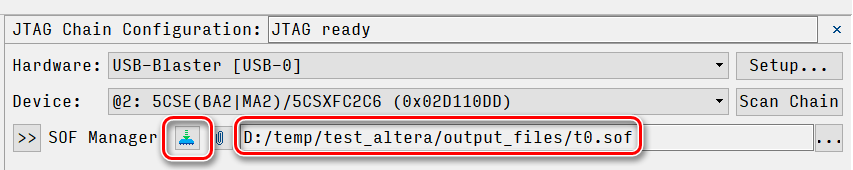

完成编译后,再次打开Signal Tap界面,在SOF Manager选择刚生成的sof文件,并点击下载按钮

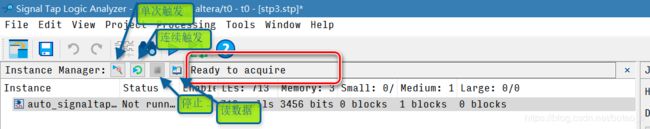

下载完成后显示Ready to acquire

启动触发后,在Data页可以查看数据波形

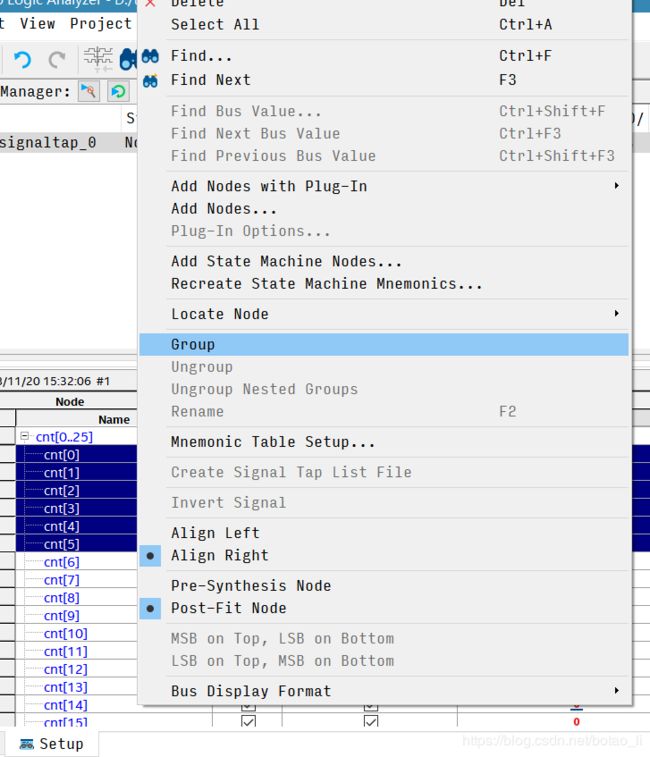

在Setup页可以选中多个信号后,右键建立group,可直接设置数值触发

并且用右键设置触发条件

注意,由于编译时设置的触发条件是Basic AND,因此各信号的触发条件之间是AND的逻辑