HMC833 测试板总结

ReadMe:

限制PLL性能的主要特性有相位噪声、杂散频率和锁定时间。

1、相位噪声:相当于时域中的抖动,相位噪声是振荡器或PLL噪声在频域中的表现。它是PLL中各器件所贡献噪声的均方根和。基于电荷泵的PLL可以抑制环路滤波器带宽内的VCO噪声。在环路带宽之外,VCO噪声占主导地位。

2、杂散:杂散频率由电荷泵定期更新VCO调谐电压而引起,并以与载波相差PFD频率的偏移频率出现。在小数N分频PLL中,小数分频器操作也会引起杂散。

3、锁定时间:从一个频率变为另一个频率或响应瞬时偏移时,PLL的相位或频率返回锁定范围所需的时间。它以频率或相位建立性能来确定,其作为特性的重要程度视应用而定。

自我的心得体会:

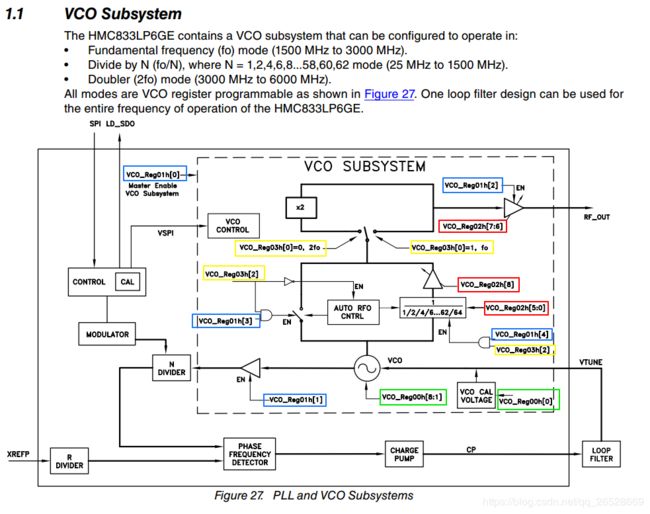

HMC833是带有小数N分频和PLL的综合VCO器件,输出频率可以实现25~6000M的任意频率输出。芯片的接口如下图所示,其SPI串行通信口可以实现50MHz的高速数据通信,同时SPI串行接口中的LD_SDO接口为复用引脚,可通过写寄存器0x0F来选用PLL锁定输出指示功能和SPI的SDO功能,因此更方便PCB布板和电路设计。

芯片的额参考时钟XTAL可选择频率为10~200MHz的方波,幅度为0.6~2.5VPP、频率为25~200MHz的正弦波,功率为3~15dBm,有较宽的频率输入范围。VCO输出频率计算公式为F_vco=F_xtal/R*(N_int+N_frac),期中VCO的输出频率为1500~3000M。高频输出频率为F_out=F_vco/K, 式中K为VCO输出的分频系数,当倍频功能开启时K=0.5=1/2.

软件设计时的寄存器操作:

1、芯片模式的选择,这里我们选用的是HMC mode,先给CS一个上升沿

2、在上电后250us,芯片会将VCO寄存器进行复位,若上电不到250us则需要软件复位Write_once(0x00,0x000000);然后释放复位Write_once(0x00,0x000020);

3、然后依次写入寄存器值

Write_once(0x01,0x000002);

Write_once(0x02,R);//xtal分频R [13:0] 1d-16383d

//05H REG [2:0] Chip-ID=0; [6:3]VCO REG_addr; [15:7]data

// Write_once(0x05,0x000000);VCO_06

Write_once(0x05,0x001628);//VCO_05

Write_once(0x05,0x0060A0);//VCO_04

Write_once(0x05,0x002898);//VCO_03 VCO输出倍频设置

Write_once(0x05,VCO_DIV_REG);//VCO_02 VCO输出分频设置 //[6:0]addr bit=0010000; [12:7]=OutPut_Div;[14:13]RF output buffer gain control;[15]Divider output stage gain control;

// Write_once(0x05,0x000008);//VCO_01

Write_once(0x05,0x000000);//VCO_00

//SD CFG REG;[1:0]seed=2;[3:2]order=2;[6:4]resaved;[7]FracMode=0,IntMode=1;

//[8]AutoSeed=1;[9]=1;[10]=0;[11]SD Enable,Int=0,Frac=1;[12:16]Resaved;[18]Built in self Test def=0;[20:19]RDiv BIST Cycles.

Write_once(0x06,0x030F4A);//选择整数或者分数模式

//[2:0]LD wincnt set=VCO/reg_set def=101;[3]Enable LD=1;[5:4]Resave;[6]LD win type=1;[9:7]LD win Duration cycle=1;

//[11:10]LD Digital Time Freq Control=0;[12]LD Timer Test Mode=0;[13]Auto Relock once=0;

// Write_once(0x07,0x00014D);

// Write_once(0x08,0xC1BEFF);

//[6:0]CP DN Gain 20uA/step;[13:7]CP UP Gain 20uA/step;[20:14]CP offset 5uA/step;[21]UP EN;[22]DN EN;[23]HikCP High Current CP.

Write_once(0x09,0x5CBFFF);//电荷泵 Current 2.54mA 偏置电流570uA

//

Write_once(0x0A,0x002046);//Autocal REG

Write_once(0x0B,0x07C061);//PD REG

// Write_once(0x0C,0x000000);

// Write_once(0x0D,0x000000);

Write_once(0x0F,0x000081);//pin LD_SDO引脚功能配置

// Write_once(0x10,0x000000);

// Write_once(0x11,0x000000);

// Write_once(0x12,0x000000);

// Write_once(0x13,0x000000);

Write_once(0x03,N_int);//设置N int [18:0] Frac Mode 20d-524284d Int Mode 16d-524287d

Write_once(0x04,N_frac); //设置N frac [23:0] 0d-16777215d

4、注意上述中文注释的寄存器,对要实现的输出频率进行相应的寄存器赋值计算:

VCO分频系数VCO_K设置: VCO_DIV_REG = (VCO_K<<7)|0x00E010;

VCO频率系数N的计算: N = RF*R*VCO_K*1.0/F_xtal;

N_int = (u32)N;

if (((N-N_int)*pow(2,24))-(u32)((N-N_int)*pow(2,24)) >= 0.5)

N_frac= (u32)((N-N_int)*pow(2,24))+1;

else

N_frac= (u32)((N-N_int)*pow(2,24));

R的预设

倍频的设置

5、电荷泵的设置,在Frac Mode推荐使用CP_DN,CP Current为reg*20uA,CP_offset为reg*5uA。

注意:CP_offset/CP应在25%以内,一般为20%左右。(这是有由于LD Window宽度为10ns,frac Mode中PD的时间抖动为~2.5ns+4Tvco造成的,此操作可能导致PLL无法锁定,或者杂散变多变大)

6、VCO输出增益的控制VCO_02 REG 设置为MaxGain

测试版的调试:

------条件:电源为5V供电,STM32F407为控制芯片,SPI为30M,xtal为40M。

在测试板的调试过程中,首先对测试板进行焊接检测,注意到xtal输入时需要外接一个100Ω的电阻和电路中的50Ω做匹配,所以在输入端的SM接头下面补上。然后对芯片进行写数据测试,主要测试数据有两组740M和2270M,740M的测试结果为输出幅度30dBm,且杂散较大,分别为1、2、3倍频,与740M幅度相差为-16dBc,但由于其频率相差加大,可以在后端接滤波器以做改善。2270M的测试结果为输出幅度25dBm,基本无杂散,频率稳定,通带干净。

分析:在740和2270MHz输出频率的测试之后,还对从 740~2000M依次20M频率步进做了测试,发现杂散的出现主要为当前输出频率的倍频,随着频率的升高,杂散间的频率间隔等比增大,在频率上到1800M时在频谱仪中以3GHZ的Span,观测时已无法观测。

在查找相关手册和相关资料后,定义为VCO调谐电压而引起,并以与载波相差PFD频率的偏移频率出现。在小数N分频PLL中,小数分频器操作也会引起的杂散。