Xilinx的ZYNQ芯片软件设计说明

1、概述

ZYNQ是xilinx推出一个款SOC,其亮点在于FPGA里包含了完整的ARM处理子系统(PS),每一颗Zynq系列的处理器都包含了Cortex-A9处理器,整个处理器的搭建都以处理器为中心,而且处理器子系统中集成了内存控制器和大量的外设,使Cortex-A9的核在Zynq-7000中完全独立于可编程逻辑单元,也就是说如果暂时没有用到可编程逻辑单元部分(PL),ARM处理器的子系统也可以独立工作,这与以前的FPGA有本质区别,其是以处理器为中心的。

Zynq就是两大功能块,PS 部分和PL部分,就是ARM的SOC部分,和FPGA部分。其中,PS集成了两个ARM Cortex™-A9处理器,AMBA®互连,内部存储器,外部存储器接口和外设。这些外设主要包括USB总线接口,以太网接口,SD/SDIO接口,I2C总线接口,CAN总线接口,UART接口,GPIO等。

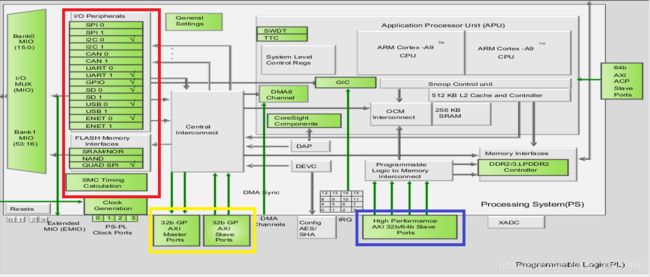

ZYNQ芯片总体框图

其中红色的PS本身自带的外设,黄色框是PS与PL通信接口(两个Master、两个Slaver),蓝色框是高性能PS与PL通信接口其只有Slaver接口,我们现主要用作DMA数据传输。

2、PS和PL互联技术

ZYNQ作为首款将高性能ARM Cortex-A9系列处理器与高性能FPGA在单芯片内紧密结合的产品,高效的PL和PS数据交互通路是ZYNQ芯片设计的重中之重。

用户在具体设计中往往不需要在连接这个地方做太多工作,我们加入IP核以后,系统会自动使用AXI接口将我们的IP核与处理器连接起来,我们只需要再做一点补充就可以了。

2.1AXI总线简介

AXI全称Advanced eXtensible Interface,是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,所以我们经常会看到AXI4.0,ZYNQ内部设备都有AXI接口。其实AXI就是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。

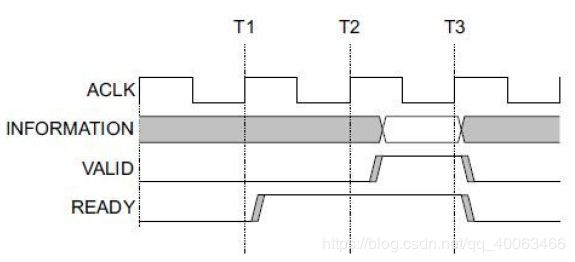

AXI协议主要描述了主设备和从设备之间的数据传输方式,主设备和从设备之间通过握手信号建立连接。当从设备准备好接收数据时,会发出READY信号。当主设备的数据准备好时,会发出和维持VALID信号,表示数据有效。数据只有在VALID和READY信号都有效的时候才开始传输。当这两个信号持续保持有效,主设备会继续传输下一个数据。主设备可以撤销VALID信号,或者从设备撤销READY信号终止传输。AXI的协议如图,T2时,从设备的READY信号有效,T3时主设备的VILID信号有效,数据传输开始。

2.2 AXI三种协议对比

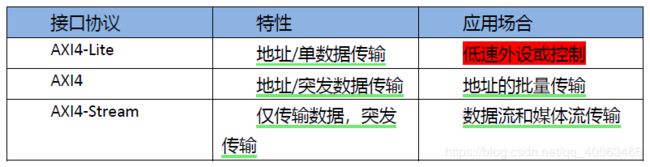

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,通过下表我们可以看到这三中AXI接口的特性。

AXI4-Lite:

具有轻量级,结构简单的特点,适合小批量数据、简单控制场合。不支持批量传输,读写时一次只能读写一个字(32bit)。主要用于访问一些低速外设和外设的控制。

AXI4:

接口和AXI-Lite差不多,只是增加了一项功能就是批量传输,可以连续对一片地址进行一次性读写。也就是说具有数据读写的burst功能。

上面两种均采用内存映射控制方式,即ARM将用户自定义IP编入某一地址进行访问,读写时就像在读写自己的片内RAM,编程也很方便,开发难度较低。代价就是资源占用过多,需要额外的读地址线、写地址线、读数据线、写数据线、写应答线这些信号线。

AXI4-Stream:

这是一种连续流接口,不需要地址线(很像FIFO,一直读或一直写就行)。对于这类IP,ARM不能通过上面的内存映射方式控制(FIFO根本没有地址的概念),必须有一个转换装置,例如AXI-DMA模块来实现内存映射到流式接口的转换。AXI-Stream适用的场合有很多:视频流处理;通信协议转换;数字信号处理;无线通信等。其本质都是针对数值流构建的数据通路,从信源(例如ARM内存、DMA、无线接收前端等)到信宿(例如HDMI显示器、高速AD音频输出,等)构建起连续的数据流。这种接口适合做实时信号处理。

AXI4和AXI4-Lite接口包含5个不同的通道:

●Read Address Channel

●Write Address Channel

●Read Data Channel

●Write Data Channel

●Write Response Channel

其中每个通道都是一个独立的AXI握手协议。下面两个图分别显示了读和写的模型:

AXI读数据通道

AXI写数据通道

2.3 ZYNQ PL与PS互联接口

在ZYNQ芯片内部用硬件实现了AXI总线协议,包括9个物理接口,分别为AXI-GP0~AXI-GP3,AXI-HP0~AXI-HP3,AXI-ACP接口。

AXI_ACP接口,是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

AXI_HP接口,是高性能/带宽的AXI3.0标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

AXI_GP接口,是通用的AXI接口,总共有四个,包括两个32位主设备接口和两个32位从设备接口。

另外这9个AXI接口性能也是不同的。GP接口是32位的低性能接口,理论带宽600MB/s,而HP和ACP接口为64位高性能接口,理论带宽1200MB/s。

PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相应的AXI协议。Xilinx在Vivado开发环境里提供现成IP如AXI-DMA,AXI-GPIO,AXI-Dataover, AXI-Stream都实现了相应的接口,使用时直接从Vivado的IP列表中添加即可实现相应的功能。

工程实现

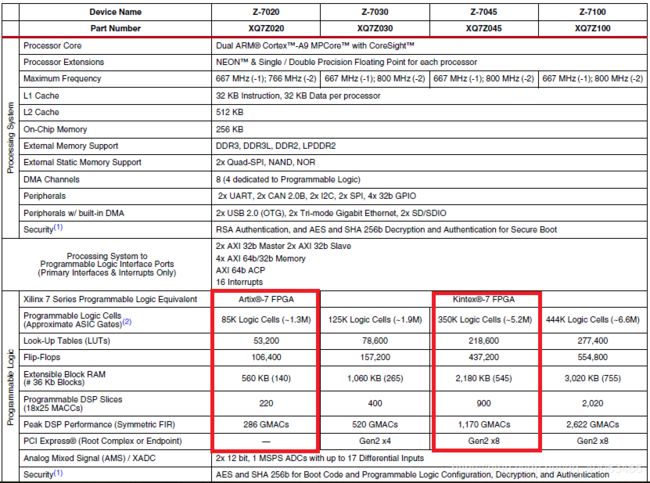

3.1 ZYNQ资源对比

最终我们开发所用的芯片为:ZYNQ7045,目前开发板所用的是:ZYNQ7020,其中各个ZYNQ的资源的对比如下图。

由上图可以看出,ZYNQ系列7020和7045的主要差别是在FPGA资料上,PS端的资源是一样的,因此在ZYNQ上PS的代码具有通用性。

3.2 代码实现

下图是工程整体实现框图,首先是初始化系统硬件,然后创建六个线程来实现各个模块的功能。

1、网络接收线程

目前网络接收线程没有特别多的工作做,主要是上位机命令的解析。

2、网络发送线程

此线程主要通过AXI_Lite总线以写寄存器的方式通知PL何时开始数据传输、传输数据的长度等,由于是和PL的自定义IP通信,因此需要自己写Linux的驱动。同时PL根据PS的命令通过DMA发送数据流到PS端,经过PS端将数据封装与打包,发到上位机。

3、串口发送

ZYNQ将射频组件状态、电机状态等雷达所必要状态信息通过PL端自定义IP将信息写到Bram中并通知PS去读取数据,并根据协议要求发送到上位机。

4、串口接收

串口接收主要接收上位机控制命令和参数,并解析如需要PS控制着直接控制,若需要通过FPGA与射频板通信或控制,则由PS将数据写入到Bram中并通过AXI_Lite总线通知PL自定义IP读取数据(PS端需要根据自定义IP写相应的驱动)。

5、Bram读写

在Vivado的Blockdesign中设计一个Bram模块,主要用于PS与PL之间小批量的数据交互,此线程主要是根据PL端的信号和上位机命令实现对Bram的读写。

6、系统指示灯

此线程目前无其他功能,仅仅作为系统运行指示作用,后续可根据需要添加功能。

3.3 工程框图

下图是Vivado中的工程框图,其中红色部分是实现Bram功能,黄色框内是实现PL-PS大量数据DMA交互的。