Verilog HDL——层次建模的概念

设计方法学

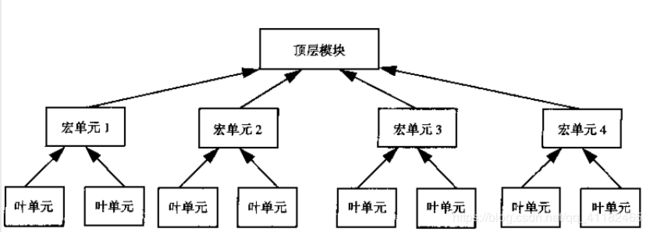

数字电路设计中有两种基本方法:自底向上和自顶向下。

自顶向下:

首先定义顶层功能块,进而分析需要哪些构成顶层模块的必要的自模块,然后对子模块进行分解,直到达到无法进一步分解的底层功能块。

自底向上:

首先对现有的功能块进行分析,然后使用这些模块来搭建一些规模较大的模块,如此继续直至顶层模块。

实际设计中,一般是两种方法结合起来更加方便也更加合理。

举例:

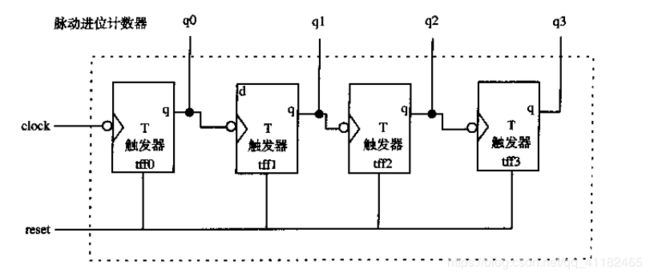

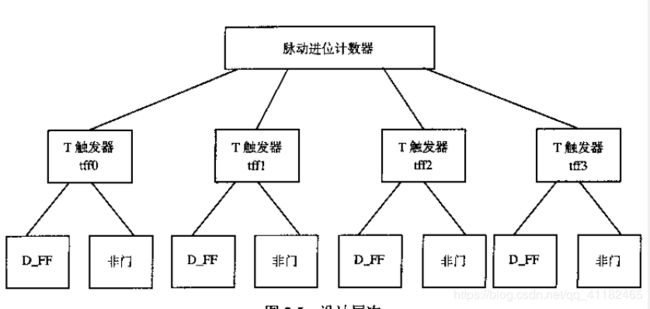

这是由四个T触发器构成的脉冲进位计数器。

而T触发器是可以有D触发器和非门构成的,那我们就可以为了构成这个脉冲计数器,先构成四个T触发器,又因为D触发器和非门可以构成T触发器,所以更低一层就可以考虑使用D触发器加非门。

实际上D触发器还可以接着由门电路构成,接着分解,不过并不是分的层次越细越好,因为D触发器已经是很基础的元器件了。

模块

Verilog 是 一门类C语言,与VHDL不同,如果学过C语言的话就比较容易理解语法的含义。

Verilog 使用模块的概念来代表一个基本的功能块,模块中可以是其他模块的实例化,也可以是单独的一个原件。模块通过接口被调用,而具体的细节调用时并不需要考虑。

上面的例子中,就可以将D触发器设计为一个模块,T触发器模块实例化D触发器模块,同时用语句实现非门这样一个结构,最后再组合为一个T触发器,而脉冲计数器模块就可以实例化四个T触发器。

模块的语法形式:

module <模块名>(<模块端口列表>);

<具体实现>

endmodule

例如:

module T_FF(q, clock, reste);

…

//注释:这是一个T触发器

end module

模块声明中不允许嵌套声明。

四个抽象层次

模块内部可以在四个抽象层次中进行描述,而对外显示功能都是一样的。

1.行为或算法级:

Verilog所支持的最高抽象级别,设计者只需要注重算法而不关心具体的硬件实现。

2.数据流级:

通过说明数据的流程对模块进行描述,设计者关心的是数据如何在各个寄存器之间流动和如何处理。

3.门级:

从组成电路的逻辑门及其相互之间 的互联关系来描述设计模块。

4开关级:

最低抽象级别,通过使用开关,存储节点及其互连关系来设计。需要了解开关级别的具体实现细节。

抽象层次越高,设计的灵活性和工艺无关性就会越强;随着抽象级别的降低,对底层了解的就越清楚,微小的调整可能会导致对设计的多出修改。

模块实例

就我个人来言,感觉就像是C语言里结构体。而实例化就像是变量声明,模块声明只是解释模块如何如何工作,其内部结构和外部结构的

调用必须对其实例化完成。

例子——对脉冲计数器的实现:

//这里先不考虑具体的语法

//D触发器

module D_FF(q,d,clk,reset);

output q;

input d,clk,reset;

reg 1;

always @(posedge reset or negedge clk)

if(reset)

q<=1’b0;

else

q<=d;

endmodule;

//T触发器

module T_FF(q,clk,reset);

output q;

input clk,reset;

wire d;

D_FF dff0(q,d,clk,reset);

not n1(d,q);

endmodule

//脉冲计数器

module ripper_carry_counter(q,clk,reset);

output [3:0] q;

input clk,reset;

T_FF tffo(q[0],clk,reset);

T_FF tffo(q[0],clk,reset);

T_FF tffo(q[0],clk,reset);

T_FF tffo(q[0],clk,reset);

endmodule

激励块

一般设计的模块称为设计块,而用来仿真调测的称为激励块,也称为测试台。

激励块的设计有两种模式:

1.在激励块中调用并直接驱动设计块:

2.在一个虚拟的顶层模块中调用激励块和设计块:

例子——对计数器的检查

//激励块

module stimulus;

reg clk;

reg reset;

wire[3:0] q;

//实例化计数器

ripple_carry_counter r1(q,clk,reset);

//设计测试的时钟信号

initial

clk = 1’b0;

always

#5 clk=~clk;

//控制驱动设计块的Reset信号

Initial

begin

reset = 1’b1;

#15 reset=1’b0;

#180 reset=1‘b0;

#10 reset=1’b0;

#20 $finish;

end

initial

m o n i t o r ( monitor( monitor(time,“Out put q= %d”, q);

endmodule

之后就可以进行仿真测试设块的正确性。