计算机组成原理课程设计_微程序控制的简单模型机设计

文章目录

- 微程序控制的简单模型机设计

- 要求

- 基本要求

- 弹性要求

- 实验软件和硬件环境

- 实验原理和方法

- 实验步骤

- 拟定指令系统

- 确定总体结构

- 逻辑设计

- 控制方式

- 编制指令流程

- 编制微程序

- 调试

- 单元测试部分

- 整机测试

- 测试程序编写

- 测试方式

- 问题分析

- 实验感悟

- 项目位置

微程序控制的简单模型机设计

要求

基本要求

完成一个简单主机的设计,模型机应具备如下能力:在自行设计的指令集基础上,运行自行编写的简单用户程序,实现特定运算功能。

弹性要求

在此基础上,完成必要的扩展,实现模型机的功能扩展设计,包括:实现多种运算功能(指令集的扩充)、支持更为丰富的寻址方式、有更为完善的微程序设计等。

实验软件和硬件环境

QuartusII, FPGA计算机组成实验箱

winxp系统,内存8G,CPU i7-5500U

实验原理和方法

利用所学过的理论知识,写出要设计的指令系统的微程序。随后确认总体结构,进行逻辑设计,再确定控制方式,编制指令流程,最后将所设计的微程序写入计算机组成原理教学实验系统环境中进行测试,

在设计的过程中,我们首先要确定所设计计算机的功能和用途,设计中根据功能和用途确定指令系统,数据的表示格式,位数,指令的编码,类型,需要设计那些指令和寻址方式。确定相对应指令所包含的微操作以及总体结构设计之间的数据通路结构,在此基础上,就可以拟出各种信息传输路径,以及实现这些传输所需要的微指令。

实验步骤

拟定指令系统

基本字长:

模型机基本字长定位8位,存储容量为256*8位,

指令类型:

指令类型有三种:无操作数指令、单操作数指令和双操作数指令。操作码OP共四位,最多可以定义16条指令。

指令格式:

指令格式有单字长指令、双字长指令(16位)和三字长指令(24位,仅用于乘法)三种;

在双字长指令和三字长指令中中,第二字节和第三字节被定义为操作数或操作数地址

寻址方式:

采用了立即数寻址、直接寻址两种寻址方式。

10:是立即数寻址,操作数在指令的下一个单元;

20:是直接寻址,操作数地址在指令的下一个单元。

基本指令集:

LOAD 取指指令

LOAD A 立即数寻址

LOAD A# 直接寻址

MOVE AC,R1 转移指令(AC->R1)

MOVE R1,AC 转移指令(R1->AC)

STORE 存数指令(AC->RAM立即数)

STORE 存数指令(AC->RAM直接寻址)

ADD AC,R1 加法指令(AC+Y->AC)

ADD AC,A 加法指令(立即数寻址+AC->AC)

ADD AC,A# 加法指令(直接寻址+AC->AC)

MUTI AC,R1 乘法指令(ACR1->AC/R1)

MUTI AC,R1 STORE 乘法指令(ACR1->RAM立即数)

MUTI AC,R1 STORE 乘法指令(AC*R1->RAM直接寻址)

HALT 停机指令

确定总体结构

寄存器设置:

AC、Z为带有三态门的移位寄存器,8位

MDR,R1为带有三态门的通用寄存器,8位

Y为寄存器,8位

IR为带有三态门的指令寄存器,8位。

uPC,PC程序计数器,8位。

MAR为地址寄存器,8位。

运算器ALU的设置:

ALU仅提供加法运算,采用两个74181芯片和一个74182芯片制成,并附带一个8位移位器,用于实现乘法。

数据通路:

模型机的数据通路是以总线为基础,以CPU为核心构成的。

基本指令流程举例:

(添加控制信号和流程)

送指令地址:

取指令:

程序计数器加1:

R0 → R1 :

R1 → RAM :

逻辑设计

ALU的逻辑设计:

由两片74181和一片74182组成。

触发功能:

寄存器的设计

Z和AC为八位带三态门的移位寄存器,每个寄存器由8个D触发器组成,每个输入通过三个二位与门和一个三位或门组成选择器,并在每个输出端接三态门。

触发功能:略

而带三态门的通用寄存器为将移位寄存器中的移位触发管脚接低电平直接封装而成。

AC为累加寄存器,可存放操作数或结果、中间结果

Y为加寄存器,用于参与ALU运算。

Z为部分积寄存器,用于存放ALU得到的结果

MDR为数据寄存器,用于存放从RAM取得的操作数或地址。

MAR为地址寄存器,用于存放指向某个数据的地址。

IR为指令寄存器,用于存放微程序的基地址。

程序计数器:

也是一个带复位和Load信号的八位寄存器,PC加1是通过加法器实现的。复位信号RET 的作用是有复位信号时,计数器PC清零。

部件之间的连接:

由系统结构图可看出,部件之间的连接是为单总线连接方式。除Z以外所有寄存器都能通过总线输入,除Y的输出连接ALU,地址寄存器MAR的输出连接RAM地址管脚,其余输出都与总线相连。

控制方式

控制方式采用微程序控制器时序

P脉冲的低电平用做控制存储器读命令μRD

P脉冲的上升边沿将读出的微指令送 μIR

微指令格式:

微指令字长24位即 μIR23~ μIR0。

微指令字段定义:

-

uIR23-uIR17:分别对应AC,IR,MAR,MDR,R1,Y,Z的触发

1:触发对应寄存器

0:不触发 -

uIR16-uIR11:分别对应AC,IR,MDR,PC,R1,Z的三态输出的使能端

1:允许对应寄存器输出

0:不允许输出

(一次指令输出仅有一个可置1) -

uIR10,uIR9:ALU的a输入与b输入的与门端,只有相应字段为高电平才会输入正

确字段,否则输入为全0。

00:00000000+00000000->ALU

01:00000000+bus->ALU

10:Y+00000000->ALU

11:Y+bus->ALU -

uIR8:标志乘法的指令字段,通过该字段控制移位和补位

-

uIR7-uIR5:uPC控制的指令字段,用来控制微程序执行的位置

100:uPC+1->uPC

010:0->uPC

001:bus->uPC -

uIR4:PC+1

-

uIR3-uIR2:RAM读写控制(10读,01写)

-

uIR1:停机指令

-

uIR0:乘法最后一步标志位

微命令形成逻辑:

略

后继微地址产生逻辑:

使用了三种后继微地址生成方式:

增量方式、无条件转移方式、按操作码转移方式

当upc_add=1时,微程序计数 μPC执行加1操作。

当uPC_clr=1时,微程序计数器uPC清零,仅执行完一条非取指指令需要重新进入取指周期的时候使用。

当uPC_Load=1时,按IR指令寄存器的地址的高四位(低四位为0)转移。

编制指令流程

| 微程序名称 | 入口地址 |

|---|---|

| LOAD0 | 00H |

| LOAD1 | 10H |

| LOAD2 | 20H |

| MOVE0 | 30H |

| MOVE1 | 40H |

| STORE | 50H |

| STORE | 60H |

| ADD | 70H |

| MUTI | 80H |

| MUTI | 90H |

| HALT | B0H |

编制微程序

根据指令流程和微指令格式就可以编制微程序。

指令流程中每行对应一条微指令,结合总体结构框图,写出这个流程所对应的数据通路的控制命令。

所需的控制命令在表中的相应位置填写上“1”,不需要的命令填写“0”。

另外每一条微指令都要确定下条微指令地址的生成方式。

写出取指令、每条指令对应的微代码,并用16进制数表示。

调试

单元测试部分

ALU测试:

an,bn,in_a,in_b,m,s0-s3,cn各自分配开关

f1-f7,f8(即进位)连接灯泡

通过控制开关查看灯泡的方式验证alu的加法包括进位没有问题。

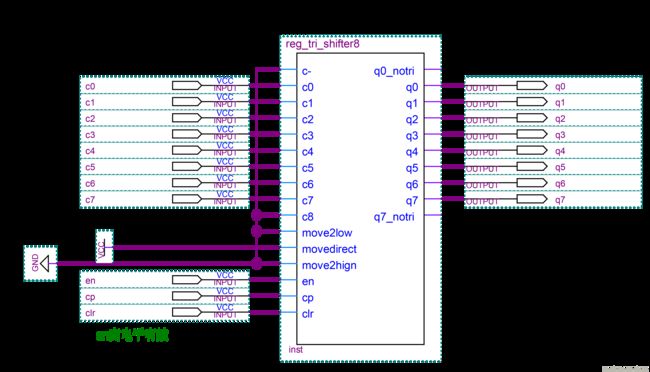

移位寄存器测试:

测试1:

c-(右移补位),c8(左移补位),c0-c7,move2low,movedirect,move2high,en各自分配开关

cp接单脉冲

clr接清零脉冲

通过改变开关,使用单脉冲来测试左移右移,置数和使能端是否有效,以及有效时候的电平是否为高电平。

测试2:

将两个移位寄存器以一个寄存器的低位接到另一个寄存器的右移的补位的方式,其他分配方式同测试1,进行16位扩展寄存器的测试,用来验证一次脉冲能否实现移位和正常的补位以及。

整机测试

测试程序编写

1.实现存取

Load1

Move1

Move2

Store

Halt

2.实现加法和结果的存放

Load1

move

Load1

Add

Store

Halt

3.实现乘法和结果的存放(两位)

Load1

Move

Load1

MUTI

Store

测试方式

①微程序经过检查无误后通过“计算机组成原理与系统结构安装软件”以十六进制写入3# ROM2# ROM和1# ROM的相应单元中去。

②按复位键RET使MAR清0、指令计数器PC清0,保证从存储器0号单元取指令。使微程序计数器UPC清0,保证从3# RAM、2# ROM、1# ROM的0# 单元取出取指令微程序的第一条微指令。

③按一次脉冲键产生一负脉冲(作为 μRD ),将ROM1# 、ROM2# 0号单元的16位微指令代码读出,用上升沿将微指令送入µIR15-0。

④在电路图CP端接上连续脉冲,去掉所有路线上的灯,点击实验平台上的脉冲按钮后,程序自动执行到停机指令结束。观察F0-F5的数值是否正确。

问题分析

-

对整机的测试问题

为了确保不犯低级错误,以及不因为一些疏忽导致错误,我对每一个部件都做了相应的测试,通过连接开关和灯,对ALU,程序计数器,启动器,移位寄存器,以及移位寄存器的补位都做了相应的测试。并在整机中分批次连接了大量的灯泡用来判断当时的状态,这样就保证不会因为一些低级错误没有发现而浪费大量的调试时间。 -

连续脉冲下不能正常工作

测试和调试的过程中,我在很多地方都加了灯,以灯的变化来看数据通路里的数据内容,在单步执行的时候没有问题,但是当处于连续脉冲状态下就会产生影响。把灯的连接线断开后即可解决这个问题,猜测这可能是与脉冲的频率,机器的运算速度等相关。 -

对于指令的简化:

由于对本次实验而言,ALU只用到了加法功能,因此对其m,s0-s3直接连接高低电平,以及Cn端接高电平,这样就节省了6个管脚,从而不需要译码器就可以完成对机器的控制。 -

cp脉冲的分配问题:

因为uIR和CPuRD是下降沿有效,而各个CP为上升沿有效,而单脉冲为负脉冲,因此在各个cp脉冲门之前都要加一个非门,才能确保指令的正确执行。 -

乘法的实现:

乘法的实现原理是原码一位乘,其中1位是符号位,7位是数值位,在乘法的时候通过acc_ml表示乘法,应该在加的过程同时左移,将结果存入Z(高8位)和AC(低8位),一共左移8次,其中数值位相加(需要判断乘数末位)7次,最后一次通过异或门来实现符号位相乘,并置入Z的最高位。这样就实现了8步乘法。 -

各运算指令的实现:

各运算指令由IR的高四位形成(RAM → IR),RAM中的数据高四位写入的是各个运算指令和操作指令。

实验感悟

略

项目位置

Quartus工程