反向器是一个简单的器件,用一个继电器就可以实现。当我们把反向器的输出连接到输入时,会发生什么呢?

当输入为0时,输出为1;输出连接到输入上,此时输入又变成1,输出值变成0;如此反复。需要特别指出的是,反向器实际上是一个继电器,而继电器从一个状态转换到另一个状态是需要时间的。所以,即使输入和输出是相等的,输出也会很快地改变,成为输入的倒置(当然,随即输出也就改变了输入,如此反复)。

这种电路称为振荡器(oscillator)。

振荡器又常被称为时钟,因为它的输出在0、1之间按固有的规律交替变化。

振荡器从一个初始状态经过一段时间又回到这个状态;这个时间间隔定义为振荡器的一个循环,又叫周期。如下图所示

周期的倒数就是频率,也就是每秒钟振荡器产生循环的次数。

第一个图所示的连接方式叫做反馈,系统的输出反馈给输入。

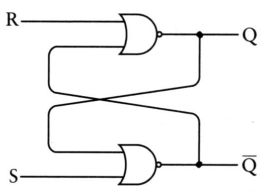

下面看一个电路图

上图由两个或非门组成。实际上这就是一个R-S触发器。其真值表如下所示

S是置位,R是复位。当R为1时,Q为0,Q非为1;当S为1时,Q非为0,Q为1;当两者都为0时,输出状态保持不变。两者同时为1的情况是不允许存在的,一定要避免这种情况。

R-S触发器的好处是可以记忆电路:Q的状态反映了输入端的状态。例如此时S和R均为0,、Q为1,那我们就知道S之前为1,R为0。

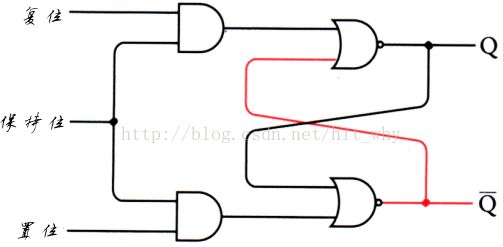

但有时我们需要记忆功能更强大的电路,于是有了下面的电路。

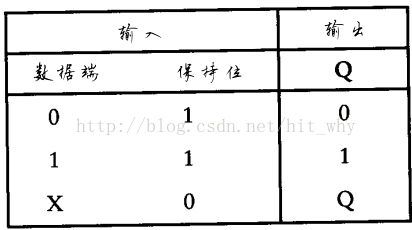

其真值表为

当保持位为1时,它实际上就是一个R-S触发器;当保持位为0时,置位和复位段数值无论是什么,对输出都没有影响。我们就可以控制输出的记忆时间等。但我们需要两个输入,现在有三个。首先我们知道R-S触发器两个输入端不能同时为1;而且两个输入端同时为0,也没有意义,因为保持位为0已经包含这种情况。因此将电路图改为以下形式

当保持位为1时,Q反映了数据端的数值,数据端就相当于置位。当保持位为0时,输入端对输出端没有任何影响。此时R-S触发器处于记忆状态。

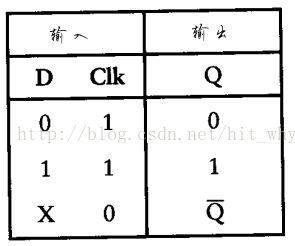

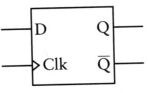

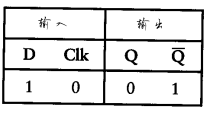

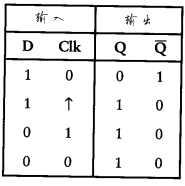

这个电路又叫电平触发的D型触发器,电平触发是指当数据端电平为1或者为0时就会影响输出。D代表输入端(数据端),其真值表如下

这个电路也叫D锁存器,实际上就是1位存储器,多个1位存储器可以构成多位存储器。

由以上内容可知,每个锁存器包括两个或非门、两个与门和一个反向器。

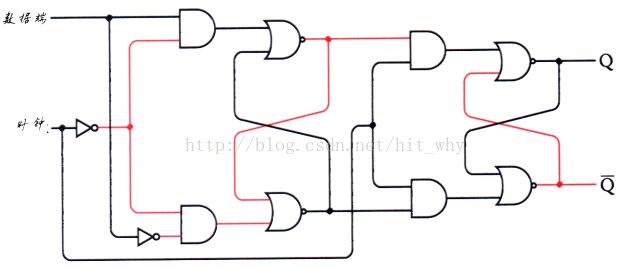

对某些应用而言,上面的电平触发器就够用了,但对另外一些来说,边沿触发器则更有效。对于边沿触发器,只有当电平从0->1或者从1->0时数据才会改变。边沿触发器可以由两级R-S触发器连接而成,如下所示

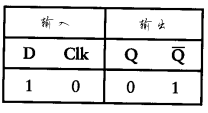

上面的电路在上升沿触发,下面分析一下。这里时钟同时控制着第一级和第二级R-S触发器。进一步分析,假设初始状态数据和时钟均为0,Q也为0。现在数据端变为1,此时第一级触发器的输出变为0,但是由于时钟为0,此时第一级触发器的输出对第二级触发器没有影响。然后,时钟从0变为1。在时钟从0->1的瞬间,第一级的输入对第二级的输出产生影响,使Q的值变为1;也就是上升沿触发。此时时钟为1,数据端的改变对第一级也不会有影响。边沿D触发器的真值表如下所示

符号为,其中小三角表示边沿触发。

回到本文开始的振荡器,现在将振荡器和上面的边沿D触发器连在一起

反馈接着反馈。假设初始状态时钟为0,Q也为0,Q非为1。当时钟从0变为1,Q输出与D相同,也就是Q非,值为1,Q非变为0,也就是D此时也变为0,此时时钟为1。

当时钟从1变为0时,由于是上升沿触发,此时对输出没有影响,时钟变为0。现在时钟再次从0变为1,由于此时D为0,所以Q变为0,Q非变为1,D变为1。如此反复。过程如下图

整个过程用下图也可以说明

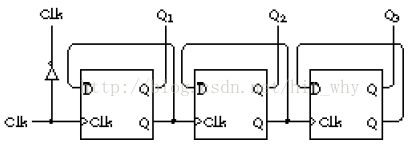

这种电路称为分频器,可以看出输出Q的频率是时钟的一半。我们现在将三个这样的分频器连在一起

然后在输出的信号上标上0和1,

将上图顺时针旋转90度,然后把每一行0和1连起来,就会发现,他们分别对应了0000-1111这16个二进制数。将输出Q1、Q2和Q3逆序连起来就组成了一个三位计数器。在时钟的每个上升沿这个计数器就会加1。

将8个这样的边沿D触发器连在一起就组成一个8位的计数器。称为“8位行波计数器”。这样我们就拥有了一个8位计数器。