一、摘要

DE2_TV中,有关于寄存器的配置的部分,采用的方法是通过IIC的功能,这里对IIC总线的FPGA实现做个说明。

二、实验平台

软件平台:ModelSim-Altera 6.4a (Quartus II 9.0)

硬件平台:DIY_DE2

三、实验原理

1、IIC总线器件工作原理

在IIC总线上传送信息时的时钟同步信号是由挂接在SCL时钟线上的所有器件的逻辑“与”完成的。SCL线上由高电平到低电平的跳变将影响到这些器件,一旦某个器件的时钟信号变为低电平,将使SCL线上所有器件开始并保护低电平期。此时,低电平周期短的器件的时钟由低至高的跳变并不影响SCL线的状态,这些器件将进入高电平等待的状态。

当所有器件的时钟信号都变为高电平时,低电平期结束,SCL线被释放返回高电平,即所有的器件都同时开始它们的高电平期。其后,第一个结束高电平期的器件又将SCL线拉成低电平。这样就在SCL线上产生一个同步时钟。可见,时钟低电平时间由时钟低电平期最长的器件决定,而时钟高电平时间由时钟高电平期最短的器件决定。

IIC总线上数据的传输速率在标准模式下可达100kbit/s 在快速模式下可达400kbit/s 在高速模式下可达3.4Mbit/s ,连接到总线的接口数量只由总线电容是400pF 的限制决定。

2、IIC总线的传输协议与数据传送时序

(1)起始和停止条件

在数据传送过程中,必须确认数据传送的开始和结束。在IIC总线技术规范中,开始和结束信号(也称启动和停止信号)的定义如图1所示。

图1起始和停止信号图

开始信号:当时钟总线SCL为高电平时,数据线SDA由高电平向低电平跳变,开始传送数据。

结束信号:当SCL线为高电平时,SDA线从低电平向高电平跳变,结束传送数据。

开始和结束信号都是由主器件产生。在开始信号以后,总线即被认为处于忙状态,其它器件不能再产生开始信号。主器件在结束信号以后退出主器件角色,经过一段时间过,总线被认为是空闲的。

(2)数据格式

IIC总线数据传送采用时钟脉冲逐位串行传送方式,在SCL的低电平期间,SDA线上高、低电平能变化,在高电平期间,SDA上数据必须保护稳定,以便接收器采样接收,时序如图2所示。

图2 数据传送时序图

IIC总线发送器送到SDA线上的每个字节必须为8位长,传送时高位在前,低位在后。与之对应,主器件在SCL线上产生8个脉冲;第9个脉冲低电平期间,发送器释放SDA线,接收器把SDA线拉低,以给出一个接收确认位;第9个脉冲高电平期间,发送器收到这个确认位然后开始下一字节的传送,下一个字节的第一个脉冲低电平期间接收器释放SDA。每个字节需要9个脉冲,每次传送的字节数是不受限制的。

IIC总线的数据传送格式是在IIC总线开始信号后,送出的第一字节数据是用来选择从器件地址的,其中前7位为地址码,第8位为方向位(R/W)。方向位为“0”表示发送,即主器件把信息写到所选择的从器件中;方向位为“1”表示主器件将从从器件读信息。格式如下:

| 1 |

0 |

1 |

0 |

A2 |

A1 |

A0 |

R/W |

开始信号后,系统中的各个器件将自己的地址和主器件送到总线上的地址进行比较,如果与主器件发送到总线上的地址一致,则该器件即被主器件寻址的器件,其接收信息还是发送信息则由第8位(R/W)决定。发送完第一个字节后再开始发数据信号。

(3)响应

数据传输必须带响应。相关的响应时钟脉冲由主机产生,当主器件发送完一字节的数据后,接着发出对应于SCL线上的一个时钟(ACK)认可位,此时钟内主器件释放SDA线,一字节传送结束,而从器件的响应信号将SDA线拉成低电平,使SDA在该时钟的高电平期间为稳定的低电平。从器件的响应信号结束后,SDA线返回高电平,进入下一个传送周期。

通常被寻址的接收器在接收到的每个字节后必须产生一个响应。当从机不能响应从机地址时,从机必须使数据线保持高电平,主机然后产生一个停止条件终止传输或者产生重复起始条件开始新的传输。如果从机接收器响应了从机地址但是在传输了一段时间后不能接收更多数据字节,主机必须再一次终止传输。这个情况用从机在第一个字节后没有产生响应来表示。从机使数据线保持高电平主机产生一个停止或重复起始条件。完整的数据传送过程如图3所示。

图3 完整的数据传送过程

另外,IIC总线还具有广播呼叫地址用于寻址总线上所有器件的功能。若一个器件不需要广播呼叫寻址中所提供的任何数据,则可以忽咯该地址不作响应。如果该器件需要广播呼叫寻址中按需提供的数据,则应对地址作出响应,其表现为一个接收器。

四、实验过程

根据上述的实验原理,对DE2_TV中的IIC部分进行modelsim仿真。

1、IIC所需时钟的仿真

FPGA作为IIC器件的主机,要产生IIC的工作时钟,下面先对IIC所需的时钟信号进行仿真。

待仿真的时钟信号程序如下:

module I2C_Clock ( iCLK, iRST_N, mI2C_CTRL_CLK, mI2C_CLK_DIV, mI2C_CLKO ); input iCLK; input iRST_N; output mI2C_CTRL_CLK; output mI2C_CLK_DIV; output mI2C_CLKO; reg mI2C_CTRL_CLK; reg [15:0] mI2C_CLK_DIV; reg mI2C_CLKO; // Clock Setting parameter CLK_Freq = 50000000; //??? 50 MHz parameter I2C_Freq = 80000; //??? 40 KHz 25Us parameter I2C_Thd = 200000; //??? 5Us 200 KHz always@(posedge iCLK or negedge iRST_N) begin // 5000 times divide frequence of iCLK if (!iRST_N) begin mI2C_CLK_DIV <= 0; mI2C_CLKO <= 0; mI2C_CTRL_CLK <= 0; end else if( mI2C_CLK_DIV < (CLK_Freq/I2C_Freq)) begin mI2C_CLK_DIV <= mI2C_CLK_DIV+1; if ((!mI2C_CTRL_CLK)&(mI2C_CLK_DIV < ((CLK_Freq/I2C_Freq)- (CLK_Freq/I2C_Thd))) ) mI2C_CLKO <= 0; else mI2C_CLKO <= 1; end else begin mI2C_CLK_DIV <= 0; mI2C_CTRL_CLK <= ~mI2C_CTRL_CLK; end end endmodule

testbench程序如下:

module I2C_Clock_tb ; //parameter I2C_Thd = 200000 ; //parameter I2C_Freq = 80000 ; //parameter CLK_Freq = 50000000 ; wire mI2C_CTRL_CLK ; wire [15:0] mI2C_CLK_DIV ; wire mI2C_CLKO ; reg iRST_N ; reg iCLK ; I2C_Clock //#( I2C_Thd , I2C_Freq , CLK_Freq ) DUT ( .mI2C_CTRL_CLK (mI2C_CTRL_CLK ) , .mI2C_CLK_DIV (mI2C_CLK_DIV ) , .mI2C_CLKO (mI2C_CLKO ) , .iRST_N (iRST_N ) , .iCLK (iCLK ) ); initial begin iRST_N = 0; iCLK = 0; #50 iRST_N = 1; end always begin #50 iCLK = ~iCLK; end endmodule

modelsim仿真的波形如下:

图4 IIC内部时钟仿真图

经过计算,IIC内部所用的时钟频率为40KHz。

2、IIC整体仿真

相关程序在附件中。下面是仿真波形。

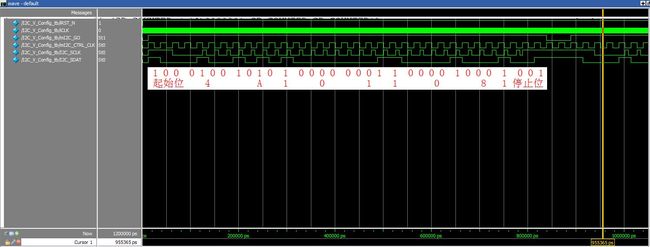

图5 IIC整体仿真波形图

结合上述仿真波形图和程序可以看出:

起始位:SCLK为高电平时,SDAT由高到低,指示IIC总线传输数据的开始;

之后,传送一个字节的数据,即4A,为从机的地址,随后,跟了一个高电平,为应答位;

之后,传送一个字节的数据,即01,为从机地址的子地址,随后,跟了一个高电平,为应答位;

之后,传送一个字节的数据,即08,为上面子地址寄存器配置的数据,随后,跟了一个高电平,为应答位;

最后,为停止位,SCLK为高电平时,SDAT由低到高,指示该次IIC总线传输数据的结束。

由仿真结果可知,当传送完一个字节后,SDAT为一个脉冲的高电平,而不是从器件先将SDAT拉低再拉高,这样也是可以的。