Transistor Tutorial Summary

Transistor Tutorial Summary

Bipolar Junction Transistor Tutorial We can summarise this transistors tutorial section as follows: The Bipolar Junction Transistor (BJT) is a three layer device constructed form two semiconductor diode junctions joined together, one forward biased and one reverse biased. There are two main types of bipolar junction transistors, the NPN and the PNP transistor. Transistors are… Read more »

Darlington Transistors

Darlington Transistor Pair The Darlington Transistor named after its inventor, Sidney Darlington is a special arrangement of two standard NPN or PNP bipolar junction transistors (BJT) connected together. The Emitter of one transistor is connected to the Base of the other to produce a more sensitive transistor with a much larger current gain being useful…Read more »

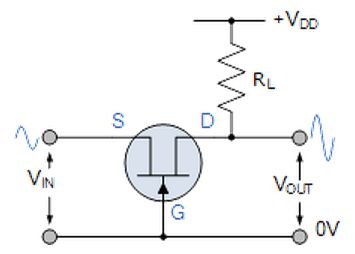

MOSFET as a Switch

The MOSFET

The MOSFET – Metal Oxide FET As well as the Junction Field Effect Transistor (JFET), there is another type of Field Effect Transistor available whose Gate input is electrically insulated from the main current carrying channel and is therefore called an Insulated Gate Field Effect Transistor or IGFET. The most common type of insulated gate… Read more »

Junction Field Effect Transistor

The Field Effect Transistor In the Bipolar Junction Transistor tutorials, we saw that the output Collector current of the transistor is proportional to input current flowing into the Base terminal of the device, thereby making the bipolar transistor a “CURRENT” operated device (Beta model) as a smaller current can be used to switch a larger load… Read more »

Transistor as a Switch

The Transistor as a Switch When used as an AC signal amplifier, the transistors Base biasing voltage is applied in such a way that it always operates within its “active” region, that is the linear part of the output characteristics curves are used. However, both the NPN & PNP type bipolar transistors can be made… Read more »

PNP Transistor

The PNP Transistor The PNP Transistor is the exact opposite to the NPN Transistor device we looked at in the previous tutorial. Basically, in this type of transistor construction the two diodes are reversed with respect to the NPN type giving a Positive-Negative-Positive type of configuration, with the arrow which also defines the Emitter terminal… Read more »

NPN Transistor

The NPN Transistor In the previous tutorial we saw that the standard Bipolar Transistor or BJT, comes in two basic forms. An NPN (Negative-Positive-Negative) type and a PNP (Positive-Negative-Positive) type, with the most commonly used transistor type being the NPN Transistor. We also learnt that the junctions of the bipolar transistor can be biased in…Read more »

Bipolar Transistor

Bipolar Transistor Basics In the Diode tutorials we saw that simple diodes are made up from two pieces of semiconductor material, either silicon or germanium to form a simple PN-junction and we also learnt about their properties and characteristics. If we now join together two individual signal diodes back-to-back, this will give us two PN-junctions…Read more »

Bipolar Junction Transistor Tutorial

We can summarise this transistors tutorial section as follows:

- The Bipolar Junction Transistor (BJT) is a three layer device constructed form two semiconductor diode junctions joined together, one forward biased and one reverse biased.

- There are two main types of bipolar junction transistors, the NPN and the PNP transistor.

- Transistors are “Current Operated Devices” where a much smaller Base current causes a larger Emitter to Collector current, which themselves are nearly equal, to flow.

- The arrow in a transistor symbol represents conventional current flow.

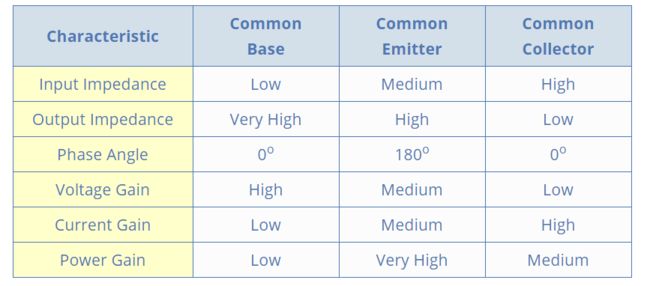

- The most common transistor connection is the Common Emitter (CE) configuration but Common Base (CB) and Common Collector (CC) are also available.

- Requires a Biasing voltage for AC amplifier operation.

- The Base-Emitter junction is always forward biased whereas the Collector-Base junction is always reverse biased.

- The standard equation for currents flowing in a transistor is given as: IE = IB + IC

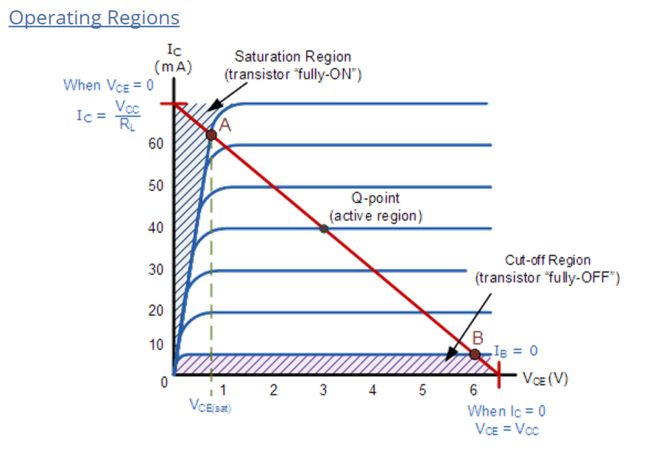

- The Collector or output characteristics curves can be used to find either Ib, Ic or β to which a load line can be constructed to determine a suitable operating point, Q with variations in base current determining the operating range.

- A transistor can also be used as an electronic switch between its saturation and cut-off regions to control devices such as lamps, motors and solenoids etc.

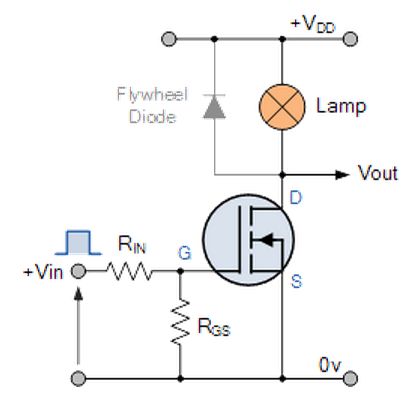

- Inductive loads such as DC motors, relays and solenoids require a reverse biased “Flywheel” diode placed across the load. This helps prevent any induced back emf’s generated when the load is switched “OFF” from damaging the transistor.

- The NPN transistor requires the Base to be more positive than the Emitter while the PNP type requires that the Emitter is more positive than the Base.

Field Effect Transistor Tutorial

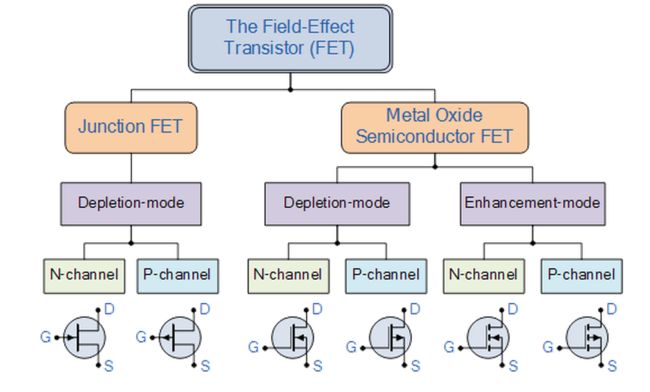

- Field Effect Transistors, or FET’s are “Voltage Operated Devices” and can be divided into two main types: Junction-gate devices called JFET’s and Insulated-gate devices called IGFET´sor more commonly known as MOSFETs.

- Insulated-gate devices can also be sub-divided into Enhancement types and Depletion types. All forms are available in both N-channel and P-channel versions.

- FET’s have very high input resistances so very little or no current (MOSFET types) flows into the input terminal making them ideal for use as electronic switches.

- The input impedance of the MOSFET is even higher than that of the JFET due to the insulating oxide layer and therefore static electricity can easily damage MOSFET devices so care needs to be taken when handling them.

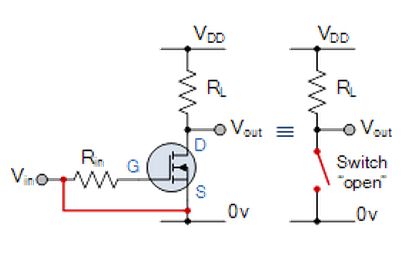

- When no voltage is applied to the gate of an enhancement FET the transistor is in the “OFF” state similar to an “open switch”.

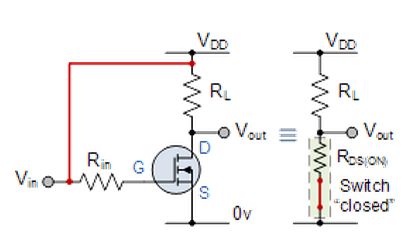

- The depletion FET is inherently conductive and in the “ON” state when no voltage is applied to the gate similar to a “closed switch”.

- FET’s have much higher current gains compared to bipolar junction transistors.

- The most common FET connection is the Common Source (CS) configuration but Common Gate (CG) and Common Drain (CD) configurations are also available.

- MOSFETS can be used as ideal switches due to their very high channel “OFF” resistance, low “ON” resistance.

- To turn the N-channel JFET transistor “OFF”, a negative voltage must be applied to the gate.

- To turn the P-channel JFET transistor “OFF”, a positive voltage must be applied to the gate.

- N-channel depletion MOSFETs are in the “OFF” state when a negative voltage is applied to the gate to create the depletion region.

- P-channel depletion MOSFETs, are in the “OFF” state when a positive voltage is applied to the gate to create the depletion region.

- N-channel enhancement MOSFETs are in the “ON” state when a “+ve” (positive) voltage is applied to the gate.

- P-channel enhancement MOSFETs are in the “ON” state when “-ve” (negative) voltage is applied to the gate.

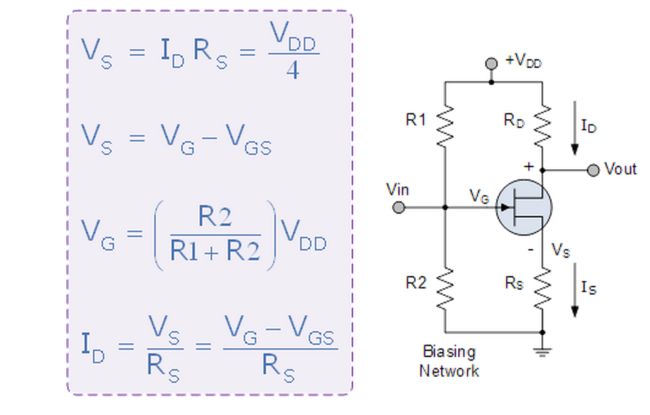

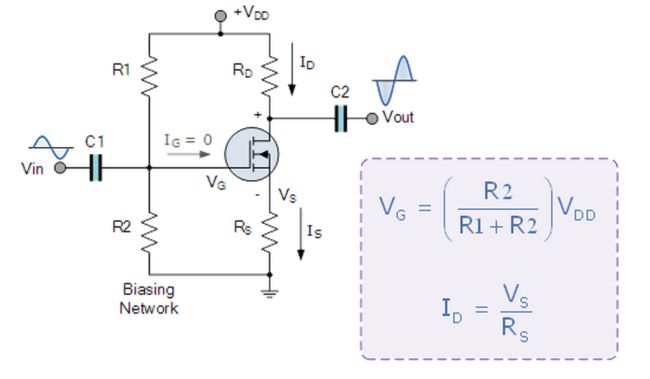

Biasing of the Gate for both the junction field effect transistor, (JFET) and the metal oxide semiconductor field effect transistor, (MOSFET) configurations are given as:

Differences between a FET and a Bipolar Transistor

Field Effect Transistors can be used to replace normal Bipolar Junction Transistors in electronic circuits and a simple comparison between FET’s and Transistors stating both their advantages and their disadvantages is given below.

Below is a list of complementary bipolar transistors which can be used for the general–purpose switching of low-current relays, driving LED’s and lamps, and for amplifier and oscillator applications.

Complementary NPN and PNP Transistors

Bipolar Transistor

Bipolar Transistor Basics

In the Diode tutorials we saw that simple diodes are made up from two pieces of semiconductor material, either silicon or germanium to form a simple PN-junction and we also learnt about their properties and characteristics. If we now join together two individual signal diodes back-to-back, this will give us two PN-junctions connected together in series that share a common P or N terminal. The fusion of these two diodes produces a three layer, two junction, three terminal device forming the basis of a Bipolar Junction Transistor, or BJTfor short.

Transistors are three terminal active devices made from different semiconductor materials that can act as either an insulator or a conductor by the application of a small signal voltage. The transistor’s ability to change between these two states enables it to have two basic functions: “switching” (digital electronics) or “amplification” (analogue electronics). Then Bipolar Transistors have the ability to operate within three different regions:

- • Active Region – the transistor operates as an amplifier and Ic = β.Ib

- • Saturation – the transistor is “Fully-ON” operating as a switch and Ic = I(saturation)

- • Cut-off – the transistor is “Fully-OFF” operating as a switch and Ic = 0

The word Transistor is an acronym, and is a combination of the wordsTransfer Varistor used to describe their mode of operation way back in their early days of development. There are two basic types of bipolar transistor construction, PNP and NPN, which basically describes the physical arrangement of the P-type and N-type semiconductor materials from which they are made.

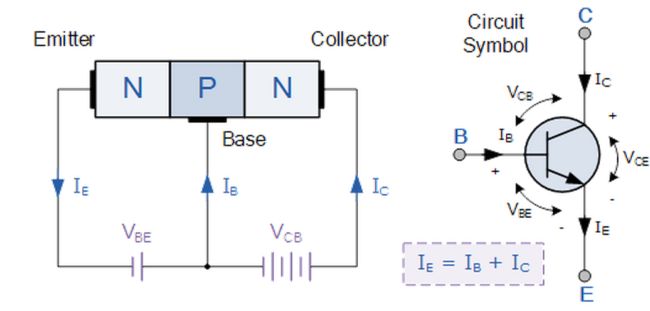

The Bipolar Transistor basic construction consists of two PN-junctions producing three connecting terminals with each terminal being given a name to identify it from the other two. These three terminals are known and labelled as the Emitter ( E ), the Base ( B ) and the Collector ( C ) respectively.

Bipolar Transistors are current regulating devices that control the amount of current flowing through them in proportion to the amount of biasing voltage applied to their base terminal acting like a current-controlled switch. The principle of operation of the two transistor types PNP and NPN, is exactly the same the only difference being in their biasing and the polarity of the power supply for each type.

Bipolar Transistor Construction

The construction and circuit symbols for both the PNP and NPN bipolar transistor are given above with the arrow in the circuit symbol always showing the direction of “conventional current flow” between the base terminal and its emitter terminal. The direction of the arrow always points from the positive P-type region to the negative N-type region for both transistor types, exactly the same as for the standard diode symbol.

Bipolar Transistor Configurations

As the Bipolar Transistor is a three terminal device, there are basically three possible ways to connect it within an electronic circuit with one terminal being common to both the input and output. Each method of connection responding differently to its input signal within a circuit as the static characteristics of the transistor vary with each circuit arrangement.

- • Common Base Configuration – has Voltage Gain but no Current Gain.

- • Common Emitter Configuration – has both Current and Voltage Gain.

- • Common Collector Configuration – has Current Gain but no Voltage Gain.

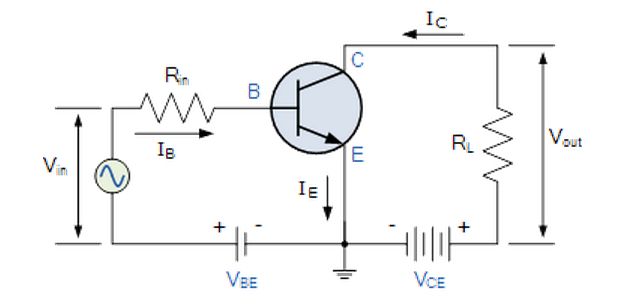

The Common Base (CB) Configuration

As its name suggests, in the Common Base or grounded base configuration, the BASE connection is common to both the input signal AND the output signal with the input signal being applied between the base and the emitter terminals. The corresponding output signal is taken from between the base and the collector terminals as shown with the base terminal grounded or connected to a fixed reference voltage point.

The input current flowing into the emitter is quite large as its the sum of both the base current and collector current respectively therefore, the collector current output is less than the emitter current input resulting in a current gain for this type of circuit of “1” (unity) or less, in other words the common base configuration “attenuates” the input signal.

The Common Base Transistor Circuit

This type of amplifier configuration is a non-inverting voltage amplifier circuit, in that the signal voltages Vin and Vout are “in-phase”. This type of transistor arrangement is not very common due to its unusually high voltage gain characteristics. Its output characteristics represent that of a forward biased diode while the input characteristics represent that of an illuminated photo-diode.

Also this type of bipolar transistor configuration has a high ratio of output to input resistance or more importantly “load” resistance ( RL ) to “input” resistance ( Rin ) giving it a value of “Resistance Gain”. Then the voltage gain ( Av ) for a common base configuration is therefore given as:

Common Base Voltage Gain

Where: Ic/Ie is the current gain, alpha ( α ) and RL/Rin is the resistance gain.

The common base circuit is generally only used in single stage amplifier circuits such as microphone pre-amplifier or radio frequency ( Rf ) amplifiers due to its very good high frequency response.

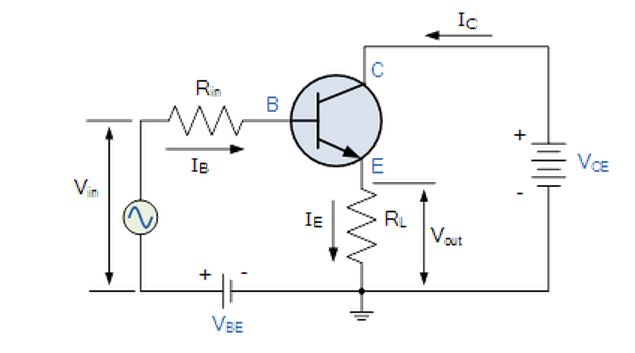

The Common Emitter (CE) Configuration

In the Common Emitter or grounded emitter configuration, the input signal is applied between the base, while the output is taken from between the collector and the emitter as shown. This type of configuration is the most commonly used circuit for transistor based amplifiers and which represents the “normal” method of bipolar transistor connection.

The common emitter amplifier configuration produces the highest current and power gain of all the three bipolar transistor configurations. This is mainly because the input impedance is LOW as it is connected to a forward biased PN-junction, while the output impedance is HIGH as it is taken from a reverse biased PN-junction.

The Common Emitter Amplifier Circuit

In this type of configuration, the current flowing out of the transistor must be equal to the currents flowing into the transistor as the emitter current is given as Ie = Ic + Ib.

As the load resistance ( RL ) is connected in series with the collector, the current gain of the common emitter transistor configuration is quite large as it is the ratio of Ic/Ib. A transistors current gain is given the Greek symbol of Beta, ( β ).

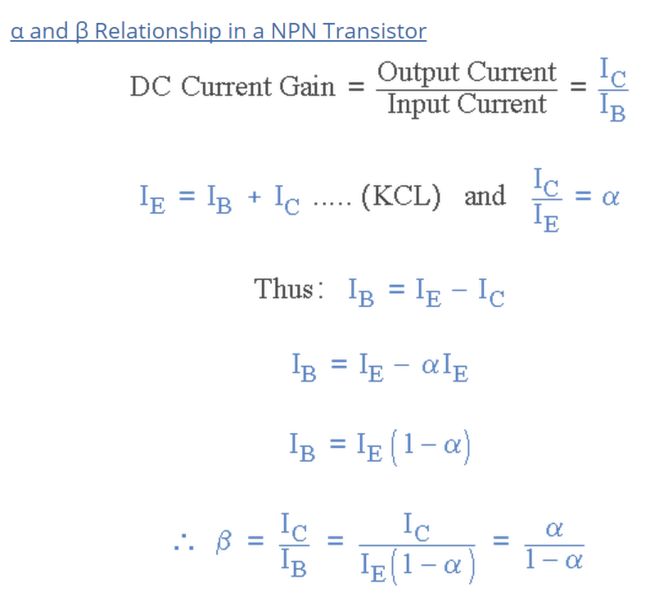

As the emitter current for a common emitter configuration is defined as Ie = Ic + Ib, the ratio of Ic/Ieis called Alpha, given the Greek symbol of α. Note: that the value of Alpha will always be less than unity.

Since the electrical relationship between these three currents, Ib, Ic and Ie is determined by the physical construction of the transistor itself, any small change in the base current ( Ib ), will result in a much larger change in the collector current ( Ic ).

Then, small changes in current flowing in the base will thus control the current in the emitter-collector circuit. Typically, Beta has a value between 20 and 200 for most general purpose transistors. So if a transistor has a Beta value of say 100, then one electron will flow from the base terminal for every 100 electrons flowing between the emitter-collector terminal.

By combining the expressions for both Alpha, α and Beta, β the mathematical relationship between these parameters and therefore the current gain of the transistor can be given as:

Where: “Ic” is the current flowing into the collector terminal, “Ib” is the current flowing into the base terminal and “Ie” is the current flowing out of the emitter terminal.

Then to summarise a little. This type of bipolar transistor configuration has a greater input impedance, current and power gain than that of the common base configuration but its voltage gain is much lower. The common emitter configuration is an inverting amplifier circuit. This means that the resulting output signal is 180o “out-of-phase” with the input voltage signal.

The Common Collector (CC) Configuration

In the Common Collector or grounded collector configuration, the collector is now common through the supply. The input signal is connected directly to the base, while the output is taken from the emitter load as shown. This type of configuration is commonly known as a Voltage Follower or Emitter Follower circuit.

The common collector, or emitter follower configuration is very useful for impedance matching applications because of the very high input impedance, in the region of hundreds of thousands of Ohms while having a relatively low output impedance.

The Common Collector Transistor Circuit

The common emitter configuration has a current gain approximately equal to the β value of the transistor itself. In the common collector configuration the load resistance is situated in series with the emitter so its current is equal to that of the emitter current.

As the emitter current is the combination of the collector AND the base current combined, the load resistance in this type of transistor configuration also has both the collector current and the input current of the base flowing through it. Then the current gain of the circuit is given as:

The Common Collector Current Gain

This type of bipolar transistor configuration is a non-inverting circuit in that the signal voltages ofVin and Vout are “in-phase”. It has a voltage gain that is always less than “1” (unity). The load resistance of the common collector transistor receives both the base and collector currents giving a large current gain (as with the common emitter configuration) therefore, providing good current amplification with very little voltage gain.

We can now summarise the various relationships between the transistors individual DC currents flowing through each leg and its DC current gains given above in the following table.

Relationship between DC Currents and Gains

Bipolar Transistor Summary

Then to summarise, the behaviour of the bipolar transistor in each one of the above circuit configurations is very different and produces different circuit characteristics with regards to input impedance, output impedance and gain whether this is voltage gain, current gain or power gain and this is summarised in the table below.

Bipolar Transistor Configurations

with the characteristics of the different transistor configurations given in the following table:

In the next tutorial about Bipolar Transistors, we will look at the NPN Transistor in more detail when used in the common emitter configuration as an amplifier as this is the most widely used configuration due to its flexibility and high gain. We will also plot the output characteristics curves commonly associated with amplifier circuits as a function of the collector current to the base current.

The NPN Transistor

In the previous tutorial we saw that the standard Bipolar Transistor or BJT, comes in two basic forms. An NPN (Negative-Positive-Negative) type and a PNP (Positive-Negative-Positive) type, with the most commonly used transistor type being the NPN Transistor. We also learnt that the junctions of the bipolar transistor can be biased in one of three different ways – Common Base, Common Emitter and Common Collector.

In this tutorial about bipolar transistors we will look more closely at the “Common Emitter” configuration using the Bipolar NPN Transistor with an example of the construction of a NPN transistor along with the transistors current flow characteristics is given below.

A Bipolar NPN Transistor Configuration

(Note: Arrow defines the emitter and conventional current flow, “out” for a Bipolar NPN Transistor.)

The construction and terminal voltages for a Bipolar NPN Transistor are shown above. The voltage between the Base and Emitter ( VBE ), is positive at the Base and negative at the Emitter because for an NPN transistor, the Base terminal is always positive with respect to the Emitter. Also the Collector supply voltage is positive with respect to the Emitter ( VCE ). So for a bipolar NPN transistor to conduct the Collector is always more positive with respect to both the Base and the Emitter.

Then the voltage sources are connected to an NPN transistor as shown. The Collector is connected to the supply voltage VCC via the load resistor, RL which also acts to limit the maximum current flowing through the device. The Base supply voltage VB is connected to the Base resistor RB, which again is used to limit the maximum Base current.

So in a NPN Transistor it is the movement of negative current carriers (electrons) through the Base region that constitutes transistor action, since these mobile electrons provide the link between the Collector and Emitter circuits. This link between the input and output circuits is the main feature of transistor action because the transistors amplifying properties come from the consequent control which the Base exerts upon the Collector to Emitter current.

Then we can see that the transistor is a current operated device (Beta model) and that a large current ( Ic ) flows freely through the device between the collector and the emitter terminals when the transistor is switched “fully-ON”. However, this only happens when a small biasing current ( Ib ) is flowing into the base terminal of the transistor at the same time thus allowing the Base to act as a sort of current control input.

The transistor current in a bipolar NPN transistor is the ratio of these two currents ( Ic/Ib ), called the DC Current Gain of the device and is given the symbol of hfe or nowadays Beta, ( β ). The value of β can be large up to 200 for standard transistors, and it is this large ratio between Ic and Ib that makes the bipolar NPN transistor a useful amplifying device when used in its active region as Ibprovides the input and Ic provides the output. Note that Beta has no units as it is a ratio.

Also, the current gain of the transistor from the Collector terminal to the Emitter terminal, Ic/Ie, is called Alpha, ( α ), and is a function of the transistor itself (electrons diffusing across the junction). As the emitter current Ie is the sum of a very small base current plus a very large collector current, the value of alpha α, is very close to unity, and for a typical low-power signal transistor this value ranges from about 0.950 to 0.999

By combining the two parameters α and β we can produce two mathematical expressions that gives the relationship between the different currents flowing in the transistor.

The values of Beta vary from about 20 for high current power transistors to well over 1000 for high frequency low power type bipolar transistors. The value of Beta for most standard NPN transistors can be found in the manufactures data sheets but generally range between 50 – 200.

The equation above for Beta can also be re-arranged to make Ic as the subject, and with a zero base current ( Ib = 0 ) the resultant collector current Ic will also be zero, ( β x 0 ). Also when the base current is high the corresponding collector current will also be high resulting in the base current controlling the collector current. One of the most important properties of the Bipolar Junction Transistor is that a small base current can control a much larger collector current. Consider the following example.

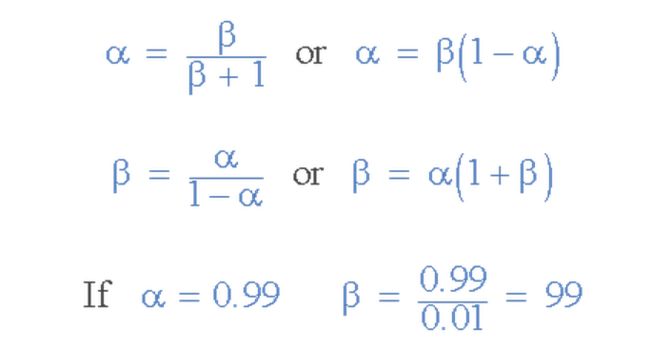

The Common Emitter Configuration.

As well as being used as a semiconductor switch to turn load currents “ON” or “OFF” by controlling the Base signal to the transistor in ether its saturation or cut-off regions, Bipolar NPN Transistorscan also be used in its active region to produce a circuit which will amplify any small AC signal applied to its Base terminal with the Emitter grounded.

If a suitable DC “biasing” voltage is firstly applied to the transistors Base terminal thus allowing it to always operate within its linear active region, an inverting amplifier circuit called a single stage common emitter amplifier is produced.

One such Common Emitter Amplifier configuration of an NPN transistor is called a Class A Amplifier. A “Class A Amplifier” operation is one where the transistors Base terminal is biased in such a way as to forward bias the Base-emitter junction.

The result is that the transistor is always operating halfway between its cut-off and saturation regions, thereby allowing the transistor amplifier to accurately reproduce the positive and negative halves of any AC input signal superimposed upon this DC biasing voltage.

Without this “Bias Voltage” only one half of the input waveform would be amplified. This common emitter amplifier configuration using an NPN transistor has many applications but is commonly used in audio circuits such as pre-amplifier and power amplifier stages.

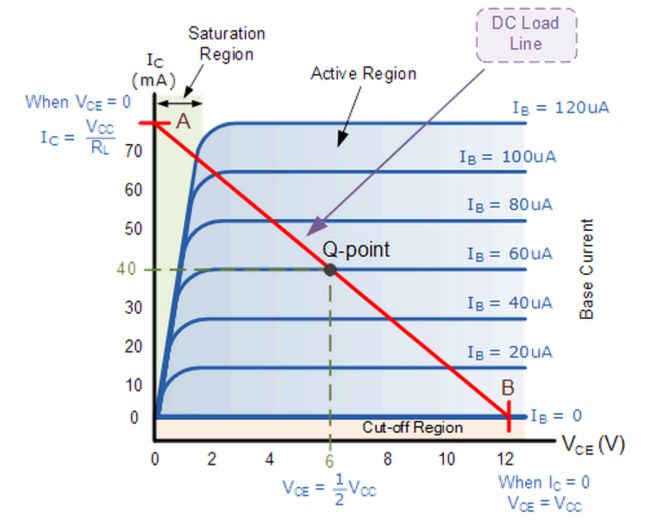

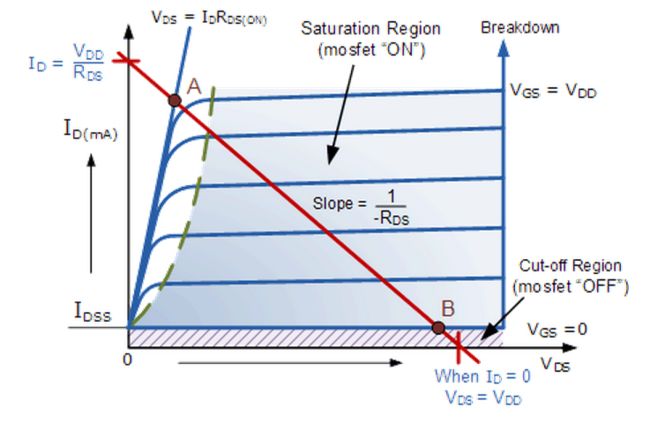

With reference to the Common Emitter Configuration shown below, a family of curves known as theOutput Characteristics Curves, relates the output collector current, ( Ic ) to the collector voltage, ( Vce ) when different values of Base current, ( Ib ). Output characteristics curves are applied to the transistor for transistors with the same β value.

A DC “Load Line” can also be drawn onto the output characteristics curves to show all the possible operating points when different values of base current are applied. It is necessary to set the initial value of Vce correctly to allow the output voltage to vary both up and down when amplifying AC input signals and this is called setting the operating point or Quiescent Point, Q-point for short and this is shown below.

Single Stage Common Emitter Amplifier Circuit

Output Characteristics Curves of a Typical Bipolar Transistor

The most important factor to notice is the effect of Vce upon the collector current Ic when Vce is greater than about 1.0 volts. We can see that Ic is largely unaffected by changes in Vce above this value and instead it is almost entirely controlled by the base current, Ib. When this happens we can say then that the output circuit represents that of a “Constant Current Source”.

It can also be seen from the common emitter circuit above that the emitter current Ie is the sum of the collector current, Ic and the base current, Ib, added together so we can also say that Ie = Ic + Ibfor the common emitter (CE) configuration.

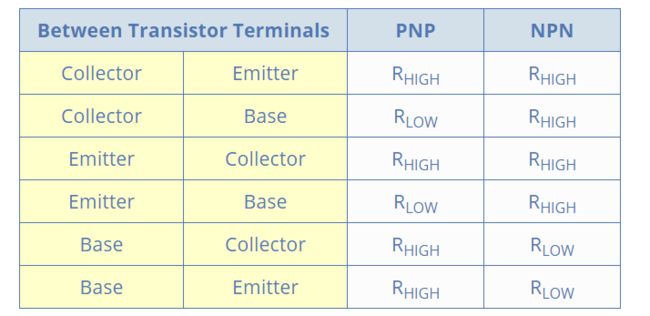

By using the output characteristics curves in our example above and also Ohm´s Law, the current flowing through the load resistor, ( RL ), is equal to the collector current, Ic entering the transistor which in turn corresponds to the supply voltage, ( Vcc ) minus the voltage drop between the collector and the emitter terminals, ( Vce ) and is given as:

Also, a straight line representing the Dynamic Load Line of the transistor can be drawn directly onto the graph of curves above from the point of “Saturation” ( A ) when Vce = 0 to the point of “Cut-off” ( B ) when Ic = 0 thus giving us the “Operating” or Q-point of the transistor. These two points are joined together by a straight line and any position along this straight line represents the “Active Region” of the transistor. The actual position of the load line on the characteristics curves can be calculated as follows:

Then, the collector or output characteristics curves for Common Emitter NPN Transistors can be used to predict the Collector current, Ic, when given Vce and the Base current, Ib. A Load Line can also be constructed onto the curves to determine a suitable Operating or Q-point which can be set by adjustment of the base current. The slope of this load line is equal to the reciprocal of the load resistance which is given as: -1/RL

Then we can define a NPN Transistor as being normally “OFF” but a small input current and a small positive voltage at its Base ( B ) relative to its Emitter ( E ) will turn it “ON” allowing a much large Collector-Emitter current to flow. NPN transistors conduct when Vc is much greater than Ve.

In the next tutorial about Bipolar Transistors, we will look at the opposite or complementary form of the NPN Transistor called the PNP Transistor and show that the PNP Transistor has very similar characteristics to the bipolar NPN transistor except that the polarities (or biasing) of the current and voltage directions are reversed.

The PNP Transistor

The PNP Transistor is the exact opposite to the NPN Transistor device we looked at in the previous tutorial. Basically, in this type of transistor construction the two diodes are reversed with respect to the NPN type giving a Positive-Negative-Positive type of configuration, with the arrow which also defines the Emitter terminal this time pointing inwards in the transistor symbol.

Also, all the polarities for a PNP transistor are reversed which means that it “sinks” current into its Base as opposed to the NPN Transistor which “sources” current through its Base. The main difference between the two types of transistors is that holes are the more important carriers for PNP transistors, whereas electrons are the important carriers for NPN transistors.

Then, PNP transistors use a small base current and a negative base voltage to control a much larger emitter-collector current. In other words for a PNP transistor, the Emitter is more positive with respect to the Base and also with respect to the Collector.

The construction of a “PNP transistor” consists of two P-type semiconductor materials either side of an N-type material as shown below.

A PNP Transistor Configuration

(Note: Arrow defines the emitter and conventional current flow, “in” for a PNP transistor.)

The construction and terminal voltages for an NPN transistor are shown above. The PNP Transistor has very similar characteristics to their NPN bipolar cousins, except that the polarities (or biasing) of the current and voltage directions are reversed for any one of the possible three configurations looked at in the first tutorial, Common Base, Common Emitter and Common Collector.

The voltage between the Base and Emitter ( VBE ), is now negative at the Base and positive at the Emitter because for a PNP transistor, the Base terminal is always biased negative with respect to the Emitter.

Also the Emitter supply voltage is positive with respect to the Collector ( VCE ). So for a PNP transistor to conduct the Emitter is always more positive with respect to both the Base and the Collector.

The voltage sources are connected to a PNP transistor are as shown. This time the Emitter is connected to the supply voltage VCC with the load resistor, RL which limits the maximum current flowing through the device connected to the Collector terminal. The Base voltage VB which is biased negative with respect to the Emitter and is connected to the Base resistor RB, which again is used to limit the maximum Base current.

To cause the Base current to flow in a PNP transistor the Base needs to be more negative than the Emitter (current must leave the base) by approx 0.7 volts for a silicon device or 0.3 volts for a germanium device with the formulas used to calculate the Base resistor, Base current or Collector current are the same as those used for an equivalent NPN transistor and is given as.

We can see that the fundamental differences between a NPN Transistor and a PNP Transistor is the proper biasing of the transistors junctions as the current directions and voltage polarities are always opposite to each other. So for the circuit above: Ic = Ie – Ib as current must leave the Base.

Generally, the PNP transistor can replace NPN transistors in most electronic circuits, the only difference is the polarities of the voltages, and the directions of the current flow. PNP transistors can also be used as switching devices and an example of a PNP transistor switch is shown below.

A PNP Transistor Circuit

The Output Characteristics Curves for a PNP transistor look very similar to those for an equivalent NPN transistor except that they are rotated by 180o to take account of the reverse polarity voltages and currents, (the currents flowing out of the Base and Collector in a PNP transistor are negative). The same dynamic load line can be drawn onto the I-V curves to find the PNP transistors operating points.

Transistor Matching

You may think what is the point of having a PNP Transistor, when there are plenty of NPN Transistors available that can be used as an amplifier or solid-state switch?. Well, having two different types of transistors “PNP” and “NPN”, can be a great advantage when designing power amplifier circuits such as the Class B Amplifier.

Class-B amplifiers uses “Complementary” or “Matched Pair” (that is one PNP and one NPN connected together) transistors in its output stage or in reversible H-Bridge motor control circuits were we want to control the flow of current evenly through the motor in both directions.

A pair of corresponding NPN and PNP transistors with near identical characteristics to each other are calledComplementary Transistors for example, a TIP3055 (NPN transistor) and the TIP2955 (PNP transistor) are good examples of complementary or matched pair silicon power transistors. They both have a DC current gain, Beta, ( Ic/Ib ) matched to within 10% and high Collector current of about 15A making them ideal for general motor control or robotic applications.

Also, class B amplifiers use complementary NPN and PNP in their power output stage design. The NPN transistor conducts for only the positive half of the signal while the PNP transistor conducts for negative half of the signal.

This allows the amplifier to drive the required power through the load loudspeaker in both directions at the stated nominal impedance and power resulting in an output current which is likely to be in the order of several amps shared evenly between the two complementary transistors.

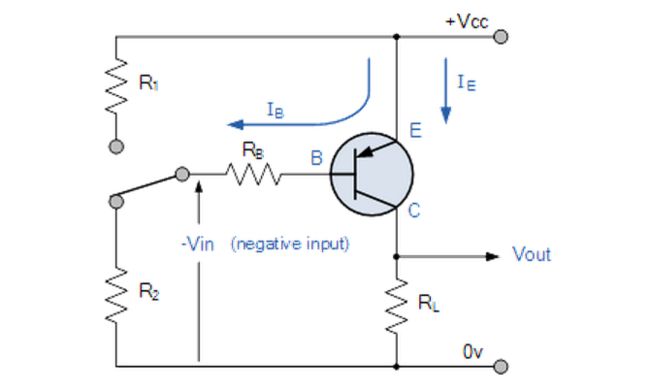

Identifying the PNP Transistor

We saw in the first tutorial of this transistors section, that transistors are basically made up of twoDiodes connected together back-to-back.

We can use this analogy to determine whether a transistor is of the PNP type or NPN type by testing its Resistance between the three different leads, Emitter, Base and Collector. By testing each pair of transistor leads in both directions with a multimeter will result in six tests in total with the expected resistance values in Ohm’s given below.

- 1. Emitter-Base Terminals – The Emitter to Base should act like a normal diode and conduct one way only.

- 2. Collector-Base Terminals – The Collector-Base junction should act like a normal diode and conduct one way only.

- 3. Emitter-Collector Terminals – The Emitter-Collector should not conduct in either direction.

Transistor Resistance Values for a PNP Transistor and a NPN Transistor

Then we can define a PNP Transistor as being normally “OFF” but a small output current and negative voltage at its Base ( B ) relative to its Emitter ( E ) will turn it “ON” allowing a much large Emitter-Collector current to flow. PNP transistors conduct when Ve is much greater than Vc.

In other words, a Bipolar PNP Transistor will ONLY conduct if both the Base and Collector terminals are negative with respect to the Emitter

In the next tutorial about Bipolar Transistors instead of using the transistor as an amplifying device, we will look at the operation of the transistor in its saturation and cut-off regions when used as a solid-state switch. Bipolar transistor switches are used in many applications to switch a DC current “ON” or “OFF”, from LED’s which require only a few milliamps of switching current at low DC voltages, or motors and relays which may require higher currents at higher voltages.

Darlington Transistors

Darlington Transistor Pair

The Darlington Transistor named after its inventor, Sidney Darlington is a special arrangement of two standard NPN or PNP bipolar junction transistors (BJT) connected together. The Emitter of one transistor is connected to the Base of the other to produce a more sensitive transistor with a much larger current gain being useful in applications where current amplification or switching is required.

Darlington Transistor pairs can be made from two individually connected Bipolar Transistors or a one single device commercially made in a single package with the standard: Base, Emitter and Collector connecting leads and are available in a wide variety of case styles and voltage (and current) ratings in both NPN and PNP versions.

As we saw in our Transistor As A Switch tutorial, as well as being used as an amplifier, the bipolar junction transistor, (BJT) can be made to operate as an ON-OFF switch as shown.

Bipolar Transistor as a Switch

When the base of the NPN transistor is grounded (0 volts) and no base current, Ib flows, no current flows from the emitter to the collector and the transistor is therefore switched “OFF”. If the base is forward biased by more than 0.7 volts, a current will flow from the emitter to the collector and the transistor is said to be switched “ON”. When operated in these two modes, the transistor operates as a switch.

The problem here is that the transistors base needs to be switched between zero and some large, positive value for the transistor to become saturated at which point an increased base current, Ibflows into the device resulting in collector current Ic becoming large while Vce is small. Then we can see that a small current on the base can control a much larger current flowing between the collector and the emitter.

The ratio of collector current to base current ( β ) is known as the current gain of the transistor. A typical value of β for a standard bipolar transistor may be in the range of 50 to 200 and varies even between transistors of the same part number. In some cases where the current gain of a single transistor is too low to directly drive a load, one way to increase the gain is to use a Darlington pair.

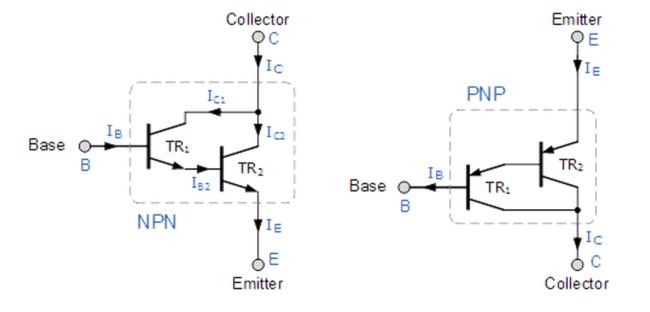

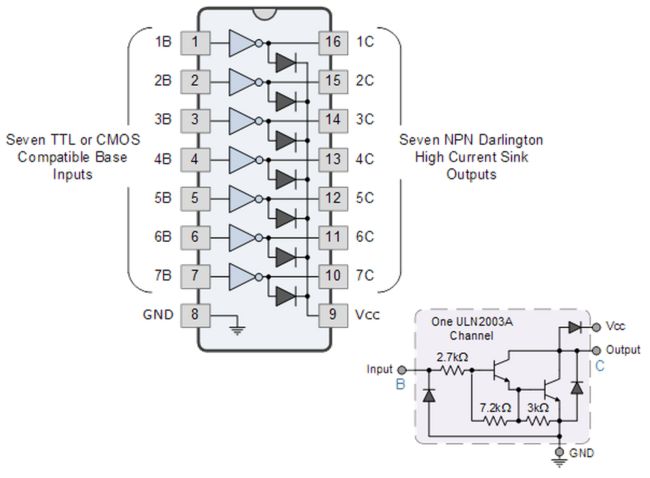

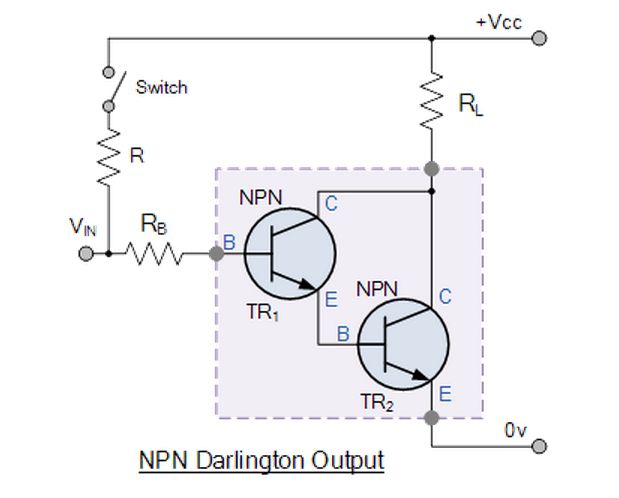

A Darlington Transistor configuration, also known as a “Darlington pair” or “super-alpha circuit”, consist of two NPN or PNP transistors connected together so that the emitter current of the first transistor TR1 becomes the base current of the second transistor TR2. Then transistor TR1 is connected as an emitter follower and TR2 as a common emitter amplifier as shown below.

Also note that in this Darlington pair configuration, the collector current of the slave or control transistor, TR1 is “in-phase” with that of the master switching transistor TR2.

Basic Darlington Transistor Configuration

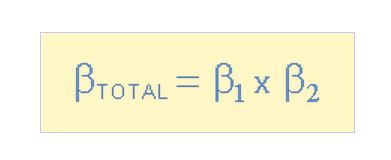

Using the NPN Darlington pair as the example, the collectors of two transistors are connected together, and the emitter of TR1 drives the base of TR2. This configuration achieves β multiplication because for a base current ib, the collector current is β.ib where the current gain is greater than one, or unity and this is defined as:

But the base current, IB2 is equal to transistor TR1 emitter current, IE1 as the emitter of TR1 is connected to the base of TR2. Therefore:

Then substituting in the first equation:

![]()

Where β1 and β2 are the gains of the individual transistors.

This means that the overall current gain, β is given by the gain of the first transistor multiplied by the gain of the second transistor as the current gains of the two transistors multiply. In other words, a pair of bipolar transistors combined together to make a single Darlington transistor pair can be regarded as a single transistor with a very high value of β and consequently a high input resistance.

Darlington Transistor Applications

The base of the Darlington transistor is sufficiently sensitive to respond to any small input current from a switch or directly from a TTL or 5V CMOS logic gate. The maximum collector current Ic(max)for any Darlington pair is the same as that for the main switching transistor, TR2 so can be used to operate relays, DC motors, solenoids and lamps, etc.

One of the main disadvantage of a Darlington transistor pair is the minimum voltage drop between the base and emitter when fully saturated. Unlike a single transistor which has a saturated voltage drop of between 0.3v and 0.7v when fully-ON, a Darlington device has twice the base-emitter voltage drop (1.2 V instead of 0.6 V) as the base-emitter voltage drop is the sum of the base-emitter diode drops of the two individual transistors which can be between 0.6v to 1.5v depending on the current through the transistor.

This high base-emitter voltage drop means that the Darlington transistor can get hotter than a normal bipolar transistor for a given load current and therefore requires good heat sinking. Also, Darlington transistors have slower ON-OFF response times as it takes longer for the slave transistorTR1 to turn the master transistor TR1 either fully-ON or fully-OFF.

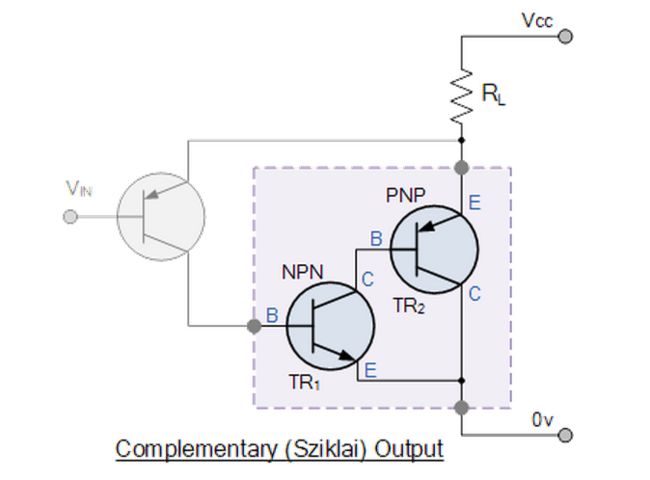

To overcome the slow response, increased voltage drop and thermal disadvantages of a standardDarlington Transistor device, complementary NPN and PNP transistors can be used in the same cascaded arrangement to produce another type of Darlington transistor called a Sziklai Configuration.

Sziklai Transistor Pair

The Sziklai Darlington Pair, named after its Hungarian inventor George Sziklai, is a complementary or compound Darlington device that consists of separate NPN and PNPcomplementary transistors connected together as shown below.

This cascaded combination of NPN and PNP transistors has the advantage that the Sziklai pair performs the same basic function of a Darlington pair except that it only requires 0.6v for it to turn-ON and like the standard Darlington configuration, the current gain is equal to β2 for equally matched transistors or is given by the product of the two current gains for unmatched individual transistors.

Sziklai Darlington Transistor Configuration

We can see that the base-emitter voltage drop of the Sziklai device is equal to the diode drop of a single transistor in the signal path. However, the Sziklai configuration can not saturate to less than one whole diode drop, i.e. 0.7v instead of the usual 0.2v.

Also, as with the Darlington pair, the Sziklai pair have slower response times than a single transistor. Sziklai pair complementary transistors are commonly used in push-pull and class AB audio amplifier output stages allowing for one polarity of output transistor only. Both the Darlington and Sziklai transistor pairs are available in both NPN and PNP configurations.

Darlington Transistor IC’s

In most electronics applications it is sufficient for the controlling circuit to switch a DC output voltage or current “ON” or “OFF” directly as some output devices such as LED’s or displays only require a few milliamps to operate at low DC voltages and can therefore be driven directly by the output of a standard logic gate.

However as we have seen above, sometimes more power is required to operate the output device such as a DC motor than can be supplied by an ordinary logic gate or micro-controller. If the digital logic device cannot supply sufficient current then additional circuitry will be required to drive the device.

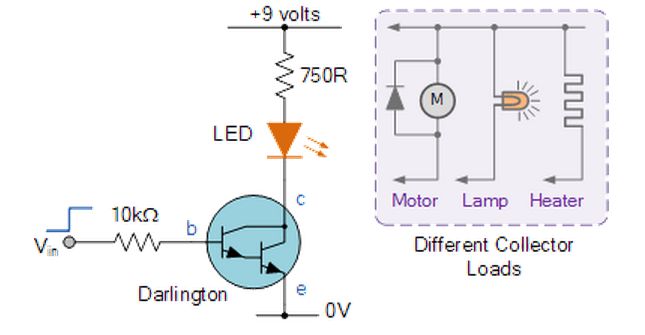

One such commonly used Darlington transistor chip is the ULN2003 array. The family of darlington arrays consist of the ULN2002A, ULN2003A and the ULN2004A which are all high voltage, high current darlington arrays each containing seven open collector darlington pairs within a single IC package.

Each channel of the array is rated at 500mA and can withstand peak currents of up to 600mA making it ideal for controlling small motors or lamps or the gates and bases of high power semiconductors. Additional suppression diodes are included for inductive load driving and the inputs are pinned opposite the outputs to simplify the connections and board layout.

The ULN2003A Darlington Transistor Array

The ULN2003A is a inexpensive unipolar darlington transistor array with high efficiency and low power consumption making it useful for driving a wide range of loads including solenoids, relays DC Motor’s and LED displays or filament lamps. The ULN2003A contains seven darlington transistor pairs each with an input pin on the left and an output pin opposite it on the right as shown.

ULN2003A Darlington Transistor Array

The ULN2003A Darlington driver has an extremely high input impedance and current gain which can be driven directly from either a TTL or +5V CMOS logic gate. For +15V CMOS logic use the ULN2004A and for higher switching voltages up to 100V it is better to use the SN75468 Darlington array.

When an input (pins 1 to 7) is driven “HIGH” the corresponding output will switch “LOW” sinking current. Likewise, when the input is driven “LOW” the corresponding output switches to a high impedance state. This high impedance “OFF” state blocks load current and reduces leakage current through the device improving efficiency.

Pin 8, (GND) is connected to the loads ground or 0 volts, while pin 9 (Vcc) connects to the loads supply. Then any load needs to be connected between +Vcc and an output pin, pins 10 to 16. For inductive loads such as motors, relays and solenoids, etc, pin 9 should always be connected to Vcc.

The ULN2003A is capable of switching 500mA (0.5A) per channel but if more switching current capability is required then both the Darlington pairs inputs and outputs can be paralleled together for higher current capability. For example, input pins 1 and 2 connected together and output pins 16 and 15 connected together to switch the load.

Darlington Transistor Summary

The Darlington Transistor is a high power semiconductor device with individual current and voltage ratings many times higher than a conventional small signal junction transistors.

The DC current gain values for standard high power NPN or PNP transistors are relatively low, as low as 20 or even less, compared to small signal switching transistors. This means that large base currents are required to switch a given load.

The Darlington arrangement uses two transistors back to back, one of which is the main current carrying transistor, while the other being a much smaller “switching” transistor provides the base current to drive the main transistor. As a result, a smaller base current can be used to switch a much larger load current as the DC current gains of the two transistors are multiplied together. Then the two transistor combination can be regarded as one single transistor with a very high value of β and consequently a high input resistance.

As well as standard PNP and NPN Darlington transistor pairs, complementary Sziklai Darlington transistors are also available which consist of separate matching NPN and PNP complementary transistors connected together within the same Darlington pair to improve efficiency. Also Darlington arrays such as the ULN2003A are available which allow high power or inductive loads such as lamps, solenoids and motors to be safely driven by microprocessor and micro-controller devices in robotic and mechatronic type applications.

Transistor as a Switch

The Transistor as a Switch

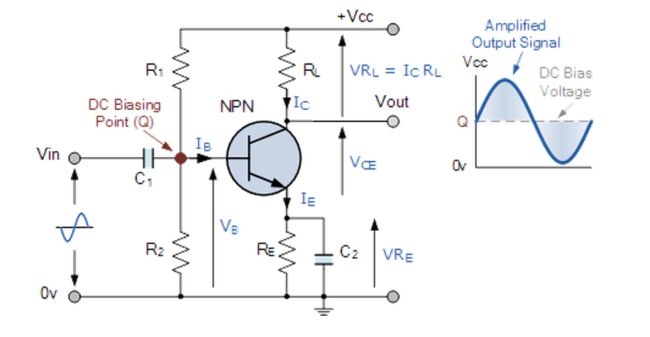

When used as an AC signal amplifier, the transistors Base biasing voltage is applied in such a way that it always operates within its “active” region, that is the linear part of the output characteristics curves are used. However, both the NPN & PNP type bipolar transistors can be made to operate as “ON/OFF” type solid state switches by biasing the transistors base differently to that of a signal amplifier.

Solid state switches are one of the main applications for the use of transistors, and transistor switches can be used for controlling high power devices such as motors, solenoids or lamps, but they can also used in digital electronics and logic gate circuits.

If the circuit uses the Bipolar Transistor as a Switch, then the biasing of the transistor, either NPN or PNP is arranged to operate the transistor at both sides of the “ I-V ” characteristics curves we have seen previously.

The areas of operation for a Transistor Switch are known as the Saturation Region and the Cut-off Region. This means then that we can ignore the operating Q-point biasing and voltage divider circuitry required for amplification, and use the transistor as a switch by driving it back and forth between its “fully-OFF” (cut-off) and “fully-ON” (saturation) regions as shown below.

The pink shaded area at the bottom of the curves represents the “Cut-off” region while the blue area to the left represents the “Saturation” region of the transistor. Both these transistor regions are defined as:

1. Cut-off Region

Here the operating conditions of the transistor are zero input base current ( IB ), zero output collector current ( IC ) and maximum collector voltage ( VCE ) which results in a large depletion layer and no current flowing through the device. Therefore the transistor is switched “Fully-OFF”.

Cut-off Characteristics

![]()

- The input and Base are grounded ( 0v )

- • Base-Emitter voltage VBE < 0.7v

- • Base-Emitter junction is reverse biased

- • Base-Collector junction is reverse biased

- • Transistor is “fully-OFF” ( Cut-off region )

- • No Collector current flows ( IC = 0 )

- • VOUT = VCE = VCC = ”1″

- • Transistor operates as an “open switch”

Then we can define the “cut-off region” or “OFF mode” when using a bipolar transistor as a switch as being, both junctions reverse biased, VB < 0.7v and IC = 0. For a PNP transistor, the Emitter potential must be negative with respect to the Base.

2. Saturation Region

Here the transistor will be biased so that the maximum amount of base current is applied, resulting in maximum collector current resulting in the minimum collector emitter voltage drop which results in the depletion layer being as small as possible and maximum current flowing through the transistor. Therefore the transistor is switched “Fully-ON”.

Saturation Characteristics

- The input and Base are connected to VCC

- • Base-Emitter voltage VBE > 0.7v

- • Base-Emitter junction is forward biased

- • Base-Collector junction is forward biased

- • Transistor is “fully-ON” ( saturation region )

- • Max Collector current flows ( IC = Vcc/RL )

- • VCE = 0 ( ideal saturation )

- • VOUT = VCE = ”0″

- • Transistor operates as a “closed switch”

Then we can define the “saturation region” or “ON mode” when using a bipolar transistor as a switch as being, both junctions forward biased, VB > 0.7v and IC = Maximum. For a PNP transistor, the Emitter potential must be positive with respect to the Base.

Then the transistor operates as a “single-pole single-throw” (SPST) solid state switch. With a zero signal applied to the Base of the transistor it turns “OFF” acting like an open switch and zero collector current flows. With a positive signal applied to the Base of the transistor it turns “ON” acting like a closed switch and maximum circuit current flows through the device.

An example of an NPN Transistor as a switch being used to operate a relay is given below. With inductive loads such as relays or solenoids a flywheel diode is placed across the load to dissipate the back EMF generated by the inductive load when the transistor switches “OFF” and so protect the transistor from damage. If the load is of a very high current or voltage nature, such as motors, heaters etc, then the load current can be controlled via a suitable relay as shown.

Basic NPN Transistor Switching Circuit

The circuit resembles that of the Common Emitter circuit we looked at in the previous tutorials. The difference this time is that to operate the transistor as a switch the transistor needs to be turned either fully “OFF” (cut-off) or fully “ON” (saturated). An ideal transistor switch would have infinite circuit resistance between the Collector and Emitter when turned “fully-OFF” resulting in zero current flowing through it and zero resistance between the Collector and Emitter when turned “fully-ON”, resulting in maximum current flow.

In practice when the transistor is turned “OFF”, small leakage currents flow through the transistor and when fully “ON” the device has a low resistance value causing a small saturation voltage ( VCE ) across it. Even though the transistor is not a perfect switch, in both the cut-off and saturation regions the power dissipated by the transistor is at its minimum.

In order for the Base current to flow, the Base input terminal must be made more positive than the Emitter by increasing it above the 0.7 volts needed for a silicon device. By varying this Base-Emitter voltage VBE, the Base current is also altered and which in turn controls the amount of Collector current flowing through the transistor as previously discussed.

When maximum Collector current flows the transistor is said to be Saturated. The value of the Base resistor determines how much input voltage is required and corresponding Base current to switch the transistor fully “ON”.

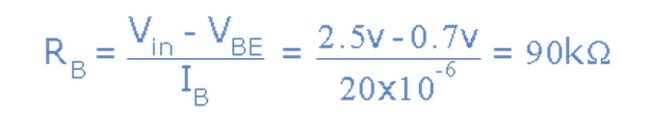

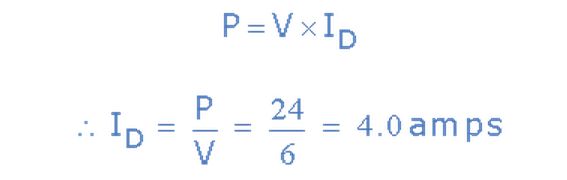

Transistor as a Switch Example No1

Using the transistor values from the previous tutorials of: β = 200, Ic = 4mA and Ib = 20uA, find the value of the Base resistor (Rb) required to switch the load fully “ON” when the input terminal voltage exceeds 2.5v.

The next lowest preferred value is: 82kΩ, this guarantees the transistor switch is always saturated.

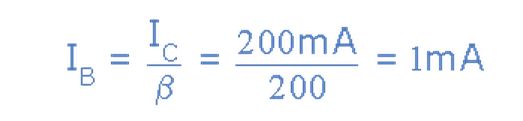

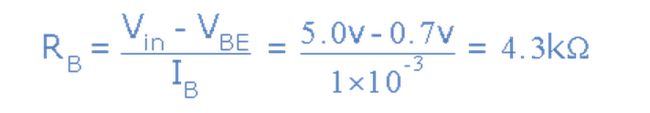

Transistor as a Switch Example No2

Again using the same values, find the minimum Base current required to turn the transistor “fully-ON” (saturated) for a load that requires 200mA of current when the input voltage is increased to 5.0V. Also calculate the new value of Rb.

Transistor Base current:

Transistor Base resistance:

Transistor switches are used for a wide variety of applications such as interfacing large current or high voltage devices like motors, relays or lamps to low voltage digital logic IC’s or gates like ANDgates or OR gates. Here, the output from a digital logic gate is only +5v but the device to be controlled may require a 12 or even 24 volts supply. Or the load such as a DC Motor may need to have its speed controlled using a series of pulses (Pulse Width Modulation). transistor switches will allow us to do this faster and more easily than with conventional mechanical switches.

Digital Logic Transistor Switch

The base resistor, Rb is required to limit the output current from the logic gate.

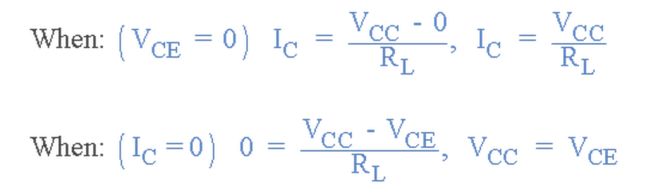

PNP Transistor Switch

We can also use the PNP Transistors as a switch, the difference this time is that the load is connected to ground (0v) and the PNP transistor switches the power to it. To turn the PNP transistor operating as a switch “ON”, the Base terminal is connected to ground or zero volts (LOW) as shown.

PNP Transistor Switching Circuit

The equations for calculating the Base resistance, Collector current and voltages are exactly the same as for the previous NPN transistor switch. The difference this time is that we are switching power with a PNP transistor (sourcing current) instead of switching ground with an NPN transistor (sinking current).

Darlington Transistor Switch

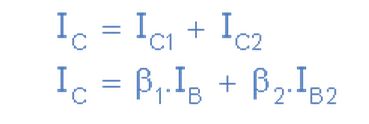

Sometimes the DC current gain of the bipolar transistor is too low to directly switch the load current or voltage, so multiple switching transistors are used. Here, one small input transistor is used to switch “ON” or “OFF” a much larger current handling output transistor. To maximise the signal gain, the two transistors are connected in a “Complementary Gain Compounding Configuration” or what is more commonly called a “Darlington Configuration” were the amplification factor is the product of the two individual transistors.

Darlington Transistors simply contain two individual bipolar NPN or PNP type transistors connected together so that the current gain of the first transistor is multiplied with that of the current gain of the second transistor to produce a device which acts like a single transistor with a very high current gain for a much smaller Base current. The overall current gain Beta (β) or Hfevalue of a Darlington device is the product of the two individual gains of the transistors and is given as:

So Darlington Transistors with very high β values and high Collector currents are possible compared to a single transistor switch. For example, if the first input transistor has a current gain of 100 and the second switching transistor has a current gain of 50 then the total current gain will be 100 x 50 = 5000. So for example, if our load current from above is 200mA, then the darlington base current is only 200mA/5000 = 40uA. A huge reduction from the previous 1mA for a single transistor.

An example of the two basic types of Darlington transistor configurations are given below.

Darlington Transistor Configurations

The above NPN Darlington transistor switch configuration shows the Collectors of the two transistors connected together with the Emitter of the first transistor connected to the Base terminal of the second transistor therefore, the Emitter current of the first transistor becomes the Base current of the second transistor switching it “ON”.

The first or “input” transistor receives the input signal to its Base. This transistor amplifies it in the usual way and uses it to drive the second larger “output” transistors. The second transistor amplifies the signal again resulting in a very high current gain. One of the main characteristics ofDarlington Transistors is their high current gains compared to single bipolar transistors.

As well as its high increased current and voltage switching capabilities, another advantage of a “Darlington Transistor Switch” is in its high switching speeds making them ideal for use in inverter circuits, lighting circuits and DC motor or stepper motor control applications.

One difference to consider when using Darlington transistors over the conventional single bipolar types when using the transistor as a switch is that the Base-Emitter input voltage ( VBE ) needs to be higher at approx 1.4v for silicon devices, due to the series connection of the two PN junctions.

Transistor as a Switch Summary

Then to summarise when using a Transistor as a Switch the following conditions apply:

- Transistor switches can be used to switch and control lamps, relays or even motors.

- When using the bipolar transistor as a switch they must be either “fully-OFF” or “fully-ON”.

- Transistors that are fully “ON” are said to be in their Saturation region.

- Transistors that are fully “OFF” are said to be in their Cut-off region.

- When using the transistor as a switch, a small Base current controls a much larger Collector load current.

- When using transistors to switch inductive loads such as relays and solenoids, a “Flywheel Diode” is used.

- When large currents or voltages need to be controlled, Darlington Transistors can be used.

In the next tutorial about Transistors, we will look at the operation of the junction field effect transistor known commonly as an JFET. We will also plot the output characteristics curves commonly associated with JFET amplifier circuits as a function of Source voltage to Gate voltage.

Junction Field Effect Transistor

The Field Effect Transistor

In the Bipolar Junction Transistor tutorials, we saw that the output Collector current of the transistor is proportional to input current flowing into the Base terminal of the device, thereby making the bipolar transistor a “CURRENT” operated device (Beta model) as a smaller current can be used to switch a larger load current.

The Field Effect Transistor, or simply FET however, uses the voltage that is applied to their input terminal, called the Gate to control the current flowing through them resulting in the output current being proportional to the input voltage. As their operation relies on an electric field (hence the name field effect) generated by the input Gate voltage, this then makes the Field Effect Transistor a “VOLTAGE” operated device.

Typical Field Effect Transistor

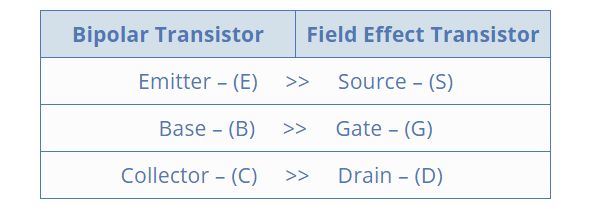

The Field Effect Transistor is a three terminal unipolar semiconductor device that has very similar characteristics to those of their Bipolar Transistor counterparts ie, high efficiency, instant operation, robust and cheap and can be used in most electronic circuit applications to replace their equivalent bipolar junction transistors (BJT) cousins.

Field effect transistors can be made much smaller than an equivalent BJT transistor and along with their low power consumption and power dissipation makes them ideal for use in integrated circuits such as the CMOS range of digital logic chips.

We remember from the previous tutorials that there are two basic types of Bipolar Transistor Construction, NPN and PNP, which basically describes the physical arrangement of the P-type and N-type semiconductor materials from which they are made. This is also true of FET’s as there are also two basic classifications of Field Effect Transistor, called the N-channel FET and the P-channel FET.

The field effect transistor is a three terminal device that is constructed with no PN-junctions within the main current carrying path between the Drain and the Source terminals, which correspond in function to the Collector and the Emitter respectively of the bipolar transistor. The current path between these two terminals is called the “channel” which may be made of either a P-type or an N-type semiconductor material.

The control of current flowing in this channel is achieved by varying the voltage applied to the Gate. As their name implies, Bipolar Transistors are “Bipolar” devices because they operate with both types of charge carriers, Holes and Electrons. The Field Effect Transistor on the other hand is a “Unipolar” device that depends only on the conduction of electrons (N-channel) or holes (P-channel).

The Field Effect Transistor has one major advantage over its standard bipolar transistor cousins, in that their input impedance, ( Rin ) is very high, (thousands of Ohms), while the BJT is comparatively low. This very high input impedance makes them very sensitive to input voltage signals, but the price of this high sensitivity also means that they can be easily damaged by static electricity.

There are two main types of field effect transistor, the Junction Field Effect Transistor or JFET and the Insulated-gate Field Effect Transistor or IGFET), which is more commonly known as the standard Metal Oxide Semiconductor Field Effect Transistor or MOSFET for short.

The Junction Field Effect Transistor

We saw previously that a bipolar junction transistor is constructed using two PN-junctions in the main current carrying path between the Emitter and the Collector terminals. The Junction Field Effect Transistor (JUGFET or JFET) has no PN-junctions but instead has a narrow piece of high resistivity semiconductor material forming a “Channel” of either N-type or P-type silicon for the majority carriers to flow through with two ohmic electrical connections at either end commonly called the Drain and the Source respectively.

There are two basic configurations of junction field effect transistor, the N-channel JFET and the P-channel JFET. The N-channel JFET’s channel is doped with donor impurities meaning that the flow of current through the channel is negative (hence the term N-channel) in the form of electrons.

Likewise, the P-channel JFET’s channel is doped with acceptor impurities meaning that the flow of current through the channel is positive (hence the term P-channel) in the form of holes. N-channel JFET’s have a greater channel conductivity (lower resistance) than their equivalent P-channel types, since electrons have a higher mobility through a conductor compared to holes. This makes the N-channel JFET’s a more efficient conductor compared to their P-channel counterparts.

We have said previously that there are two ohmic electrical connections at either end of the channel called the Drain and the Source. But within this channel there is a third electrical connection which is called the Gate terminal and this can also be a P-type or N-type material forming a PN-junction with the main channel. The relationship between the connections of a junction field effect transistor and a bipolar junction transistor are compared below.

Comparison of Connections between a JFET and a BJT

The symbols and basic construction for both configurations of JFETs are shown below.

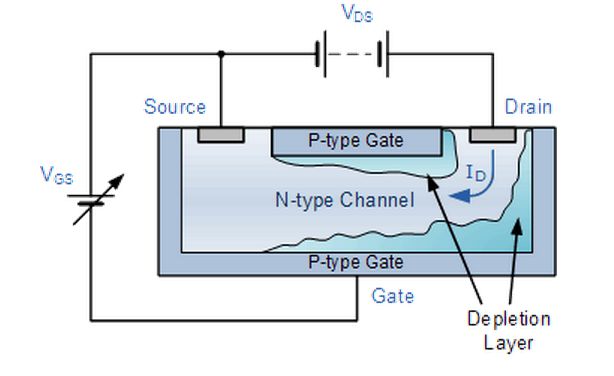

The semiconductor “channel” of the Junction Field Effect Transistor is a resistive path through which a voltage VDS causes a current ID to flow and as such the junction field effect transistor can conduct current equally well in either direction. As the channel is resistive in nature, a voltage gradient is thus formed down the length of the channel with this voltage becoming less positive as we go from the Drain terminal to the Source terminal.

The result is that the PN-junction therefore has a high reverse bias at the Drain terminal and a lower reverse bias at the Source terminal. This bias causes a “depletion layer” to be formed within the channel and whose width increases with the bias.

The magnitude of the current flowing through the channel between the Drain and the Source terminals is controlled by a voltage applied to the Gate terminal, which is a reverse-biased. In an N-channel JFET this Gate voltage is negative while for a P-channel JFET the Gate voltage is positive. The main difference between the JFET and a BJT device is that when the JFET junction is reverse-biased the Gate current is practically zero, whereas the Base current of the BJT is always some value greater than zero.

Biasing of an N-channel JFET

The cross sectional diagram above shows an N-type semiconductor channel with a P-type region called the Gate diffused into the N-type channel forming a reverse biased PN-junction and it is this junction which forms the depletion region around the Gate area when no external voltages are applied. JFETs are therefore known as depletion mode devices.

This depletion region produces a potential gradient which is of varying thickness around the PN-junction and restrict the current flow through the channel by reducing its effective width and thus increasing the overall resistance of the channel itself.

Then we can see that the most-depleted portion of the depletion region is in between the Gate and the Drain, while the least-depleted area is between the Gate and the Source. Then the JFET’s channel conducts with zero bias voltage applied (ie, the depletion region has near zero width).

With no external Gate voltage ( VG = 0 ), and a small voltage ( VDS ) applied between the Drain and the Source, maximum saturation current ( IDSS ) will flow through the channel from the Drain to the Source restricted only by the small depletion region around the junctions.

If a small negative voltage ( -VGS ) is now applied to the Gate the size of the depletion region begins to increase reducing the overall effective area of the channel and thus reducing the current flowing through it, a sort of “squeezing” effect takes place. So by applying a reverse bias voltage increases the width of the depletion region which in turn reduces the conduction of the channel.

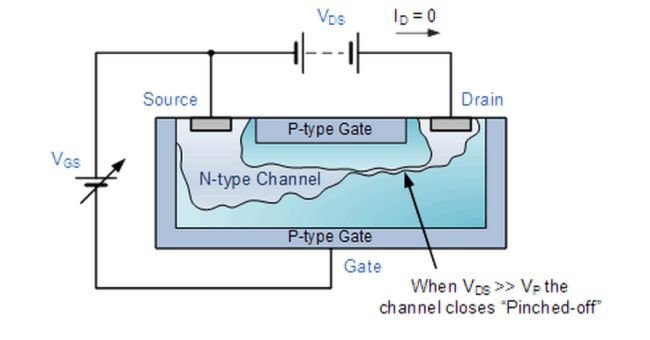

Since the PN-junction is reverse biased, little current will flow into the gate connection. As the Gate voltage ( -VGS ) is made more negative, the width of the channel decreases until no more current flows between the Drain and the Source and the FET is said to be “pinched-off” (similar to the cut-off region for a BJT). The voltage at which the channel closes is called the “pinch-off voltage”, ( VP ).

JFET Channel Pinched-off

In this pinch-off region the Gate voltage, VGS controls the channel current and VDS has little or no effect.

The result is that the FET acts more like a voltage controlled resistor which has zero resistance when VGS = 0 and maximum “ON” resistance ( RDS ) when the Gate voltage is very negative. Under normal operating conditions, the JFET gate is always negatively biased relative to the source.

It is essential that the Gate voltage is never positive since if it is all the channel current will flow to the Gate and not to the Source, the result is damage to the JFET. Then to close the channel:

- No Gate voltage ( VGS ) and VDS is increased from zero.

- No VDS and Gate control is decreased negatively from zero.

- VDS and VGS varying.

The P-channel Junction Field Effect Transistor operates the same as the N-channel above, with the following exceptions: 1). Channel current is positive due to holes, 2). The polarity of the biasing voltage needs to be reversed.

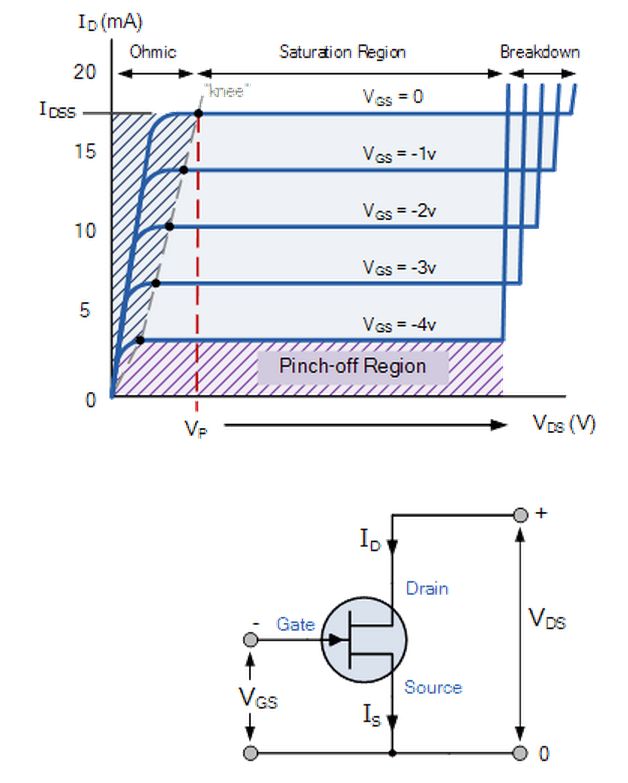

The output characteristics of an N-channel JFET with the gate short-circuited to the source is given as

Output characteristic V-I curves of a typical junction FET.

The voltage VGS applied to the Gate controls the current flowing between the Drain and the Source terminals. VGS refers to the voltage applied between the Gate and the Source while VDS refers to the voltage applied between the Drain and the Source.

Because a Junction Field Effect Transistor is a voltage controlled device, “NO current flows into the gate!” then the Source current ( IS ) flowing out of the device equals the Drain current flowing into it and therefore ( ID = IS ).

The characteristics curves example shown above, shows the four different regions of operation for a JFET and these are given as:

- • Ohmic Region – When VGS = 0 the depletion layer of the channel is very small and the JFET acts like a voltage controlled resistor.

- • Cut-off Region – This is also known as the pinch-off region were the Gate voltage, VGS is sufficient to cause the JFET to act as an open circuit as the channel resistance is at maximum.

- • Saturation or Active Region – The JFET becomes a good conductor and is controlled by the Gate-Source voltage, ( VGS ) while the Drain-Source voltage, ( VDS ) has little or no effect.

- • Breakdown Region – The voltage between the Drain and the Source, ( VDS ) is high enough to causes the JFET’s resistive channel to break down and pass uncontrolled maximum current.

The characteristics curves for a P-channel junction field effect transistor are the same as those above, except that the Drain current ID decreases with an increasing positive Gate-Source voltage,VGS.

The Drain current is zero when VGS = VP. For normal operation, VGS is biased to be somewhere between VP and 0. Then we can calculate the Drain current, ID for any given bias point in the saturation or active region as follows:

Drain current in the active region.

Note that the value of the Drain current will be between zero (pinch-off) and IDSS (maximum current). By knowing the Drain current ID and the Drain-Source voltage VDS the resistance of the channel ( ID ) is given as:

Drain-Source channel resistance.

Where: gm is the “transconductance gain” since the JFET is a voltage controlled device and which represents the rate of change of the Drain current with respect to the change in Gate-Source voltage.

Modes of FET’s

Like the bipolar junction transistor, the field effect transistor being a three terminal device is capable of three distinct modes of operation and can therefore be connected within a circuit in one of the following configurations.

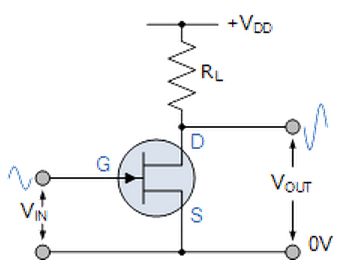

Common Source (CS) Configuration

In the Common Source configuration (similar to common emitter), the input is applied to the Gate and its output is taken from the Drain as shown. This is the most common mode of operation of the FET due to its high input impedance and good voltage amplification and as such Common Source amplifiers are widely used.

The common source mode of FET connection is generally used audio frequency amplifiers and in high input impedance pre-amps and stages. Being an amplifying circuit, the output signal is 180o “out-of-phase” with the input.

Common Gate (CG) Configuration

In the Common Gate configuration (similar to common base), the input is applied to the Source and its output is taken from the Drain with the Gate connected directly to ground (0v) as shown. The high input impedance feature of the previous connection is lost in this configuration as the common gate has a low input impedance, but a high output impedance.

This type of FET configuration can be used in high frequency circuits or in impedance matching circuits were a low input impedance needs to be matched to a high output impedance. The output is “in-phase” with the input.

Common Drain (CD) Configuration

In the Common Drain configuration (similar to common collector), the input is applied to the Gate and its output is taken from the Source. The common drain or “source follower” configuration has a high input impedance and a low output impedance and near-unity voltage gain so is therefore used in buffer amplifiers. The voltage gain of the source follower configuration is less than unity, and the output signal is “in-phase”, 0o with the input signal.

This type of configuration is referred to as “Common Drain” because there is no signal available at the drain connection, the voltage present, +VDD just provides a bias. The output is in-phase with the input.

The JFET Amplifier

Just like the bipolar junction transistor, JFET’s can be used to make single stage class A amplifier circuits with the JFET common source amplifier and characteristics being very similar to the BJT common emitter circuit. The main advantage JFET amplifiers have over BJT amplifiers is their high input impedance which is controlled by the Gate biasing resistive network formed by R1 and R2 as shown.

Biasing of JFET Amplifier

This common source (CS) amplifier circuit is biased in class “A” mode by the voltage divider network formed by resistors R1 and R2. The voltage across the Source resistor RS is generally set to be about one quarter of VDD, ( VDD /4 ). The required Gate voltage can then be calculated using this RS value. Since the Gate current is zero, ( IG = 0 ) we can set the required DC quiescent voltage by the proper selection of resistors R1 and R2.

The control of the Drain current by a negative Gate potential makes the Junction Field Effect Transistor useful as a switch and it is essential that the Gate voltage is never positive for an N-channel JFET as the channel current will flow to the Gate and not the Drain resulting in damage to the JFET. The principals of operation for a P-channel JFET are the same as for the N-channel JFET, except that the polarity of the voltages need to be reversed.

In the next tutorial about Transistors, we will look at another type of Field Effect Transistor called aMOSFET whose Gate connection is completely isolated from the main current carrying channel.

The MOSFET

The MOSFET – Metal Oxide FET

As well as the Junction Field Effect Transistor (JFET), there is another type of Field Effect Transistor available whose Gate input is electrically insulated from the main current carrying channel and is therefore called an Insulated Gate Field Effect Transistor or IGFET. The most common type of insulated gate FET which is used in many different types of electronic circuits is called the Metal Oxide Semiconductor Field Effect Transistor or MOSFETfor short.

The IGFET or MOSFET is a voltage controlled field effect transistor that differs from a JFET in that it has a “Metal Oxide” Gate electrode which is electrically insulated from the main semiconductor n-channel or p-channel by a very thin layer of insulating material usually silicon dioxide, commonly known as glass.

This ultra thin insulated metal gate electrode can be thought of as one plate of a capacitor. The isolation of the controlling Gate makes the input resistance of the MOSFET extremely high way up in the Mega-ohms ( MΩ ) region thereby making it almost infinite.

As the Gate terminal is isolated from the main current carrying channel “NO current flows into the gate” and just like the JFET, the MOSFET also acts like a voltage controlled resistor were the current flowing through the main channel between the Drain and Source is proportional to the input voltage. Also like the JFET, the MOSFETs very high input resistance can easily accumulate large amounts of static charge resulting in the MOSFET becoming easily damaged unless carefully handled or protected.

Like the previous JFET tutorial, MOSFETs are three terminal devices with a Gate, Drain and Sourceand both P-channel (PMOS) and N-channel (NMOS) MOSFETs are available. The main difference this time is that MOSFETs are available in two basic forms:

- 1. Depletion Type – the transistor requires the Gate-Source voltage, ( VGS ) to switch the device “OFF”. The depletion mode MOSFET is equivalent to a “Normally Closed” switch.

- 2. Enhancement Type – the transistor requires a Gate-Source voltage, ( VGS ) to switch the device “ON”. The enhancement mode MOSFET is equivalent to a “Normally Open” switch.

The symbols and basic construction for both configurations of MOSFETs are shown below.

The four MOSFET symbols above show an additional terminal called the Substrate and is not normally used as either an input or an output connection but instead it is used for grounding the substrate. It connects to the main semiconductive channel through a diode junction to the body or metal tab of the MOSFET. Usually in discrete type MOSFETs, this substrate lead is connected internally to the source terminal. When this is the case, as in enhancement types it is omitted from the symbol for clarification.

The line between the drain and source connections represents the semiconductive channel. If this is a solid unbroken line then this represents a “Depletion” (normally-ON) type MOSFET as drain current can flow with zero gate potential. If the channel line is shown dotted or broken it is an “Enhancement” (normally-OFF) type MOSFET as zero drain current flows with zero gate potential. The direction of the arrow indicates whether the conductive channel is a p-type or an n-type semiconductor device.

Basic MOSFET Structure and Symbol

The construction of the Metal Oxide Semiconductor FET is very different to that of the Junction FET. Both the Depletion and Enhancement type MOSFETs use an electrical field produced by a gate voltage to alter the flow of charge carriers, electrons for n-channel or holes for P-channel, through the semiconductive drain-source channel. The gate electrode is placed on top of a very thin insulating layer and there are a pair of small n-type regions just under the drain and source electrodes.