图像采集系统的Camera Link标准接口设计

高速数据采集系统可对相机采集得到的实时图像进行传输、实时处理,同时实现视频采集卡和计算机之间的通信。系统连接相机的接口用的是Camera Link接口,通过Camera Link接口把实时图像高速传输到FPGA图像采集卡中进行数据实时处理,并通过PCI接口实现采集卡和计算机之间的通信。本文主要研究数据采集系统 Cam-era Link接口技术。

Camera Link是专门为数字摄像机的数据传输提出的接口标准,是2000年10月由一些摄像头供应商和图像采集公司联合推出的。Camera Link标准简化了计算机和摄像头之间的连接。本设计选用Dalsa公司的DS-21-02M30相机,该相机支持Camera Link接口。相机数据通过Camera Link接口传输到一块Altera公司的FPGAStratixII中进行处理。在FPGA中进行数据的高速缓存,可以在FPGA中设计各种图像处理程序对图像进行实时处理。

1 DS-21-02M30相机简介

DS-21-02M30相机可提供高灵敏度的8/10位图像。为了同时获得卓越的分辨率和灰度级,DS-21-02M30相机图像分辨率为1 600×1 200,像素尺寸为7.4 μm×7.4 μm,像素数据输出时钟为40 MHz,最高帧频可达60帧/s。通过设定像素数据格式命令,可以设定像素数据为8位、10位。功耗低于15 W,供电电源电压为12~25 V。

通过异步串口向DS-21-02M30相机发送ASCII码控制命令和诊断命令,可以控制相机输出图像的增益、补偿、帧频、曝光时间、曝光模式和测试图像的输出,还可以对相机进行诊断。串口协议:1位开始位,8位数据位,无奇偶校验位,1位停止位;通信波特率为9 600 bps(相机默认),通过设定波特率命令可将其设定为19 200 bps、57 600 bps和115 200 bps。

DS-21-02M30相机共有4种曝光模式,可以通过设定曝光模式命令来为相机选择合适的曝光模式。

模式2:内部触发方式(相机的默认曝光模式)。帧频和曝光时间可用相应的命令控制。

模式3:最大曝光时间的外部触发方式。

模式4:外部触发方式。帧频和曝光时间都由外部触发信号控制,即外部触发信号的高电平阶段为曝光时间,外部触发信号的频率为帧频。

模式6:外部触发方式控制帧频,曝光时间可用相应内部命令控制。

DS-21-02M30相机的命令以ASCII码的形式发

送。向相机发送命令时,以回车符作为结束。相机上电后,相机背后的指示灯闪烁,同时通过串口发送“CameraInitialization in process,Please Wait…OK>”字符串。当收到“OK>”字符串时,表明相机要开始传送图像数据,相机背后的指示灯不再闪烁。当相机收到有效的命令时,会返回“OK>”字符串作为应答;否则,返回“Error x:Error Massage>”字符串作为应答。其中,x为错误标号,Error Massage表示对错误的具体说明。相机的应答字符串以符号“>”作为结束符。

2 Camera Link结构与原理

Camera Link是专门为数字摄像机的数据传输提出的接口标准,专为数字相机制定的一种图像数据、视频数据控制信号及相机控制信号传输的总线接口,数据传输速率最高可达2.38 Gbps。该标准规定了接口模式、相机信号、端口配置、图像数据位配置、连接器引脚定义及连接线、标准接收器芯片组。采用这种标准后,使得数字摄像机的数据接口输出采用更少的线数,连接电缆更容易制造,更具有通用性,而且数据的传输距离比普通传输方式更远。其最主要的特点是采用了LVDS(Low VoltageDifferential Signaling,低压差分信号)技术,使摄像机的数据传输速率大大提高。

在Careera Link标准出现之前,业界有一些标准(如较流行的IEEE-1394:接口)作为一种数据传输的技术标准。IEEE-1394被应用到众多的领域,数字相机、摄像机等数字成像领域也有很广泛的应用。IEEE-1394接口具有廉价,速度快,支持热拔插,数据传输速率可扩展,标准开放等特点。但随着数字图像采集速度的提高、数据量的增大,原有的标准已无法满足需求。为了简化数据的连接,实现高速、高精度、灵活、简单的连接,在 NationalSemiconductor公司开发的Channel Link总线技术基础上,由多家相机制造商共同制定推出了Camera Link标准。基于Camera Link的数字相机的采集速度和数据量均好于基于IEEE-1394标准。

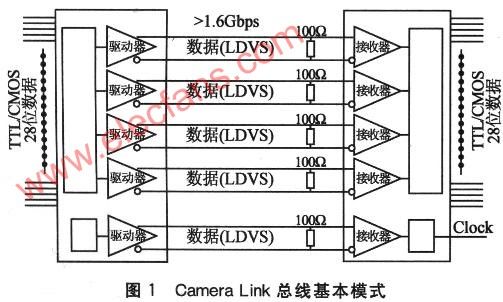

Camera Link是一种基于物理层的LVDS的平面显示解决方案。图1为Camera Link总线发送端与接收端的连接框图,也是该总线的基本模式。总线发送端,将28位并行数据转换为4对LVDS串行差分数据传送出去,还有一对LVDS 串行差分数据线用来传输图像数据输出同步时钟;而总线接收端,将串行差分数据转换成28位并行数据,同时转换出同步时钟。这样不但减少了传输线的使用量,而且由于采用串行差分传输方式,还减少了传输过程中的电磁干扰。

3 高速数据采集卡Camera Link接口设计

高速数据采集系统的基本框图如图2所示。FPGA给相机发出控制信号,相机中的数据通过Careera Link接口传送到图像采集卡;数据由FPGA读入,缓存在SDRAM中。可以在FPGA中根据用户的需求实现高速的图像处理,根据图像处理的结果可以由 FPGA完成用户所需的控制。图像采集卡通过PCI接口和计算机相连接,通过计算机可以配置图像采集卡和相机,计算机也可以从采集卡中获得图像处理数据。接下来详细研究FPGA和相机间的Camera Link接口技术。

3.1 DS-21-02M30相机的Camera Link接口

Camela Link总线标准规定:在完整模式下,最多可以使用8个端口(Port A~Port H)传输数据,每个端口为8位数据。DS-21-02M30相机使用Port A~Port C端口,用的是基本模式(Base)。相机后端有一个MDR26连接口,分别对应A、B、C三个端口各8位数据,加上FVAL、LVAL、DVAL和SP 四位数据控制信号,共28位并行数据位。

3.2 Camera Link接口的硬件设计

Camera Link的硬件连接框图如图3所示。硬件电路包括3部分:相机通过MDR26连接图像采集卡;CameraLink接口的LVDS信号和CMOS信号转换电路;FPGA接收相机数据和发送控制部分。

为了对相机进行外部触发方式控制以及向相机发送命令,用四通道CMOS信号转换为LVDS差分信号的芯,片。DS90LV047作为图像采集卡,向相机发送外同步触发信号和转换命令。由于DS-21-02M30相机只用到CC1,FPGA构成的图像采集卡,对相机的控制通过CC1和SerTC信号实现。为了接收相机向图像处理系统发送的应答字符串,选用DS90LV048芯片作为图像处理系统接收器。 DS90LV048芯片是四通道LVDS差分信号转换为CMOS信号的驱动器。