基于FPGA的UART异步串行通信发送模块设计与实现

下一篇文请点击下列链接(接收模块设计)

[基于FPGA的UART异步串行通信接收模块设计与实现]

本文发送模块:

在电子系统中,需要板内,板间或者下位机与上位机之间进行数据的发送和接受,这就需要双方共同遵循一定的通信协议来保证数据传输的正确性。大家学过单片机,应该知道串口通信的原理,例如,在stm32中,编写UART,可以在上位机PC端利用串口调试助手,通过下位机stm32给PC机发送字符消息,反正也可以,这就是最简单的通信实例。那么在FPGA领域,常见的通信协议有UART(通用异步收发传输器),IIC(集成电路总线),SPI(串行外围总线),USB2.0/3.0(通用串行总线)以及以太网。当然了,最为基础的就是UART,应用很广泛。

那么本文就讲述UART通信的基础原理和它的硬件电路的设计,使用FPGA来实现UART通信(本文只讲解发送部分设计,其他部分后续文章讲述),在quartus ii开发软件中的ISSP工具进行验证。

要实现的功能是:输入需要串口发送的数据,通过开发板上按键,来控制FPGA将要发送的数据发送给PC机,并在PC机上串口助手中查看数据。

异步串行通信原理及电路设计

RS232通信接口标准:

通用异步收发传输器(uart),其在数据发送的过程中将并行的数据转换为串行数据流进行传输,在数据接受的时候将接受到串行数据流转换为并行的数据,可以实现全双工传输接收。

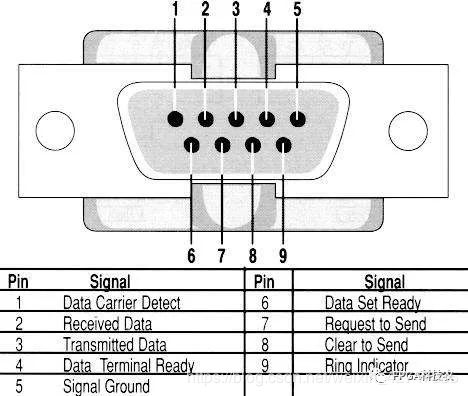

本文的RS232RS-232接口符合美国电子工业联盟(EIA)制定的串行数据通信的接口标准,原始编号全称是EIA-RS-232(简称232,RS232)。它被广泛用于计算机串行接口外设连接。连接电缆和机械、电气特性、信号功能及传送过程。其中的DB9接口定义如下:

UART参数和时序

UART在使用之前,我们需要对其进行初始设置,譬如:设置数据位数,波特率大小,奇偶校验,停止位。

数据位:这个参数定义的是单个UART数据传输在开始到停止期间发送的数据位数。

波特率:这个参数指的是从一个设备发送到另一个设备的波特率(每秒可传输的数据比特个数),一般通信双方要拥有相同的比特率。

奇偶校验类型:用来验证数据的正确性,可以作为奇校验或偶校验,在偶校验里,所有传输的数位(含字符各位数和校验位)中的1为偶数个;在奇校验里,所有传输的数位(含字符各位数和校验位)中的1为奇数个。通过这个特性,可用来接收方检查传输是否出错(1的个数错了,则传输出错),若奇偶校验正确,要不就是没错误,要不就是发生了偶数个错误。

停止位:在每个字节数据位发送完成,就要发送停止位,这就标志着一次的数据传输成功了。

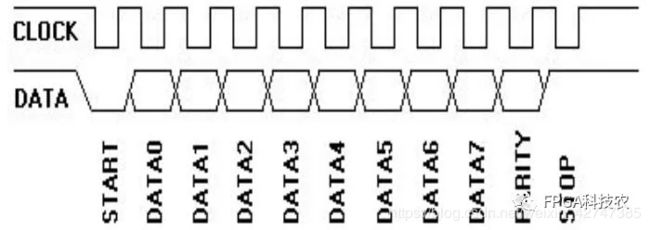

在RS232标准里,最普遍的配置就是8+1(八个数据位,无奇偶校验,一个停止位),一个完整字节包括一个起始位,8个数据为,一个停止位。

CLOCK信号第一个上升沿到来时,字节发送模块开始发送起始位,第10个上升沿到11个为停止位发送。

UART异步串行通信发送模块设计与实现

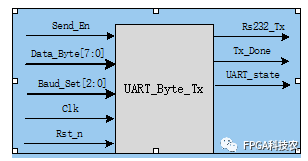

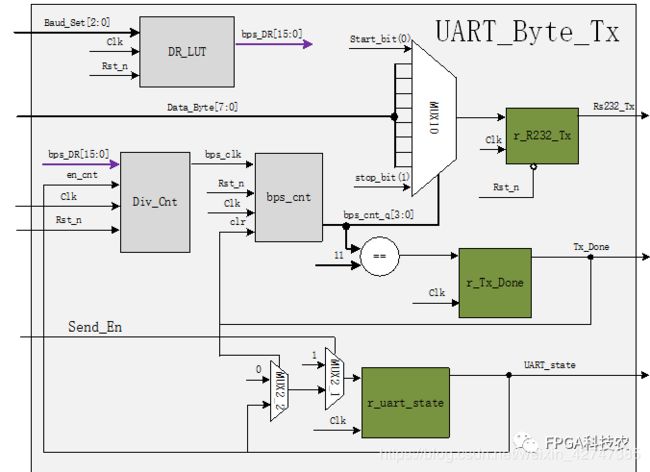

本文要实现的串口发送模块框图

串口发送模块结构图

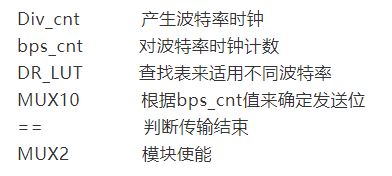

上图中子模块的功能说明

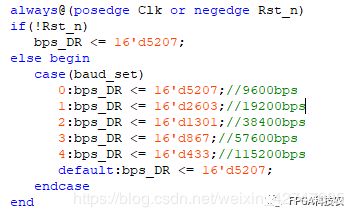

这个模块为了适应不同的波特率,只要修改不同波特率时钟对应计数器的计数值,使用查找表。

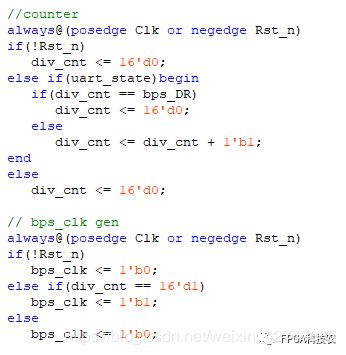

用计数器来产生波特率时钟

波特率产生,就是用一个定时器来计数定时,产生频率与对应波特率时钟频率相同的时钟信号(分频),譬如,115200bps的波特率,我们就需要一个频率为115200hz的时钟信号,可以用计数器来产生。则bps_DR=8680.6ns/20ns - 1.

数据输出模块:

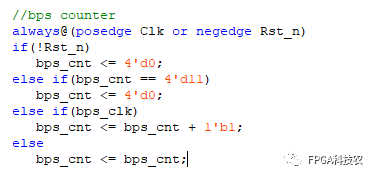

通过对波特率时钟进行计数,确定数据发送状态

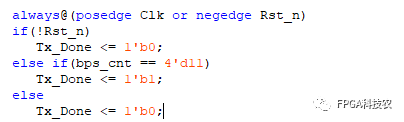

因为此模块需要对其他模块进行调用控制,就需要产生一个字节数据的完成标志信号。即一个数据传输结束,Tx_done输出一个时钟高电平。

产生数据传输状态信号,当正常的传输数据过程中,uart_state为高电平,其余状态下为低电平。

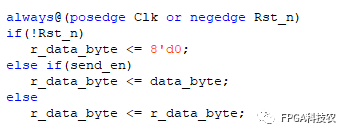

因为RS232是一个异步收发器,为了保证发送的数据在时钟到来时稳定,减少亚稳态的产生,我们需要对输入数据进行寄存,打一拍。

数据传输状态模块:

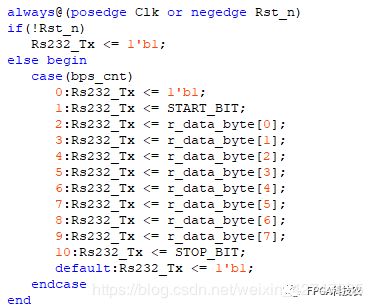

这个模块作用就是根据bps_cnt来确定数据传输的状态,也就是说前文讲述的,一个完整数据由10个位组成,这个模块控制每一位传输的状态。即不同波特率时钟计数值bps_cnt,有不同传输数据位与之对应。

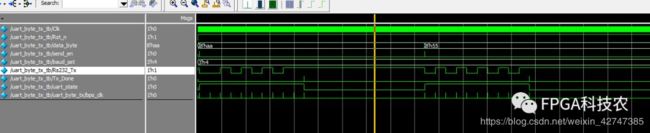

编写testbench文件进行前仿真,得到如下波形,可以看出,当输入数据data_byte为10101010时,输出信号依次是1,0(起始位),01010101,1(停止位);当输入数据为01010101时,输出信号依次为1,0,10101010,1(停止位)

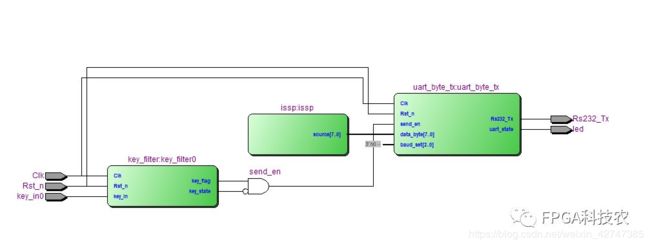

新建一个顶层文件,考虑到本次需要实现的功能,要和按键结合,所以将按键消抖,串口发送和ISSP例化,将按键状态与串口发送使能连接,并将串口发送状态连接到LED上。

最后,通过RTL_viewer观察各模块之间关系。

下一篇文请点击下列链接(接收模块设计)

[基于FPGA的UART异步串行通信接收模块设计与实现]