《EDA技术与Verilog HDL设计》第4、5 章读书笔记与总结

前言:

Verilog HDL是一门硬件设计语言。

硬件描述语言(HDL)是一种用形式化方法描述数字电路和设计数字逻辑系统的语言。

第四章笔记

Verilog HDL的基本设计单元是模块,一个模块由描述接口和描述逻辑功能两部分构成。

Verilog HDL程序由五部分构成:模块声明,端口定义,数据(信号)类型声明,逻辑功能描述,结束模块。

例:与或门电路

module ao(a,b,c,d); //模块名:ao,端口:a,b,c,d

input a,b; //输入端口a,b

output c,d; //输出端口c,d

wire a,b,c,d; //定义数据类型为wire型(线网类型)

assign c=a|b; //逻辑功能描述(连续赋值)

assign d=a&b; //逻辑功能描述(连续赋值)

endmodule //模块结束

注:每个模块实现特定功能,可以进行层次嵌套。

端口说明:input,output,inout(输入输出端口)。

数据类型说明:wire(线网),reg(寄存器),parameter(参数)

逻辑功能定义:assign(连续赋值),always(过程赋值),function(函数),task(任务)

模块中所有信号都应定义数据类型,端口如果没有定义则默认为wire型数据,输入和双向端口不能声明为reg型。

例化的定义:

模块或元件的调用指从元件或模块模板生成实际的电路结构的过程,元件或模板的每一次调用均生成一个单独电路,需要自己的名字、变量、参数及I/O口,因此也称为例化。

例化过程:

and a1(se_a,a,se)

and a2(se_b,b,se_n)

一般Verilog HDL模块程序的模板如下:

module <顶层模块名>(<输入/输出端口列表>);

output 输出端口列表; //输出端口声明

input 输入端口列表; //输入端口声明

/*定义数据,信号的类型,函数声明*/

wire 信号名

reg 信号名

//逻辑功能定义

assign <结果信号名>=<表达式>; //使用assign语句定义逻辑功能

//用always块描述逻辑功能

always@(<敏感信号表达式>)

begin

//过程赋值

//if-else,case语句

//while,repeat,for循环语句

//task,function调用

end

//调用其他模板

<调用模块名module_name><例化模块名>(<端口列表port_list>);

//门元件例化

门元件关键字<例化门元件名>(<端口列表port_list>);

endmodule

Verilog HDL能够在不同层级对数字系统进行描述,根据描述的抽象级别分为:系统级,算法级,寄存器传输级,门级,开关级。

门级描述指用逻辑门来描述数字电路,开关级描述指用晶体管进行电路描述。

利用Verilog HDL描述数字逻辑电路的方式有以下三种:行为描述,数据流描述,结构描述。行为描述通过对电路的行为特性的描述设计电路,多用always;数据流描述是通过连续赋值语句描述电路,结构描述是通过调用已有电路来构建新的电路。

Verilog HDL的空白符包括:空格,Tab,换行符,换页符。

Verilog HDL的注释有两种:单行注释,以//开始;多行注释,以/开始,/结束。Verilog HDL的标识符必须由字母或下划线开头,后续可以是字母、数字、下划线、$等,也可以是以\开头,以空白符结尾的任何字符排列,例{a,b},~(a+b);(区分大小写)

注:反斜杠本身和空白符都不属于标识符部分,也称为转义字符。Verilog HDL的关键字均是小写。

Verilog HDL的四种逻辑状态:

| 0 | 逻辑非,逻辑零,低电平 |

|---|---|

| 1 | 逻辑真,逻辑1,高电平 |

| x/X | 逻辑不定态 |

| z/Z/? | 高阻态 |

不定态和高阻态不区分大小,通常使用小写。

Verilog HDL的整数可以表示成二进制(b或B),八进制(o或O),十进制(d或D或默认),十六进制(h或H)。

表达方法如下:+/-<位宽(size)>’<进制(base)><数值(value)>

8’ha7 //位宽为8的十六进制数a7(二进制10100111)

4’b10x0 //位宽为4的二进制数10x0

Verilog HDL数据类型:wire是线网类型,reg是寄存器数据类型。

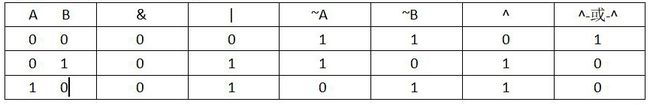

运算符:~(按位取反运算)、&(按位与运算)、|(按位或运算)、(按位异或运算)、-或者-^(按位同或运算)

按位逻辑运算真值表(部分)

例:A=4’b1010,B=4’b0110

~A=4’b0101

~B=4’b1001

A&B=4’b0010

A|B=4’b1110

A^B=4’b1100

A^-B=4’b0011

在进行关系运算后,若关系成立,则返回结果为真或“1”,若不成立,则为假或“0”,如果比较的双方只要有一个不确定,则返回的结果为不确定或“x”.

第五章笔记

Verilog HDL的描述方法包括:行为描述、结构描述和数据流描述。行为描述中,有多个过程描述体,过程语句与块语句构成每个描述体,而过程赋值语句和其他程序语句构成块语句。过程描述体结构:

过程语句@(控制事件敏感表)

块语句开始标识:块名

块内部变量说明

过程赋值语句或其他程序语句

块语句结束标识

过程语句包括:always语句、initial语句,“@控制事件敏感表”只用于always语句。块语句、结束标识包括:串行方式的begin-end,并行方式的fork-join。

always语句:当敏感事件表或表达式中的变量发生改变时,其后的块语句begin-end会被执行一次,也可省略敏感事件或表达式,此时其后的块语句将始终被执行;过程语句中要列出全部的敏感信号;“posedge”表示上升沿,“negedge”表示下降沿。

initial过程语句:常用于测试模块中对激励进行描述,主要用于测试、给寄存器变量赋初值和仿真模拟,一般不能综合;只被执行一次。

赋值语句:阻塞赋值符号为“=”,非阻塞赋值符号为“<=”。用过程语句设计时序逻辑电路优先选用非阻塞赋值;用always过程语句设计组合电路时可使用阻塞或非阻塞赋值,优先选阻塞赋值;不能在两个及以上always过程语句中对同一个变量赋值。

一般过程赋值语句的基本形式为:<寄存器变量>=/<=<表达式>

外部模式:<定时控制><寄存器变量>=/<=<表达式>

内部模式:<寄存器变量>=/<=<定时控制><表达式>

条件语句:if-else有优先级,优先级从上到下;case无优先级;使用if语句,要添上else项;使用case语句,要添上default项。

循环语句:

forever—连续执行语句;

repeat—连续执行一条/组语句n次;

while—执行一条语句直到某个条件不满足,如果 条件一开始就不满足,则语句一次也不会执行;for—通过循环控制变量控制语句的循环执行;

总结:

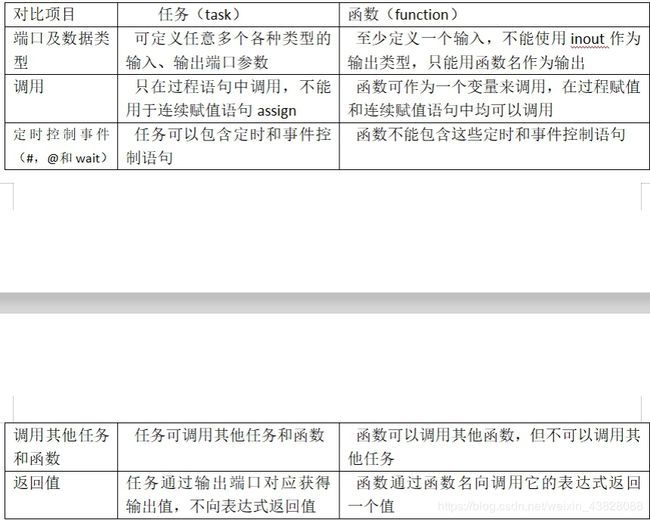

任务能启动其他任务和函数,而函数不能启动任务。

任务可以没有变量,也可以有多个不同类型的变量,而函数至少需要一个变量。

任务可以定义自己的仿真时间单位,而函数只能与主模块共有同一个仿真事件单位。

任务不返回值,而函数会返回一个值。

注意:

任务调用的端口变量应和任务定义的端口变量之间一一对应,任务定义与调用必须在同一个模块内;由于任务在模块内,因此没有端口列表。

函数定义与调用也要在同一个模块内;由于在模块内,所以没有端口列表,没有输出端口,函数名就是输出变量,输出变量必须与函数的定义顺序一致,函数可以在持续赋值assign语句中使用。

任务调用形式:<任务名>(端口1,端口2,…,端口n);

函数调用格式:<函数名>(<表达式><表达式>);

编译指示语句:对程序进行预处理的控制语句,以’开头。

include语句基本格式:’include “文件名”,例如:’include “mux.v”

注意:每条’include语句只能用于包含一个文件,有多个文件需使用多个’include语句;文件形式允许嵌套;多用于仿真器中。

语句’define基本格式:’define 标识符 字符串

总结:

Verilog HDL编程中结构和语句与C语言相似,个别有差异。比如C语言中{,}而Verilog HDL用begin,end表示。

连续赋值与过程赋值的区别:

连续赋值:类似于线网类型,只要表达式一变化,变化结果马上赋给对象。

过程赋值:类似于寄存器类型。