基于FPGA的光纤数据传输

基于FPGA的光纤数据传输

- 项目简述

- Aurora 8B10B的调用

- Aurora 8B10B接口的描述

- 光纤项目的代码设计

- MZ7015开发板工程

- MZ7015开发板测试代码

- MA7035FA开发板代码

- 仿真结果

- 下板结果

- 总结

项目简述

在这次的实验中我们主要学习SFP接口的使用,该接口是高速接口主要是使用GTP接口来完成的。本次项目的简述为,一块FPGA开发板通过光纤发送递增数据,另一块FPGA开发板通过光纤接收数据并且验证数据的正确性。本次实验所用到的软硬件环境如下:

1、VIVIADO 2019.1软件开发环境

2、米联客MA7035FA开发板

3、米联客MZ7015开发板

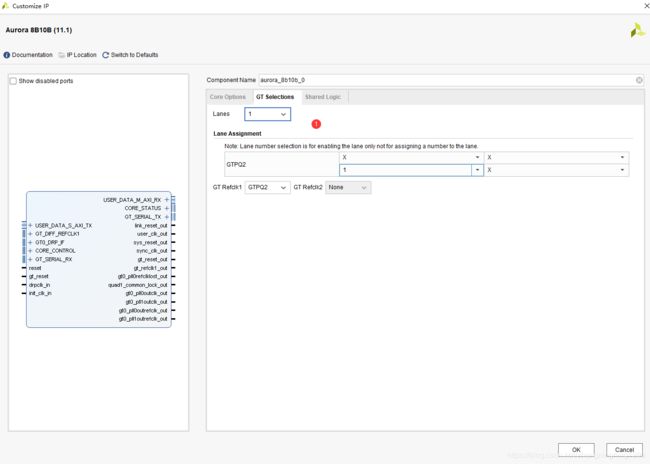

Aurora 8B10B的调用

我们接下来将对Aurora 8B10B IP进行讲解

1、传输数据的位宽,这里选择4Byte,也就是说IP的用户接口数据为32位宽

2、GTP接口的串行传输速率,GTP几口最大传输6.25Gbps,这里我们直接选择最大速率传输

3、Aurora 8B10B IP的GTP底层接口时钟,这个与FPGA开发板的GTP时钟有关,我使用的这两款开发板都是125MHz,所以我们这里选择125MHz

4、Aurora 8B10B IP的初始化时钟,我们选择50MHz

5、DRP时钟,我们在程序中没有用到DRP有关的操作,这里也给成50MHz

6、选择该Aurora 8B10B IP的通信模式,这里选择双工通信

7、数据传输的用户接口,我们这里使用简单的AXI4-stream数据接口

8、这里我们的数据使用小端模式。

大端模式,是指数据的高字节保存在内存的低地址中,而数据的低字节保存在内存的高地址中,这样的存储模式有点儿类似于把数据当作字符串顺序处理:地址由小向大增加,而数据从高位往低位放;这和我们的阅读习惯一致。

小端模式,是指数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中,这种存储模式将地址的高低和数据位权有效地结合起来,高地址部分权值高,低地址部分权值低。

1、这个按照GTP口的顺序进行选择,该款FPGA一共4对GTP接口,从左下角逆时针循环时0,1,2,3。具体选择哪一个看FPGA开发板上面的GTP接口使用的第几对。

1、这里我们只使用1个IP核,不使用示例工程,所以我们选择第一个

2、我们这个IP核的初始化时钟是单端信号,参考时钟是双端时钟,进行相应的选择。

Aurora 8B10B接口的描述

接下来我们对我们使用的Aurora 8B10B接口进行简单的描述。

aurora_8b10b_0 your_instance_name (

.s_axi_tx_tdata (s_axi_tx_tdata ), // input wire [31 : 0] s_axi_tx_tdata

.s_axi_tx_tvalid (s_axi_tx_tvalid ), // input wire s_axi_tx_tvalid

.s_axi_tx_tready (s_axi_tx_tready ), // output wire s_axi_tx_tready

.m_axi_rx_tdata (m_axi_rx_tdata ), // output wire [31 : 0] m_axi_rx_tdata

.m_axi_rx_tvalid (m_axi_rx_tvalid ), // output wire m_axi_rx_tvalid

.hard_err (hard_err ), // output wire hard_err

.soft_err (soft_err ), // output wire soft_err

.channel_up (channel_up ), // output wire channel_up

.lane_up (lane_up ), // output wire [0 : 0] lane_up

.txp (txp ), // output wire [0 : 0] txp

.txn (txn ), // output wire [0 : 0] txn

.reset (reset ), // input wire reset

.gt_reset (gt_reset ), // input wire gt_reset

.loopback (loopback ), // input wire [2 : 0] loopback

.rxp (rxp ), // input wire [0 : 0] rxp

.rxn (rxn ), // input wire [0 : 0] rxn

.drpclk_in (drpclk_in ), // input wire drpclk_in

.drpaddr_in (drpaddr_in ),// input wire [8 : 0] drpaddr_in

.drpen_in (drpen_in ), // input wire drpen_in

.drpdi_in (drpdi_in ), // input wire [15 : 0] drpdi_in

.drprdy_out (drprdy_out ),// output wire drprdy_out

.drpdo_out (drpdo_out ), // output wire [15 : 0] drpdo_out

.drpwe_in (drpwe_in ), // input wire drpwe_in

.power_down (power_down ),// input wire power_down

.tx_lock (tx_lock ), // output wire tx_lock

.tx_resetdone_out (tx_resetdone_out ), // output wire tx_resetdone_out

.rx_resetdone_out (rx_resetdone_out ), // output wire rx_resetdone_out

.link_reset_out (link_reset_out ), // output wire link_reset_out

.init_clk_in (init_clk_in ), // input wire init_clk_in

.user_clk_out (user_clk_out ), // output wire user_clk_out

.pll_not_locked_out (pll_not_locked_out ), // output wire pll_not_locked_out

.sys_reset_out (sys_reset_out ), // output wire sys_reset_out

.gt_refclk1_p (gt_refclk1_p ), // input wire gt_refclk1_p

.gt_refclk1_n (gt_refclk1_n ), // input wire gt_refclk1_n

.sync_clk_out (sync_clk_out ), // output wire sync_clk_out

.gt_reset_out (gt_reset_out ), // output wire gt_reset_out

.gt_refclk1_out (gt_refclk1_out ), // output wire gt_refclk1_out

.gt0_pll0refclklost_out (gt0_pll0refclklost_out ), // output wire gt0_pll0refclklost_out

.quad1_common_lock_out (quad1_common_lock_out ), // output wire quad1_common_lock_out

.gt0_pll0outclk_out (gt0_pll0outclk_out ), // output wire gt0_pll0outclk_out

.gt0_pll1outclk_out (gt0_pll1outclk_out ), // output wire gt0_pll1outclk_out

.gt0_pll0outrefclk_out (gt0_pll0outrefclk_out ), // output wire gt0_pll0outrefclk_out

.gt0_pll1outrefclk_out (gt0_pll1outrefclk_out ) // output wire gt0_pll1outrefclk_out

);

1、s_axi_tx_tdata、s_axi_tx_tvalid、s_axi_tx_tready、m_axi_rx_tdata、

m_axi_rx_tvalid信号:AXI4-stream协议的信号,具体的时序要求可以查找一下该协议特别容易理解,如果同学们对这个协议不熟悉,一定要学完这个协议继续学习。

2、hard_err 、soft_err信号:Aurora 8B10B IP硬件、软件出错的提示信号。

3、channel_up 、lane_up信号:两个Aurora 8B10B IP的初始化完成信号,只有将两个信号拉高之后,我们才可以进行进一步的操作。

4、txp、txn信号:GTP的写差分接口,也就是我们绑引脚的接口。

5、reset、gt_reset信号:分别是Aurora 8B10B IP与GTP接口的复位信号,高有效,通常先复位reset再复位gt_reset,高电平复位。这里需要注意的是Aurora 8B10B IP在正常使用前一定要复位一段时间。

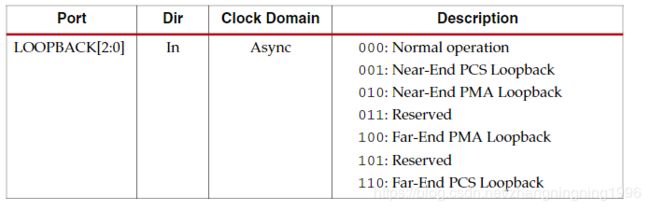

6、loopback信号:环回[2:0]端口在收发机的正常工作和不同的环回模式之间进行选择,这里我们默认为 0。

7、rxp、rxn信号: GTP的读差分接口,也是我们绑引脚的接口。

8、drpclk_in、drpaddr_in、drpen_in、drpdi_in、drprdy_out、drpdo_out、drpwe_in信号:DRP相关信号,与资源分配相关一般用不到,时钟连接定制IP时选择的50MHz时钟,其余的信号输入写0输出忽视即可。

9、power_down信号:掉电信号,1表示IP掉电,正常工作的情况下该位是0信号。

10、init_clk_in信号:Aurora 8B10B IP的初始化时钟信号。

11、user_clk_out信号:用户操作的时钟信号也就是前面AXI4-stream信号的时钟信号,所有的数据操作都是在这个时钟域里面完成的。

其余的输出我们这里用不到也就不进行详细的详解,感兴趣的同学可以查阅技术手册。

光纤项目的代码设计

MZ7015开发板工程

gtp_top模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : gtp_top.v

// Create Time : 2019-12-01 14:20:41

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module gtp_top(

input GTPQ0_P ,

input GTPQ0_N ,

output wire txp ,

output wire txn ,

input rxp ,

input rxn ,

input sclk ,

output wire sfp_tx_disable

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [31:0] s_axi_tx_tdata ;

reg s_axi_tx_tvalid ;

wire s_axi_tx_tready ;

wire [31:0] m_axi_rx_tdata ;

wire m_axi_rx_tvalid ;

wire hard_err ;

wire soft_err ;

wire channel_up ;

wire lane_up ;

reg reset ;

reg gt_reset ;

wire [ 3:0] loopback ;

wire drpclk_in ;

wire [ 8:0] drpaddr_in ;

wire drpen_in ;

wire [15:0] drpdi_in ;

wire drprdy_out ;

wire [15:0] drpdo_out ;

wire drpwe_in ;

wire power_down ;

wire tx_lock ;

wire tx_resetdone_out ;

wire rx_resetdone_out ;

wire link_reset_out ;

wire init_clk_in ;

wire user_clk_out ;

wire pll_not_locked_out ;

wire sys_reset_out ;

wire sync_clk_out ;

wire gt_reset_out ;

wire gt_refclk1_out ;

wire gt0_pll0refclklost_out;

wire quad1_common_lock_out;

wire gt0_pll0outclk_out ;

wire gt0_pll1outclk_out ;

wire gt0_pll0outrefclk_out;

wire gt0_pll1outrefclk_out;

wire locked ;

reg [10:0] gt_reset_cnt ;

reg start_flag ;

reg [31:0] data_cnt ;

reg [11:0] err_cnt ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign drpaddr_in = 9'b000;

assign drpen_in = 1'b0;

assign drpdi_in = 16'd0;

assign drpwe_in = 1'b0;

assign loopback = 3'b000;

assign power_down = ~locked;

assign sfp_tx_disable = 1'b0;

always @(posedge init_clk_in or negedge locked)

if(locked == 1'b0)

gt_reset <= 1'b0;

else if(gt_reset_cnt >= 'd500)

gt_reset <= 1'b0;

else if(gt_reset_cnt == 'd100)

gt_reset <= 1'b1;

always @(posedge init_clk_in or negedge locked)

if(locked == 1'b0)

gt_reset_cnt <= 11'd0;

else if(gt_reset_cnt[10] == 1'b1)

gt_reset_cnt <= gt_reset_cnt;

else

gt_reset_cnt <= gt_reset_cnt + 1'b1;

always @(posedge init_clk_in or negedge locked)

if(locked == 1'b0)

reset <= 1'b1;

else if(gt_reset_cnt >= 'd200)

reset <= 1'b0;

else

reset <= 1'b1;

always @(posedge user_clk_out or negedge locked)

if(locked == 1'b0)

start_flag <= 1'b0;

else if(channel_up==1'b1 && lane_up==1'b1)

start_flag <= 1'b1;

else

start_flag <= 1'b0;

always @(posedge user_clk_out or negedge locked)

if(locked == 1'b0)

s_axi_tx_tdata <= 32'd0;

else if(s_axi_tx_tvalid==1'b1 && s_axi_tx_tready==1'b1 && start_flag==1'b1)

s_axi_tx_tdata <= s_axi_tx_tdata + 1'b1;

else

s_axi_tx_tdata <= s_axi_tx_tdata;

always @(posedge user_clk_out or negedge locked)

if(locked == 1'b0)

s_axi_tx_tvalid <= 1'b0;

else if(start_flag==1'b1)

s_axi_tx_tvalid <= 1'b1;

else

s_axi_tx_tvalid <= 1'b0;

always @(posedge user_clk_out or negedge locked)

if(locked == 1'b0)

data_cnt <= 'd0;

else if(m_axi_rx_tvalid == 1'b1)

data_cnt <= data_cnt + 1'b1;

always @(posedge user_clk_out or negedge locked)

if(locked == 1'b0)

err_cnt <= 'd0;

else if(m_axi_rx_tvalid==1'b1 && data_cnt!=m_axi_rx_tdata)

err_cnt <= err_cnt + 1'b1;

clk_wiz_0 clk_wiz_0_inst(

// Clock out ports

.clk_out1 (drpclk_in ),

.clk_out2 (init_clk_in ),

.locked (locked ),

.clk_in1 (sclk )

);

aurora_8b10b_0 aurora_8b10b_0_inst (

.s_axi_tx_tdata (s_axi_tx_tdata ), // input wire [0 : 31] s_axi_tx_tdata

.s_axi_tx_tvalid (s_axi_tx_tvalid ), // input wire s_axi_tx_tvalid

.s_axi_tx_tready (s_axi_tx_tready ), // output wire s_axi_tx_tready

.m_axi_rx_tdata (m_axi_rx_tdata ), // output wire [0 : 31] m_axi_rx_tdata

.m_axi_rx_tvalid (m_axi_rx_tvalid ), // output wire m_axi_rx_tvalid

.hard_err (hard_err ), // output wire hard_err

.soft_err (soft_err ), // output wire soft_err

.channel_up (channel_up ), // output wire channel_up

.lane_up (lane_up ), // output wire [0 : 0] lane_up

.txp (txp ), // output wire [0 : 0] txp

.txn (txn ), // output wire [0 : 0] txn

.reset (reset ), // input wire reset

.gt_reset (gt_reset ), // input wire gt_reset

.loopback (loopback ), // input wire [2 : 0] loopback

.rxp (rxp ), // input wire [0 : 0] rxp

.rxn (rxn ), // input wire [0 : 0] rxn

.drpclk_in (drpclk_in ), // input wire drpclk_in

.drpaddr_in (drpaddr_in ), // input wire [8 : 0] drpaddr_in

.drpen_in (drpen_in ), // input wire drpen_in

.drpdi_in (drpdi_in ), // input wire [15 : 0] drpdi_in

.drprdy_out (drprdy_out ), // output wire drprdy_out

.drpdo_out (drpdo_out ), // output wire [15 : 0] drpdo_out

.drpwe_in (drpwe_in ), // input wire drpwe_in

.power_down (power_down ), // input wire power_down

.tx_lock (tx_lock ), // output wire tx_lock

.tx_resetdone_out (tx_resetdone_out ), // output wire tx_resetdone_out

.rx_resetdone_out (rx_resetdone_out ), // output wire rx_resetdone_out

.link_reset_out (link_reset_out ), // output wire link_reset_out

.init_clk_in (init_clk_in ), // input wire init_clk_in

.user_clk_out (user_clk_out ), // output wire user_clk_out

.pll_not_locked_out (pll_not_locked_out ), // output wire pll_not_locked_out

.sys_reset_out (sys_reset_out ), // output wire sys_reset_out

.gt_refclk1_p (GTPQ0_P ), // input wire gt_refclk1_p

.gt_refclk1_n (GTPQ0_N ), // input wire gt_refclk1_n

.sync_clk_out (sync_clk_out ), // output wire sync_clk_out

.gt_reset_out (gt_reset_out ), // output wire gt_reset_out

.gt_refclk1_out (gt_refclk1_out ), // output wire gt_refclk1_out

.gt0_pll0refclklost_out (gt0_pll0refclklost_out ), // output wire gt0_pll0refclklost_out

.quad1_common_lock_out (quad1_common_lock_out ), // output wire quad1_common_lock_out

.gt0_pll0outclk_out (gt0_pll0outclk_out ), // output wire gt0_pll0outclk_out

.gt0_pll1outclk_out (gt0_pll1outclk_out ), // output wire gt0_pll1outclk_out

.gt0_pll0outrefclk_out (gt0_pll0outrefclk_out ), // output wire gt0_pll0outrefclk_out

.gt0_pll1outrefclk_out (gt0_pll1outrefclk_out ) // output wire gt0_pll1outrefclk_out

);

//========================================================================================\

//******************************* Debug **********************************

//========================================================================================/

ila_0 ila_0_inst (

.clk (user_clk_out ), // input wire clk

.probe0 (s_axi_tx_tdata ), // input wire [31:0] probe0

.probe1 (s_axi_tx_tvalid ), // input wire [0:0] probe1

.probe2 (s_axi_tx_tready ), // input wire [0:0] probe2

.probe3 (m_axi_rx_tdata ), // input wire [31:0] probe3

.probe4 (m_axi_rx_tvalid ), // input wire [0:0] probe4

.probe5 (channel_up ), // input wire [0:0] probe5

.probe6 (lane_up ), // input wire [0:0] probe6

.probe7 (data_cnt ), // input wire [0:0] probe5

.probe8 (err_cnt ) // input wire [0:0] probe6

);

endmodule

上面的代码并不复杂,只需要详细的读一下具体的代码,相信大家可以学会这个接口的使用,因为我们在程序中主要利用了aurora_8b10b IP核,大大减少了设计的复杂度。但是需要注意的是,我们定制IP与前面我们介绍的有所出入,因为具体的开发板的不同

MZ7015开发板测试代码

测试代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2019/11/30 20:11:24

// Design Name:

// Module Name: gtp_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module gtp_tb;

wire GTPQ0_P ;

wire GTPQ0_N ;

reg sclk ;

reg GTPQ ;

wire txp ;

wire txn ;

wire rxp ;

wire rxn ;

initial begin

sclk = 1'b0;

GTPQ = 1'b0;

end

always #5 sclk = ~sclk;

always #4 GTPQ = ~GTPQ;

assign rxp = txp;

assign rxn = txn;

OBUFDS #(

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFDS_inst (

.O(GTPQ0_P), // Diff_p output (connect directly to top-level port)

.OB(GTPQ0_N), // Diff_n output (connect directly to top-level port)

.I(GTPQ) // Buffer input

);

gtp_top gtp_top_inst(

.GTPQ0_P (GTPQ0_P ),

.GTPQ0_N (GTPQ0_N ),

.txp (txp ),

.txn (txn ),

.rxp (rxp ),

.rxn (rxn ),

.sclk (sclk )

);

endmodule

/*

module gtp_tb();

reg clk_m;//50Mhz

reg gtq0;

wire gtq0_n,gtq0_p;

wire txp,txn,rxn,rxp;

initial begin

clk_m = 0;

gtq0 =0;

end

always #5 clk_m = ~clk_m;

always #4 gtq0 = ~gtq0;

OBUFDS #(

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFDS_inst (

.O(gtq0_p), // Diff_p output (connect directly to top-level port)

.OB(gtq0_n), // Diff_n output (connect directly to top-level port)

.I(gtq0) // Buffer input

);

assign rxp=txp;

assign rxn=txn;

gtp_top top_aurora_inst(

.GTPQ0_N (gtq0_n),

.GTPQ0_P (gtq0_p),

.txp (txp),

.txn (txn),

.rxp (rxp),

.rxn (rxn),

.sclk (clk_m)

);

endmodule

*/

MA7035FA开发板代码

该工程的主要代码如下:

gtp_top模块

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : gtp_top.v

// Create Time : 2019-12-01 14:20:31

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module gtp_top(

input GTPQ0_P ,

input GTPQ0_N ,

output wire txp ,

output wire txn ,

input rxp ,

input rxn ,

input sclk ,

output wire sfp_tx_disable

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

wire [31:0] s_axi_tx_tdata ;

reg s_axi_tx_tvalid ;

wire s_axi_tx_tready ;

wire [31:0] m_axi_rx_tdata ;

wire m_axi_rx_tvalid ;

wire hard_err ;

wire soft_err ;

wire channel_up ;

wire lane_up ;

reg reset ;

reg gt_reset ;

wire [ 3:0] loopback ;

wire drpclk_in ;

wire [ 8:0] drpaddr_in ;

wire drpen_in ;

wire [15:0] drpdi_in ;

wire drprdy_out ;

wire [15:0] drpdo_out ;

wire drpwe_in ;

wire power_down ;

wire tx_lock ;

wire tx_resetdone_out ;

wire rx_resetdone_out ;

wire link_reset_out ;

wire init_clk_in ;

wire user_clk_out ;

wire pll_not_locked_out ;

wire sys_reset_out ;

wire sync_clk_out ;

wire gt_reset_out ;

wire gt_refclk1_out ;

wire gt0_pll0refclklost_out;

wire quad1_common_lock_out;

wire gt0_pll0outclk_out ;

wire gt0_pll1outclk_out ;

wire gt0_pll0outrefclk_out;

wire gt0_pll1outrefclk_out;

wire locked ;

reg [10:0] gt_reset_cnt ;

reg start_flag ;

wire [11:0] data_count ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign drpaddr_in = 9'b000;

assign drpen_in = 1'b0;

assign drpdi_in = 16'd0;

assign drpwe_in = 1'b0;

assign loopback = 3'b000;

assign power_down = ~locked;

assign sfp_tx_disable = 1'b0;

always @(posedge init_clk_in or negedge locked)

if(locked == 1'b0)

gt_reset <= 1'b0;

else if(gt_reset_cnt >= 'd500)

gt_reset <= 1'b0;

else if(gt_reset_cnt == 'd100)

gt_reset <= 1'b1;

always @(posedge init_clk_in or negedge locked)

if(locked == 1'b0)

gt_reset_cnt <= 11'd0;

else if(gt_reset_cnt[10] == 1'b1)

gt_reset_cnt <= gt_reset_cnt;

else

gt_reset_cnt <= gt_reset_cnt + 1'b1;

always @(posedge init_clk_in or negedge locked)

if(locked == 1'b0)

reset <= 1'b1;

else if(gt_reset_cnt >= 'd200)

reset <= 1'b0;

else

reset <= 1'b1;

always @(posedge user_clk_out or negedge locked)

if(locked == 1'b0)

start_flag <= 1'b0;

else if(channel_up==1'b1 && lane_up==1'b1)

start_flag <= 1'b1;

else

start_flag <= 1'b0;

always @(posedge user_clk_out or negedge locked)

if(locked == 1'b0)

s_axi_tx_tvalid <= 1'b0;

else if(data_count >= 'd500)

s_axi_tx_tvalid <= 1'b1;

else if(data_count <= 'd10)

s_axi_tx_tvalid <= 1'b0;

else

s_axi_tx_tvalid <= s_axi_tx_tvalid;

fifo_generator_0 fifo_generator_0_inst (

.clk (user_clk_out ), // input wire clk

.srst (~locked ), // input wire srst

.din (m_axi_rx_tdata ), // input wire [31 : 0] din

.wr_en (m_axi_rx_tvalid ), // input wire wr_en

.rd_en (s_axi_tx_tvalid && s_axi_tx_tready), // input wire rd_en

.dout (s_axi_tx_tdata ), // output wire [31 : 0] dout

.full ( ), // output wire full

.empty ( ), // output wire empty

.data_count (data_count ) // output wire [11 : 0] data_count

);

clk_wiz_0 clk_wiz_0_inst(

// Clock out ports

.clk_out1 (drpclk_in ),

.clk_out2 (init_clk_in ),

.locked (locked ),

.clk_in1 (sclk )

);

aurora_8b10b_0 aurora_8b10b_0_inst (

.s_axi_tx_tdata (s_axi_tx_tdata ), // input wire [0 : 31] s_axi_tx_tdata

.s_axi_tx_tvalid (s_axi_tx_tvalid ), // input wire s_axi_tx_tvalid

.s_axi_tx_tready (s_axi_tx_tready ), // output wire s_axi_tx_tready

.m_axi_rx_tdata (m_axi_rx_tdata ), // output wire [0 : 31] m_axi_rx_tdata

.m_axi_rx_tvalid (m_axi_rx_tvalid ), // output wire m_axi_rx_tvalid

.hard_err (hard_err ), // output wire hard_err

.soft_err (soft_err ), // output wire soft_err

.channel_up (channel_up ), // output wire channel_up

.lane_up (lane_up ), // output wire [0 : 0] lane_up

.txp (txp ), // output wire [0 : 0] txp

.txn (txn ), // output wire [0 : 0] txn

.reset (reset ), // input wire reset

.gt_reset (gt_reset ), // input wire gt_reset

.loopback (loopback ), // input wire [2 : 0] loopback

.rxp (rxp ), // input wire [0 : 0] rxp

.rxn (rxn ), // input wire [0 : 0] rxn

.drpclk_in (drpclk_in ), // input wire drpclk_in

.drpaddr_in (drpaddr_in ), // input wire [8 : 0] drpaddr_in

.drpen_in (drpen_in ), // input wire drpen_in

.drpdi_in (drpdi_in ), // input wire [15 : 0] drpdi_in

.drprdy_out (drprdy_out ), // output wire drprdy_out

.drpdo_out (drpdo_out ), // output wire [15 : 0] drpdo_out

.drpwe_in (drpwe_in ), // input wire drpwe_in

.power_down (power_down ), // input wire power_down

.tx_lock (tx_lock ), // output wire tx_lock

.tx_resetdone_out (tx_resetdone_out ), // output wire tx_resetdone_out

.rx_resetdone_out (rx_resetdone_out ), // output wire rx_resetdone_out

.link_reset_out (link_reset_out ), // output wire link_reset_out

.init_clk_in (init_clk_in ), // input wire init_clk_in

.user_clk_out (user_clk_out ), // output wire user_clk_out

.pll_not_locked_out (pll_not_locked_out ), // output wire pll_not_locked_out

.sys_reset_out (sys_reset_out ), // output wire sys_reset_out

.gt_refclk1_p (GTPQ0_P ), // input wire gt_refclk1_p

.gt_refclk1_n (GTPQ0_N ), // input wire gt_refclk1_n

.sync_clk_out (sync_clk_out ), // output wire sync_clk_out

.gt_reset_out (gt_reset_out ), // output wire gt_reset_out

.gt_refclk1_out (gt_refclk1_out ), // output wire gt_refclk1_out

.gt0_pll0refclklost_out (gt0_pll0refclklost_out ), // output wire gt0_pll0refclklost_out

.quad1_common_lock_out (quad1_common_lock_out ), // output wire quad1_common_lock_out

.gt0_pll0outclk_out (gt0_pll0outclk_out ), // output wire gt0_pll0outclk_out

.gt0_pll1outclk_out (gt0_pll1outclk_out ), // output wire gt0_pll1outclk_out

.gt0_pll0outrefclk_out (gt0_pll0outrefclk_out ), // output wire gt0_pll0outrefclk_out

.gt0_pll1outrefclk_out (gt0_pll1outrefclk_out ) // output wire gt0_pll1outrefclk_out

);

endmodule

这里因为这个比较简单,我们便不再给出相应的测试文件,想写的同学可以试着书写。

仿真结果

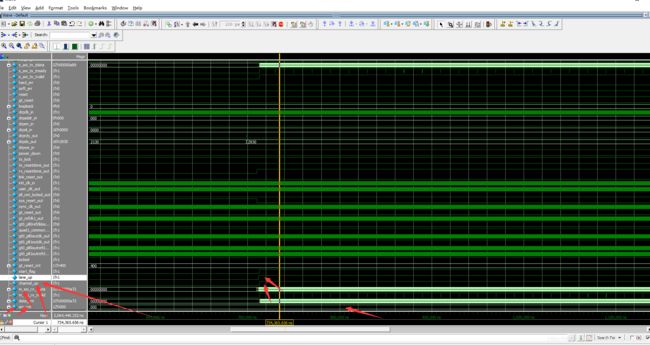

这里给出我们MZ7015开发板的仿真结果如下:

从图中可以看出,误码的个数为零,所以证明了我们设计的准确性。

下板结果

由于在家的硬件条件不够我们没办法进行下板测试,但是这个项目我们在学校的时候已经下板测试过了误码为零,从而证明了我们实验的正确性。

总结

创作不易,认为文章有帮助的同学们可以关注、点赞、转发支持。(txt文件、图片文件在群中)对文章有什么看法或者需要更近一步交流的同学,可以加入下面的群:

![]()