数字电路技术基础(三)

文章目录

- 第三章 门电路

- 概述

- 半导体二极管门电路

- 半导体二极管的开关特性

- 二极管与门

- 二极管或门

- CMOS门电路

- MOS管的开关特性

- MOS管的工作原理

- MOS管的输入特性和输出特性

- MOS管的四种类型

- CMOS反相器的电路结构和工作原理

- 反相器的电路结构

- 电压传输特性和电流传输特性

- 输入端噪声容限

- CMOS反相器的静态输入特性和输出特性

- CMOS反相器的动态特性

- 1.传输延迟时间$t_{PHL}$,$t_{PLH}$

- 2.交流噪声容限

- 3.动态功耗

- 其他类型的CMOS门电路

- 一.其他逻辑功能的CMOS门电路

- 二.漏极开路输出门电路(OD门)

- 三.CMOS传输门和三态门

- TTL门电路

- TTL工作原理

- TTL的输入特性和输出特性

- TTL的基本开关电路

- TTL的动态开关特性

- TTL反相器的电路结构和工作原理

- 一.电路结构

- 二.输入噪声容限

- TTL反相器的静态输入特性和输出特性

- TTL反相器的输入端负载特性

- TTL反相器的扇出系数

- TTL反相器的动态特性

- 传输延迟时间

- 交流噪声容限

- 动态尖峰电流

- 其他类型的TTL门电路

- 其他逻辑功能的TTL门电路

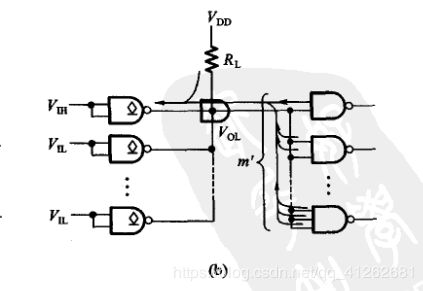

- 集电极开路输出的门电路(OC门)

- 三态门(TS门)

第三章 门电路

概述

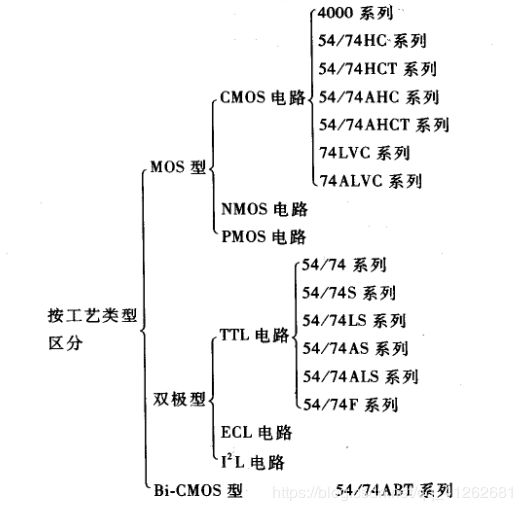

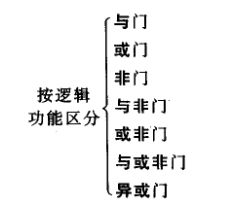

用以实现基本逻辑运算和复合运算的单元电路称为门电路

常用的门电路在逻辑功能上有与门,或门,非门,与非门,或非门,与或非门,异或门

TTL的缺点是功耗过大,CMOS有很大的优势

半导体二极管门电路

半导体二极管的开关特性

假定输入信号的高电平 V I H = V C C V_{IH}=V_{CC} VIH=VCC,低电平 V I L = 0 V_{IL}=0 VIL=0,

假定二极管D为理想开关元件,即正向导通电阻为0,反向内阻为无穷大

当 V I = V I H V_{I}=V_{IH} VI=VIH时,D截止, V O = V C C V_{O}=V_{CC} VO=VCC

当 V I = V I L V_{I}=V_{IL} VI=VIL时,D导通, V O = V O L = 0 V_{O}=V_{OL}=0 VO=VOL=0

二极管与门

虽然电路很简单,但是有缺点

缺点:

1.输出的高低电平数值和输入的高低电平数值不相等。多级串联时会发生信号的偏移

2.当输出端对地接上负载时负载电阻的改变会影响输出的高电平。

因此,这种电路只做集成电路内部的逻辑单元,而不用它去驱动负载负载

二极管或门

CMOS门电路

MOS管的开关特性

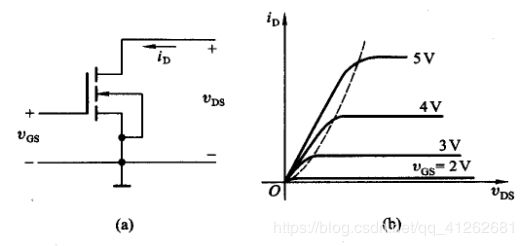

MOS管的工作原理

见模电第一章

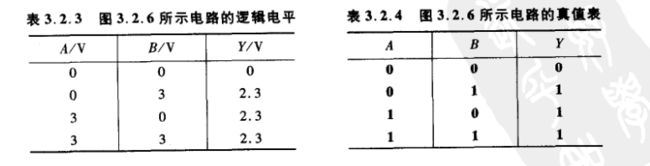

MOS管的输入特性和输出特性

MOS管的四种类型

CMOS反相器的电路结构和工作原理

反相器的电路结构

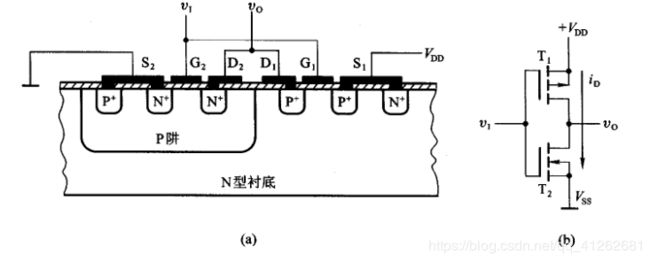

T 1 T_1 T1为P沟道增强型MOS管, T 2 T_2 T2为N沟道增强型MOS管

当 V I = V O H = V D D V_I=V_{OH}=V_{DD} VI=VOH=VDD时, T 1 T_1 T1截止, T 2 T_2 T2导通,所以 V O = V O L V_O=V_{OL} VO=VOL

输入与输出之间为逻辑非的关系。所以也称反相器

电压传输特性和电流传输特性

1.电压传输特性

(1)A-B段, V I < V G S ( t h ) N V_I<V_{GS(th)N} VI<VGS(th)N,而 ∣ V G S 1 ∣ > ∣ V G S ( t h ) P ∣ |V_{GS1}|>|V_{GS(th)P}| ∣VGS1∣>∣VGS(th)P∣,所以 T 1 T_1 T1导通而 T 2 T_2 T2截止,所以 V O = V O H ≈ V D D V_O=V_{OH}\approx V_{DD} VO=VOH≈VDD

(2)C-D段, V I > V D D − ∣ V G S ( t h ) P ∣ V_I>V_{DD}-|V_{GS(th)P|} VI>VDD−∣VGS(th)P∣,使得 ∣ V G S 1 ∣ < ∣ V G S ( t h ) P ∣ |V_{GS1}|<|V_{GS(th)P}| ∣VGS1∣<∣VGS(th)P∣,所以 T 1 T_1 T1截止,而 V G S 2 > V G S ( t h ) N V_{GS2}>V_{GS(th)N} VGS2>VGS(th)N, T 1 T_1 T1导通。所以 V O = V O L ≈ 0 V_O=V_{OL}\approx 0 VO=VOL≈0

(3)B-C段, V D D − ∣ V G S ( t h ) P ∣ < V I < V G S ( t h ) N V_{DD}-|V_{GS(th)P|}<V_I<V_{GS(th)N} VDD−∣VGS(th)P∣<VI<VGS(th)N, V G S 2 > V G S ( t h ) N V_{GS2}>V_{GS(th)N} VGS2>VGS(th)N, ∣ V G S 1 ∣ > ∣ V G S ( t h ) P ∣ |V_{GS1}|>|V_{GS(th)P}| ∣VGS1∣>∣VGS(th)P∣, T 1 T_1 T1和 T 2 T_2 T2同时导通, V I = 1 2 V D D V_I=\frac{1}{2}V_{DD} VI=21VDD时, V O = 1 2 V D D V_O=\frac{1}{2}V_{DD} VO=21VDD

2.电流传输特性

当工作在A-B段和C-D段时由于总有一个管子是截止的,所以流经 T 1 T_1 T1和 T 2 T_2 T2的电流几乎为0.

当工作在B-C段时, T 1 T_1 T1和 T 2 T_2 T2之间有电流流过,在 1 2 V D D \frac{1}{2}V_{DD} 21VDD处出现尖峰电流

所以不应使器件长期工作在B-C段,以免功耗过大而损坏

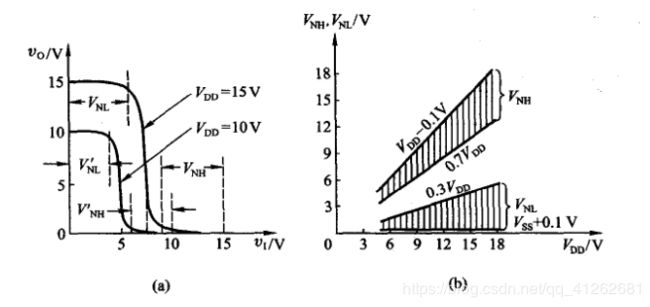

输入端噪声容限

V N H = V O H ( m i n ) − V I H ( m i n ) V_{NH}=V_{OH(min)-V_{IH(min)}} VNH=VOH(min)−VIH(min)

V N L = V I L ( m a x ) − V O L ( m a x ) V_{NL}=V_{IL(max)-V_{OL(max)}} VNL=VIL(max)−VOL(max)

CMOS反相器的静态输入特性和输出特性

一.输入特性

输入特性,即反相器输入电压和输入电流的关系

MOS管的栅极和衬底之间存在着以SiO2为介质的输入电容,而绝缘层非常薄,易被击穿,所以要加入输入保护

当 V I > V D D + V D 1 ( t h ) V_{I}>V_{DD}+V_{D1(th)} VI>VDD+VD1(th)时,电位被钳制在 V D D + V D 1 ( t h ) V_{DD}+V_{D1(th)} VDD+VD1(th)

当 V I < − V D 1 ( t h ) V_{I}<-V_{D1(th)} VI<−VD1(th),电位被钳制在 − V D 2 ( t h ) -V_{D2(th)} −VD2(th)

二.输出特性

反相器输出电压和输出电流的关系为输出特性

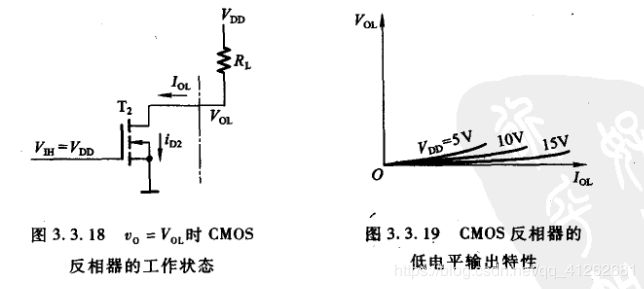

1.低电平输出特性

V O L V_{OL} VOL和 I O L I_{OL} IOL的关系就是T2的漏极特性曲线

2.高电平输出特性

CMOS反相器的动态特性

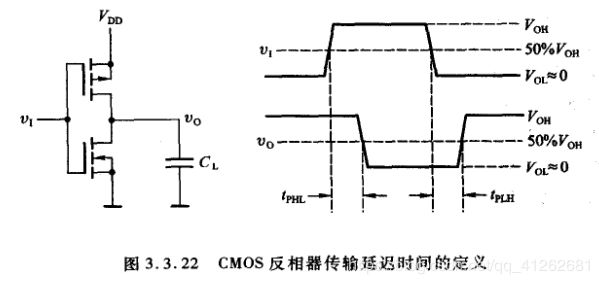

1.传输延迟时间 t P H L t_{PHL} tPHL, t P L H t_{PLH} tPLH

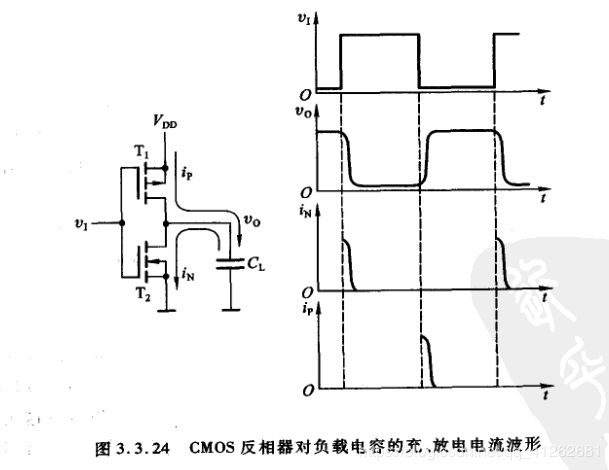

由于MOS管的电极之间以及电极和衬底之间都存在寄生电容,尤其在反相器的输出端更不可避免的存在负载电容,所以当输入信号发生跳变时,输出电压的变化必然滞后于输入电压的变化。把输出电压变化落后于输入电压变化的时间称为传输延迟时间并且将输出由高电平跳变为低电平时的传输延迟时间记做 t P H L t_{PHL} tPHL,将输出由低电平跳变为高电平时的传输延迟时间记做 t P L H t_{PLH} tPLH。在CMOS电路中, t P H L t_{PHL} tPHL和 t P L H t_{PLH} tPLH是以输入和输出波形对应边上等于最大幅度50%的两点间时间间隔来定义的。因为 t P H L t_{PHL} tPHL和 t P L H t_{PLH} tPLH通常是相等的,所以也用 t p d t_{pd} tpd表示 t P H L t_{PHL} tPHL和 t P L H t_{PLH} tPLH

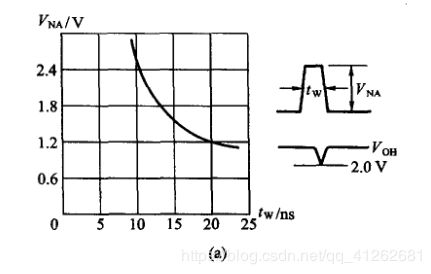

2.交流噪声容限

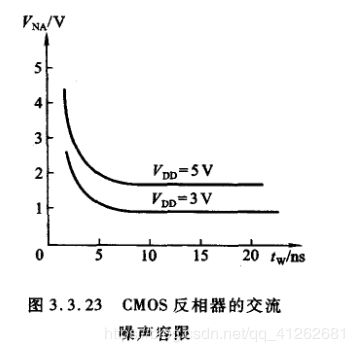

V N A V_{NA} VNA为交流噪声容限, t w t_w tw为噪声电压作用时间

可以得到噪声电压作用时间越短,电源电压越高,交流噪声容限越大

3.动态功耗

动态功耗由两部分组成,一是电容充放电所消耗的功率 P C P_C PC,二是两个MOS管 T 1 T_1 T1和 T 2 T_2 T2短时间导通所消耗的功率 P T P_T PT

P C = C L f V D D 2 P_C=C_LfV^{2}_{DD} PC=CLfVDD2

推导过程:

P T = C P D f V D D 2 P_T=C_{PD}fV^{2}_{DD} PT=CPDfVDD2

C P D C_{PD} CPD为功耗电容,f 为输入信号的重复频率

总动态功耗为 P D = P C + P T P_D=P_C+P_T PD=PC+PT

总功耗为 P T O T = P D + P S P_{TOT}=P_D+P_S PTOT=PD+PS

P S P_S PS静态功耗= V D D I D D V_{DD}I_{DD} VDDIDD

当频率很高时,静态功耗可忽略

其他类型的CMOS门电路

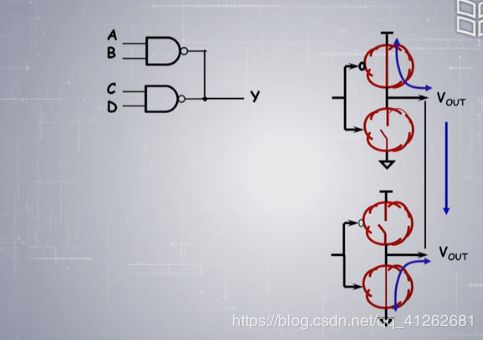

一.其他逻辑功能的CMOS门电路

与非

或非

上面电路组成问题

输出电阻会变化,会影响电压输出特性

因此要在电路前后加缓冲非门

注意,与非门里核心器件是或非,或非门核心器件是与非门

二.漏极开路输出门电路(OD门)

两与非门直接相连会发生电源和地短路的情况

解决办法:去掉上面半端

得到的电路,下端的MOS管的漏极为开路,所以为开漏电路

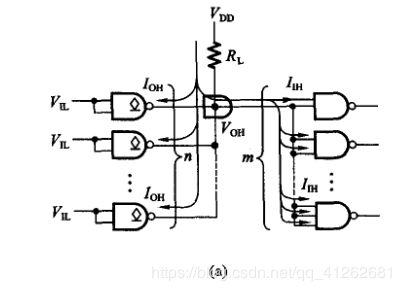

OD门工作时需要上拉电阻 R L R_L RL至电源

对于OD门

可以将输出并联使用,实现 线与

使用时需外接 R L R_L RL, V D D V_{DD} VDD

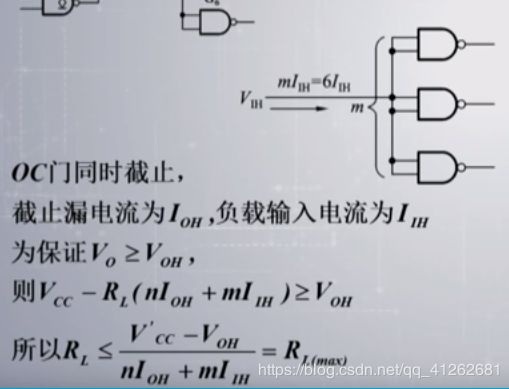

R L R_L RL的计算方法:

1.上限

R L R_L RL不能太高,因为会将高电平拉低

2.下限

也不能太小,否则前端直接将电源接地,会损毁管子

R L R_L RL要满足

![]()

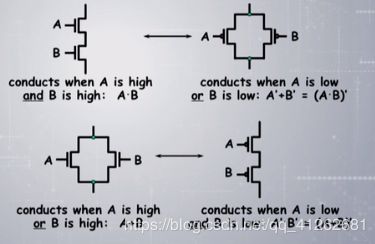

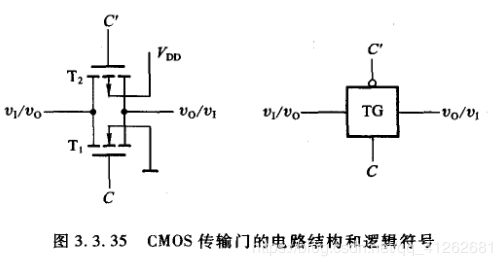

三.CMOS传输门和三态门

将衬底一个接电源,一个接地,该结构导通的关键在于栅极有没有加上合适的电场

只要C加1,就能导通

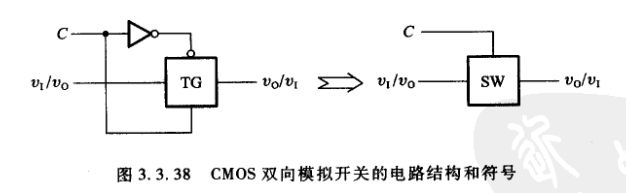

*双向模拟开关

当C为0时,为高阻态

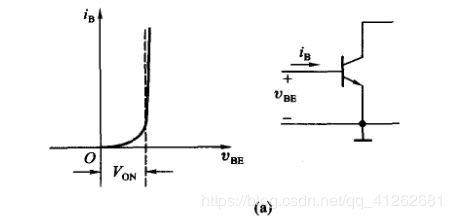

TTL门电路

TTL工作原理

见模电第一章

TTL的输入特性和输出特性

TTL的基本开关电路

TTL的动态开关特性

TTL反相器的电路结构和工作原理

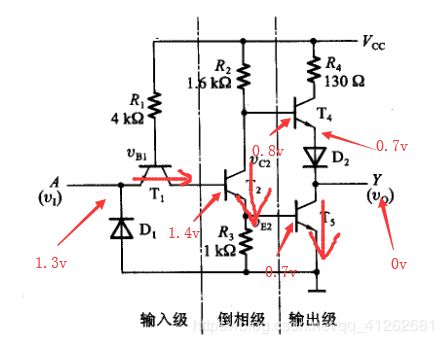

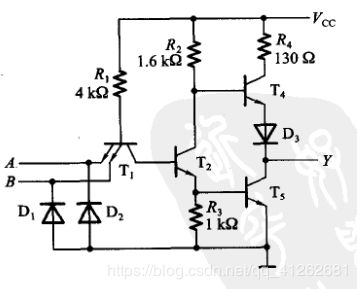

一.电路结构

典型电路

1.工作特性

2.工作原理

电压传输特性曲线

当 V I < 0.6 v V_I<0.6v VI<0.6v时,假设 V I = 0 V_I=0 VI=0,当电路刚上电时 V B 1 V_{B1} VB1和A之间压差为5v左右,而 T 2 T_2 T2的集电结有0.7的压降,导致 T 1 T_1 T1集电结正偏,所以 T 1 T_1 T1饱和导通,此时 T 1 T_1 T1管的集电极即 T 2 T_2 T2的基极的电位为0+饱和压降0.2=0.2v左右,所以 T 2 T_2 T2截止,所以 T 5 T_5 T5也截止, T 4 T_4 T4基极电位为5v,所以 T 4 T_4 T4导通

当 V I V_I VI增大到使得 T 2 T_2 T2的基极大于0.7v时, T 2 T_2 T2导通且工作在放大区

当 V I V_I VI上升到1.3v时,使得 T 5 T_5 T5基极电位到0.7v, T 5 T_5 T5导通, T 4 T_4 T4截止,截止原因是 T 4 T_4 T4的基极被 T 2 T_2 T2和 T 5 T_5 T5拉到0.8v

(1)A-B段,截止区 V I < 0.6 v V_I<0.6v VI<0.6v,所以 V B 1 V_{B1} VB1<1.3v,此时 T 1 T_1 T1导通, T 2 T_2 T2, T 5 T_5 T5截止, T 4 T_4 T4导通

V O H = V C C − V R 2 − V B E 4 − V D 2 = 3.4 V V_{OH}=V_{CC}-V_{R2}-V_{BE4}-V{D2}=3.4V VOH=VCC−VR2−VBE4−VD2=3.4V

(2)B-C段,线性区 0.6 v < V I < 1.3 v 0.6v<V_I<1.3v 0.6v<VI<1.3v, T 2 T_2 T2导通且在放大区, T 5 T_5 T5截止, T 4 T_4 T4导通, V I V_I VI上升, V O V_O VO下降

(3)C-D段,转折区 V I = V T H ≈ 1.4 v V_I=V_{TH}\approx 1.4v VI=VTH≈1.4v, V B 1 > 2.1 V V_{B1}>2.1V VB1>2.1V T 2 T_2 T2 T 5 T_5 T5导通, T 4 T_4 T4截止,所以 V O V_O VO迅速下降,为0

(4)D-E段,饱和区, V I V_I VI继续上升,而 V o V_o Vo不变

几个问题:

T2的输出 V C 2 V_{C2} VC2与 V E 2 V_{E2} VE2方向相反,故称为倒相极

输出级在稳态下 T 4 T_4 T4和 T 5 T_5 T5总有一个导通和截止,既降低功耗又提高带负载能力,又称推拉式

D 1 D_1 D1抑制负向干扰, D 2 D_2 D2保证 T 4 T_4 T4截止

二.输入噪声容限

V N H = V O H ( m i n ) − V I H ( m i n ) V_{NH}=V_{OH(min)-V_{IH(min)}} VNH=VOH(min)−VIH(min)

V N L = V I L ( m a x ) − V O L ( m a x ) V_{NL}=V_{IL(max)-V_{OL(max)}} VNL=VIL(max)−VOL(max)

TTL反相器的静态输入特性和输出特性

一.输入特性

稳态下的 i I = f ( V I ) i_I=f(V_I) iI=f(VI)

重点讨论 V I = V I H / V I L 下 的 i I V_I=V_{IH}/V_{IL}下的i_I VI=VIH/VIL下的iI

1.当 V I = V I L = 0.2 v V_{I}=V_{IL}=0.2v VI=VIL=0.2v

I I L = − ( V C C − V B E 1 − V I L ) R 1 = − 1 m A I_{IL}=\frac{-(V_{CC}-V_{BE1}-V_{IL})}{R_1}=-1mA IIL=R1−(VCC−VBE1−VIL)=−1mA

I I L I_{IL} IIL是流出的

2.当 V I = V I H = 3.4 v V_{I}=V_{IH}=3.4v VI=VIH=3.4v时

发射结反偏, I I H I_{IH} IIH很小

一.输出特性

1.高电平输出特性

当 V O = V O H V_{O}=V_{OH} VO=VOH, V O H = f ( i L ) V_{OH}=f(i_{L}) VOH=f(iL)

i L i_{L} iL流出,所以为负值,这时 T 4 T_4 T4导通

工作在射级输出状态, R O R_O RO很小

i L ( m a x ) < 0.4 m A i_{L(max)}<0.4mA iL(max)<0.4mA

2.低电平输出特性

当 V O = V O L V_{O}=V_{OL} VO=VOL, V O H = f ( i L ) V_{OH}=f(i_{L}) VOH=f(iL)

(1) i L i_{L} iL流入, T 5 T_5 T5饱和导通 , R o R_o Ro很小

(2) V O L < 0.4 v V_{OL}<0.4v VOL<0.4v, i L ( m i n ) = 16 m A i_{L(min)}=16mA iL(min)=16mA

TTL低电平时带负载能力较强

TTL反相器的输入端负载特性

1.当输入端经电阻接地, V I ≠ 0 V_I\neq 0 VI̸=0,且随 R P R_P RP升高而升高

当 V B 1 = 2.1 V V_{B1}= 2.1V VB1=2.1V时, R P R_P RP上升, V I V_I VI不在上升

2.在 V B 1 < 2.1 V ( V I < 1.4 v ) V_{B1}< 2.1V(V_I<1.4v) VB1<2.1V(VI<1.4v)时, V I = R P R I + R P ( V C C − V B E 1 ) V_I=\frac{R_P}{R_I+R_P}(V_{CC}-V_{BE1}) VI=RI+RPRP(VCC−VBE1)

TTL反相器的扇出系数

V O H ≥ 3.2 V 时 , 查 得 ∣ i O H ∣ = 0.4 m A V_{OH}\geq3.2V时,查得|i_{OH}|=0.4mA VOH≥3.2V时,查得∣iOH∣=0.4mA

V O L ≤ 0.2 V 时 , 查 得 ∣ i O L ∣ = 16 m A V_{OL}\leq0.2V时,查得|i_{OL}|=16mA VOL≤0.2V时,查得∣iOL∣=16mA

对于一个标准TTL门电路扇出系数是10

TTL反相器的动态特性

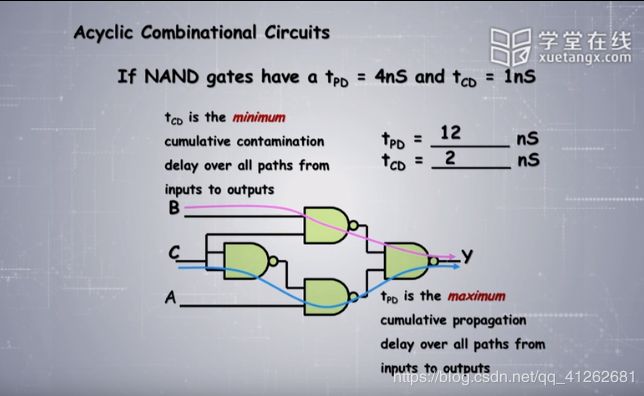

传输延迟时间

t P D t_{PD} tPD找最长路径

t C D t_{CD} tCD找最短路径

交流噪声容限

当输入信号为窄脉冲时,且接近 t P D t_{PD} tPD时,输出变化跟不上,变化很小,因此交流噪声容限远大于直流噪声容限

正脉冲噪声容限

负脉冲噪声容限

动态尖峰电流

交流电流

其他类型的TTL门电路

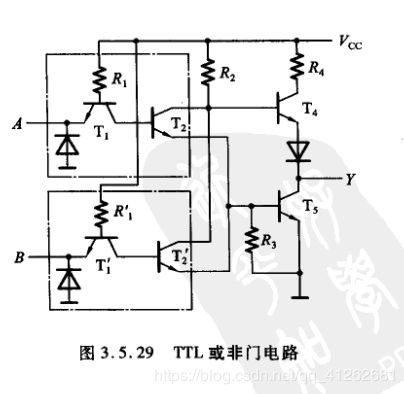

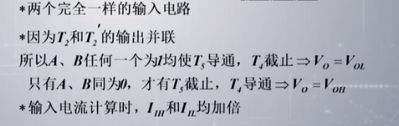

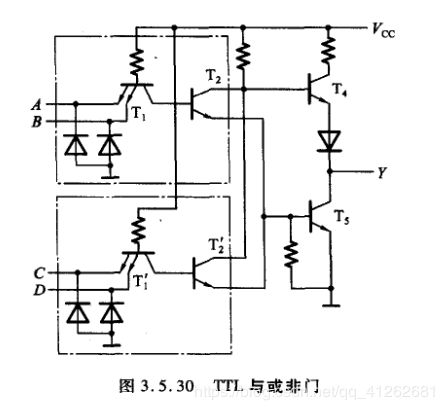

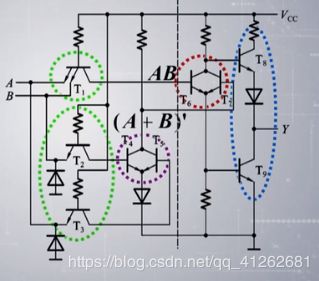

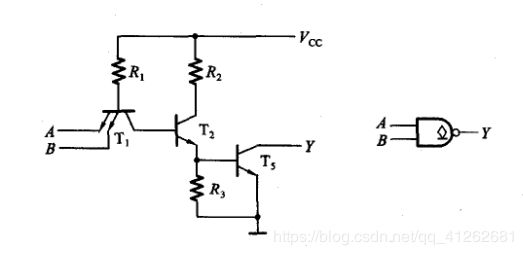

其他逻辑功能的TTL门电路

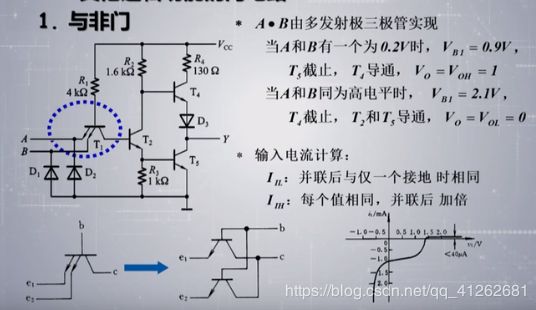

1.与非门

2.或非门

3.与或非门

上面两个结合

4.异或门

集电极开路输出的门电路(OC门)

和CMOS的OD门类似

推拉式输出电路的局限性:

(1).输出电平不可调

(2).负载能力不强,尤其是高电平输出

(3).输出端不能并联输出

会产生电源到地的短路

2.OC门的结构特点

取消了上半部分

T 5 T_5 T5可承受较大电流

工作时需要外接 R L R_L RL, V c c V_{cc} Vcc

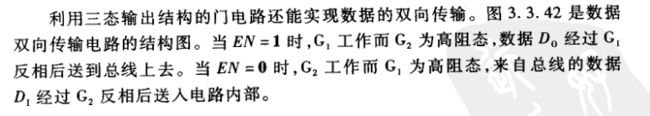

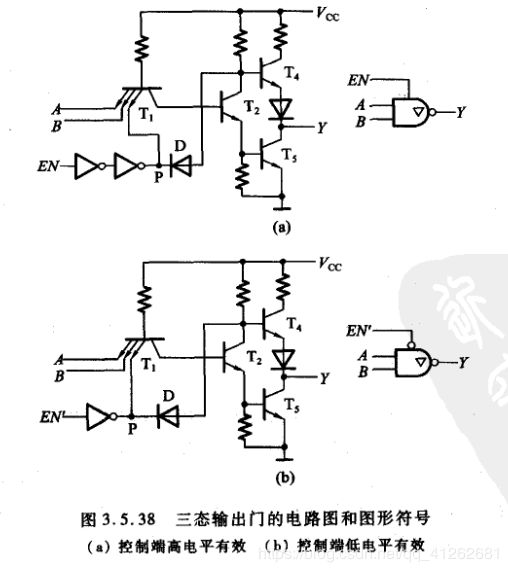

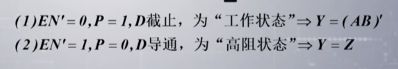

三态门(TS门)

以下图做分析:

当 E N ′ EN\prime EN′输入高电平

则,T4和T5都会被截止

输出有三个状态:

逻辑1,逻辑0,高阻态