微机原理——扩展存储器设计

目录

- 【1】存储器的层次结构

- 【2】存储器的分类

- 【3】SRAM

- 1、基本原理:

- 2、结构:

- 3、芯片参数与引脚解读:

- 4、CPU与SRAM的连接方式

- 【4】DRAM

- 1、基本原理:

- 2、结构

- 3、芯片引脚解读:

- 【5】存储器系统设计

- 【6】存储器扩展设计(重点)

- 1、位扩展(位并联法)

- 2、字节扩展(地址串联法)

- 3、字节和位扩展

- 【7】片选信号产生(译码电路)(重点)

- 1、全地址译码

- 例题

- 2、部分地址译码

- 例题

- 3、线选译码方式

- 4、三种译码方式的比较

- 4、地址译码电路设计

- 步骤:

- 【1】基于74LS138专用译码器的设计

- 【2】基于74LS688比较器的设计

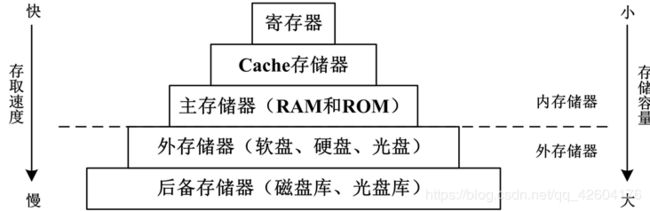

【1】存储器的层次结构

【2】存储器的分类

【3】SRAM

1、基本原理:

静态随机存取存储器(SRAM):

所谓的“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。

当电力供应停止时,SRAM储存的数据还是会消失(被称为volatile memory),这与在断电后还能储存资料的ROM或闪存是不同的。

2、结构:

⦁ 存储矩阵,决定存储器中存储单元的排列形式,有字结构和位结构两种

⦁ 地址译码器,用来选择存储单元,有线性译码和复合译码两种,通常采用复合译码

⦁ 控制逻辑与三态数据缓冲器,控制CS、WR、RD信号

3、芯片参数与引脚解读:

以6116(2K x 8)为例:

2K:表示该芯片内部存储单元的数目,这个数决定存储芯片地址线的数目。

8:表示该芯片每个存储单元存储信息的位数,这个数决定存储芯片数据线的数目。

引脚号如下:

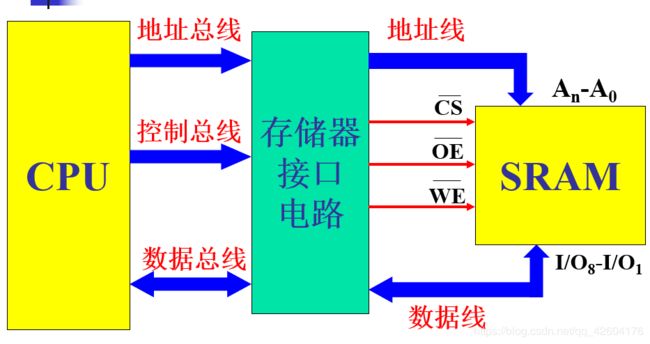

4、CPU与SRAM的连接方式

【4】DRAM

1、基本原理:

![]()

![]()

2、结构

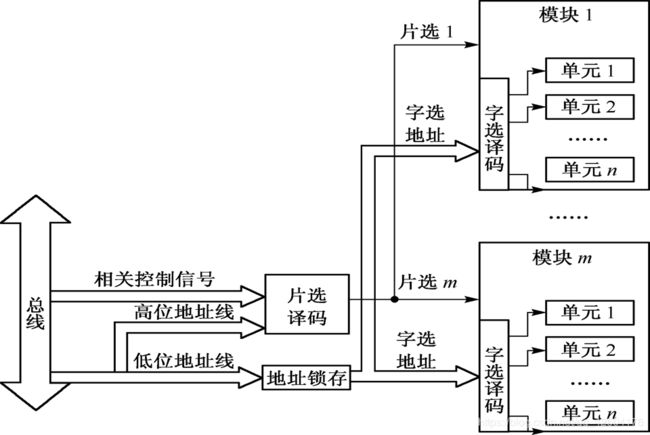

⦁ DRAM的地址线是复用的,即地址线分为行地址和列地址两部分。在对存储单元进行访问时,由行地址选通信号RAS把行地址送入行地址锁存器;再由列地址选通信号CAS把列地址送入列地址锁存器

⦁ CPU与DRAM之间的信息交换由DRAM控制器完成。

3、芯片引脚解读:

【5】存储器系统设计

所要考虑的问题:

1、总线的负载能力

2、CPU时序和存储器存取速度之间的配合

3、存储芯片的选择以及数目

4、片内寻址和片间寻址地址线的分配

5、译码电路的选取(线性译码、全译码、部分译码)

6、数据线、控制线的连接

【6】存储器扩展设计(重点)

1、位扩展(位并联法)

⦁ 位扩展指用多个存储器器件对字长进行扩充。一个地址同时控制多个存储器芯片。

进行位扩展时,模块中所有芯片的地址线和控制线互连形成整个模块的地址线和控制线,而各芯片的数据线并列(位线扩展)形成整个模块的数据线(8bit宽度)。

为何需要位扩展?

在微机系统中,存储器是按字节来构成的,而所选择的存储器芯片的字长不足8位

时,用这样的存储器芯片构成系统所需的存储器子系统电路,就必须进行位扩展,即

用几片存储器芯片并起来,以增加存储字长。例如上图,两个4位组成一个8位。所以称为“位扩展”。

2、字节扩展(地址串联法)

⦁ 字扩展指的是增加存储器中字的数量。

进行字扩展时,模块中所有芯片的地址线、控制线和数据线互连形成整个模块的低位地址线、控制线和数据线 , CPU的高位地址线(扩展的字线)被用来译码以形成对各个芯片的选择线 —— 片选线

3、字节和位扩展

![]()

1、首先对芯片分组进行位扩展,以实现按字节编址;

2、其次设计个芯片组的片选进行字扩展,以满足容量要求;

【7】片选信号产生(译码电路)(重点)

1、全地址译码

除了用于存储器芯片片内地址外,CPU总线的其他地址总线都参加芯片的片选地址译码。

特点:

存储器芯片只占用整个存储空间中的一块区域,访问该存储芯片片内单元采用唯一的地址。

例题

例:在8088CPU工作在最大方式组成的微机应用系统中,扩充设计8KB的

SRAM电路,SRAM芯片用Intel6264。若分配给该SRAM的起始地址为62000H~

63FFFH,片选信号(CS1) 为低电平有效。请用全地址译码方法设计该SRAM存储器的

片选信号形成电路

分析:

1、Intel 6264

2、8K ×8位:8KB,所以只需要1片6264,不需要扩展

3、8086/8088CPU的地址总线均为20位,8086/8088CPU的寻址范围为1MB; 8086有16根数据线和20根地址线,它既能处理16位数据,也能处理8位数据。可寻址的内存空间为1MB。

4、6264片内地址线有13根:A0~A12,所以CPU总线的低13位直接与片内地址引脚相连接,作为片内寻址,来选择片内具体单元。

5、由于采用全译码方式,CPU高7位A19~A13全部参加译码。且芯片数量是1MB/8KB=128片。所以有128个片选地址。2^7=128.

62000H/2000H=49(10000H=8*2000H)转换成二进制:0110001

6、片选信号是低电平有效,所以在地址译码设计中,若采用门电路,注意:A19~A13所有1进行逻辑与非,所有0进行逻辑或。

7、系统总线IO/M‘也参加译码

最终结果:

总结:…感觉步骤还挺多的,不过按照这个流程走一遍,第二次做的时候就很简单了。

2、部分地址译码

也称局部地址译码。片选信号不是由地址线中所有不在存储器上的地址线译码产生,而是只有部分高位地址线被送入译码电路产生片选信号。

特点:某些高位地址线被省略而不参加地址译码,简化了地址译码电路,但地址空间有重叠。

例如,在8088 CPU组成的微机系统中,存储器芯片采用8KB容量的6264芯片。在设计地址译码时,地址线A19未参加译码,只有A13—A18 6条地址线参加译码。这时每块6264将占有两个8KB的内存空间。也就是说,内存空间发生了重叠现象,其重叠情况如图6.23所示。从图中可以看到,连接到内存空间最低8KB地址区的那一块6264芯片,实际占有的内存地址空间为:00000H—01FFFH、80000H—81FFFH。它占有了两个8KB的内存空间。可以依此类推,如果有两条高位地址线不参加地址译码,那么就会使4个存储空间发生重叠; 3条高位地址线不参加地址译码,则会产生8个重叠空间。重叠空间数满足下述关系:重叠空间数=2",其中,n为不参加地址译码的高位地址线。

例题

例:在8088 CPU工作在最小方式组成的微机应用系统中,扩充设计8KB的SRAM电路,SRAM芯片用Intel6264。若分配给该SRAM的地址范围为00000H~0FFFFH,片选信号(CS)为低电平有效。请用部分地址译码方法设计该SRAM存储器的片选信号形成电路。

分析:

1、6264的容量是8KB,然而00000H0FFFFH是64KB,所以重叠区域有64KB/8KB=8个,且23=8,所以三条高位地址线不做译码,如A15A13

2、IO/M‘=0参加译码

3、线选译码方式

线选法:选择除存储器芯片片内寻址以外的高位地址线中的某一条,作为存储器芯片的片选信号。

由于片选的地址线每次寻址时只能有一位有效,不允许同时有多位有效,这才保证每次只选中一个芯片或一个芯片组。

优点:选择芯片不需要外加逻辑电路,姨妈线路简单。

缺点:把地址空间分成了相互隔离的区域,且地址重叠区域多,不能充分利用系统的存储器空间。

4、三种译码方式的比较

全译码:

系统所有地址线全部都应该参与译码

低段地址线应直接接在模块上,寻址模块内单元;

中段地址线译码后产生片选信号区分不同模块;

高段地址线可用作片选信号有效的使能控制;

部分译码:

高端地址信号不参与译码,会造成地址空间的重叠和不连续

线译码;

电路结构简单,但系统必须保证参与片选的地址线不能同时为有效电平;

同部分译码法一样,因为有地址信号不参与译码,也存在地址重叠及不连续的问题

4、地址译码电路设计

步骤:

1、根据系统中实际存储器容量,确定存储器在整个寻址空间中的位置

2、根据所选用存储芯片的容量,画出地址分配图,地址分配表

3、根据地址分配图或分配表确定译码方法并画出相应的地址位图

4、选用合适期间,画出译码电路

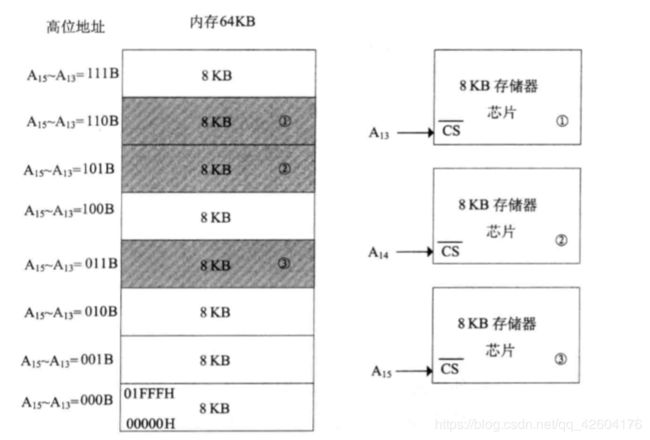

某微机系统地址总线为16位,实际存储器容量为16KB,ROM区和RAM区各占8KB。其中,ROM采用2KB的EPROM,RAM采用1KB的RAM,试设计译码电路.

1、该系统的寻址空间最大为64KB,假定实际存储器占用最低16KB的存储空间,即地址为0000H3FFFH。其中0000H1FFFH为EPROM区,2000H~3FFFH为RAM区。

2、根据所采用的存储芯片容量,可画出地址分配图;地址分配表

对于ROM来说每个子区域为2KB=2^11,需要11位地址线作为片内寻址:A0~A10;

对于RAM来说每个子区域为1KB=2^10,需要10位地址线作为片内寻址:A0~A9;

采用3—8译码器,前四根指向4片ROM,后四根加上一个A10构成二次译码,指向8片RAM;

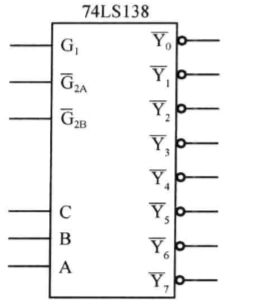

【1】基于74LS138专用译码器的设计

引脚

真值表

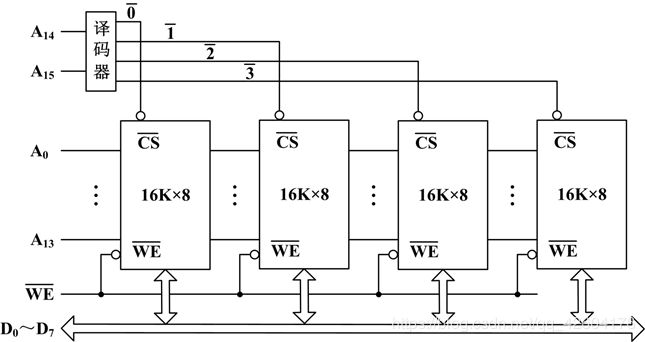

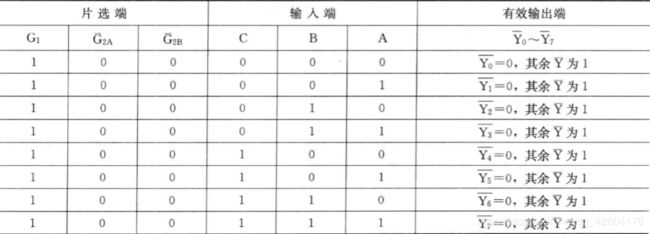

例题1:在某 8088微处理器系统中,需要用8片6264构成一个64KB的存储器。其地址分配在0000H~0FFFFH内存空间,地址译码采用全译码方式,用74LS138作译码器,请画出存储器译码电路。

分析:

1、6264片内地址线有13根:A0~A12,所以CPU总线的低13位直接与片内地址引脚相连接,作为片内寻址,来选择片内具体单元。

2、由于采用全译码方式,CPU高7位A19~A13全部参加译码。且芯片数量是8片。

这里我们只是用A13~A15作为译码器的输入,这样正好有8种输出。A16到A19作为选通信号3,全为0.

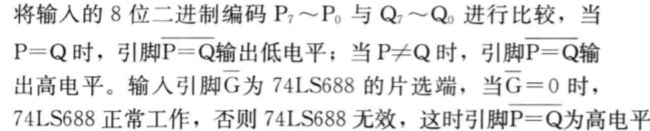

【2】基于74LS688比较器的设计

引脚

工作原理:

例:利用 74LS688设计译码电路,输出端(P= Q)'作为Intel 62128 SRAM的CS片选信号,分配给Intel 62128的地址范围为74000H~77FFFH。画出8088 CPU工作在最大方式下的译码电路。

分析:

74000H转换成2进制:0111 0100, 0000 0000 0000

77FFFH转换成2进制:0111 0111 ,1111 1111 1111

观察发现前6位都是一样的,这样就可以定位大的范围,就可以确定Q的值了:101110(从低位到高位)

所以结果如下:

如果需要改变内存芯片的地址,只需要改变Q那边开关就行了。所以这种结构可以为改变内存地址带来方便。

如果不需要改变地址,则可以直接给定Q边的编码就行了。

参考链接:

SRAM

《微机原理与接口技术.楼顺天版》