计算机组成原理复习(2)

WARNING:不知道准确性,所以希望能够指正讨论错误,小咲会尽量查漏补缺谢谢

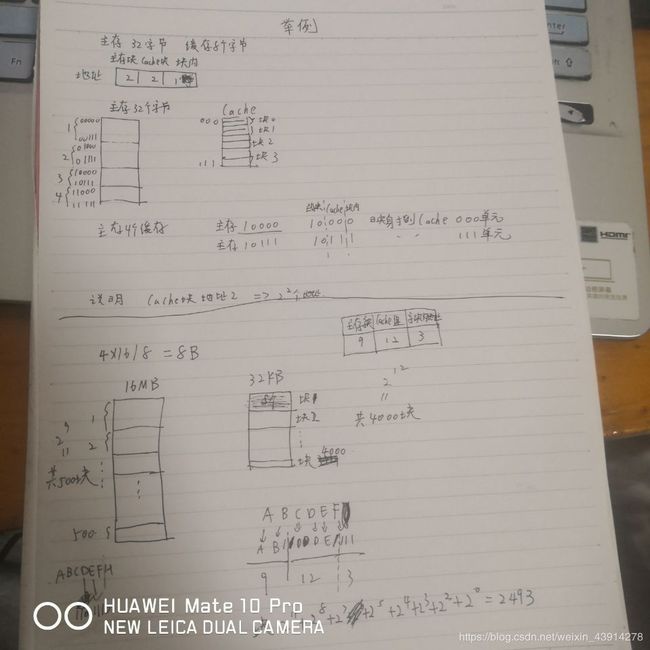

1.设某机主存容量为16MB,Cache容量为32KB,每字块有4个字,每字16位。

求:

(1)如果直接映射时,画出主存地址字段中各段的位数;地址是ABCDEFH存储单元映射到Cache哪个单元。

(2)如果全相映射时,画出主存地址字段中各段的位数。

(3)如果是四路组相联映射,画出主存地址字段中各段的位数;地址是ABCDEFH存储单元映射到Cache哪个单元。

(4)设Cache的初态为空,CPU依次从主存第0,1,2,…,55号单元读出56个字(主存一次读出一个字),并重复按此次序读6次,问命中率是多少?

(3)若Cache的速度是主存的8倍,试问有Cache和无Cache相比,速度约提高多少倍?

解:每字块有4个字,每字16位,4*16/8=8B,所以字块内地址为3位;主存容量16MB,所以总共2^24,也就是24位总长

- Cache共有32KB/2B(16位)=16K字 因每个字块4个字,16K/4=4000块.缓存子块地址为12位

| 主存字块标记 |

缓存字块地址 | 子块内地址 |

| 9 | 12 | 3 |

对应第2493块,所以2^11+2^8+2^7+2^5+2^4+2^3+2^2+2^0=2493 具体看图片解释。上面一般部分我是以主存32字节,缓存8字节为例子,先看懂,然后再具体做本题对应的块。

(2)

| 主存字块标记 |

字块内地址 |

| 21位 |

3位 |

(3)4000块 4列1000行(组) 1000组=2^10

| 主存字块标记 |

Cache组地址 |

字块内地址 |

| 11位 |

10位 |

3位 |

所以2^8+2^7+2^5+2^4+2^3+2^2+2^0=445

(4)每字块有4个字,Cache的初态为空,所以 CPU读第0号单元时未命中,必须访问主存,CPU 读取第0、4、8、12……52,即14次未命中,后5遍全部命中,所以命中率=(56*6-14)/(56*6)

(3)设主存存取周期8t,缓存存取周期t,没有缓存的访问时间8t*(56*6),有缓存的访问时间为t*(56*6-14)+8t*14

速度约提高:(8t*56*6) /(t*(56*6-14)+8t * 14)-1倍

2.磁盘组有6片磁盘,最外两侧盘面不可以记录,存储区域内径22cm,外径33cm,道密度为

40道/cm,内层密度为400位/cm,转速3600转/分,问:

(1)共有多少存储面可用?

(2)共有多少柱面?

(3)盘组总存储容量是多少?

(4)数据传输率是多少?

(5)如果某文件长度超过一个磁盘的容量,应将它记录在同一存储面上还是记录在同

一圆柱面上?为什么?

(6)如果采用定长信息块记录格式,直接寻址的最小单位是什么?寻址命令中如何表

示磁盘地址?

解:(1)共有:6 * 2-2 = 10 个存储面可用

(2)有效存储区域 = (33-22)/ 2 = 5.5cm

柱面数 = 40道/cm * 5.5 = 220道

- 内道周长 = 22 * 3.14 = 69.08 cm

道容量 = 400 * 69.08 = 3454 B

面容量 = 3454 * 220 = 759880 B

盘组总容量 = 759880 B * 12 = 9118560 B

- 转速 = 3600 / 60 = 60 转/秒

传输率 = 3454 * 60 = 207240 B/s

- 记录在同一圆柱面上,因为这样安排存取速度快

- 如果采用定长信息块记录格式,直接寻址的最小单位是扇区。磁盘地址:驱动器号、圆柱面号、盘面号、扇区号

- 设有4个模块组成的四体存储器结构,每个体的存储字长及总线宽度都为64位,存储周期250ns,总线周期50ns试求顺序存储及交叉存储的存储器带宽。

解:

连续读出4个字的信息量 64* 4 = 256 位

顺序存储连续读出4个字的时间:250 * 4 = 1000 ns = 10 ^ (-6) s

交叉存储连续读出4个字的时间:250 + 50 * (4 - 1) =400 ns = 4 * 10 ^ (-7) s

顺序存储存储器带宽:256/(10 ^ (-6))= 2.56 * 10^8 bps

交叉存储存储器带宽:256/(4 * 10 ^ (-7))= 6.4 * 10^8 bps

- 设有效位为110,试用生成多项式G(x)=11011将其编成循环冗余码。

解:

P(x) = x^2 + x^1

数据:11011

N=2=》》需要补两位:1101100/110

CRC冗余码:00

传送数据:1101100

5.填空

(1)DMA方式_ B __。

A.既然能用于高速外围设备的信息传送,也就能代替中断方式;

B.不能取代中断方式;C.也能向CPU请求中断处理数据传送; D.内无中断机制

解释:DMA 直接内存操作

(2)单级中断与多级中断的区别是___A_____。

A. 单级中断只能实现单中断,而多级中断可以实现多重中断

B. 单级中断的硬件结构是一维中断,而多级中断的硬件结构是二维中断

C. 单级中断处理机只通过一根外部中断请求线接到它的外部设备系统;而多级中断,每一个I/O设备都有一根专用的外部中断请求线

(3)采用DMA方式传递数据时,每传送一个数据就要占用一个___C_____时间。

A. 指令周期 B. 机器周期 C. 存储周期 D. 总线周期

(4)磁表面存储器不具备的特点是___C___。

A. 存储密度高 B. 可脱机保存 C. 速度快 D. 容量大

(6)若存储周期250ns,每次读出16位,则该存储器的数据传送率为( C )。

A、4×106字节/秒 B、4M字节/秒 C、8×106字节/秒 D、8M字节/秒

[解析] 存储周期250ns,则每秒读数据4000000次,每次读取2字节,于是该存储器的数据传送率为8×10^6字节/秒。

(7)直接映射cache的主要优点是实现简单。这种方式的主要缺点是( B )。

A 它比其他cache映射方式价格更贵

B 如果使用中的2个或多个块映射到cache同一行,命中率则下降

C 它的存取时间大于其它cache映射方式

D cache中的块数随着主存容量增大而线性增加

例题:

1. 汉明码

(1)写出1101011101对应的汉明码(采用奇校验);偶数个1为1

C1=3⊕5⊕7⊕9⊕11⊕13=1

C2=3⊕6⊕7⊕10⊕11⊕14=0

C4=5⊕6⊕7⊕12⊕13⊕14=1

C8=9⊕10⊕11⊕12⊕13⊕14=1

所以采用奇校验对应的汉明码为:10111011011101

(2)如果接收方收到一组数111011001101(采用偶校验),这组汉明码有错吗?正确传输的数据为多少?

第三位错误,正确数据为01101101

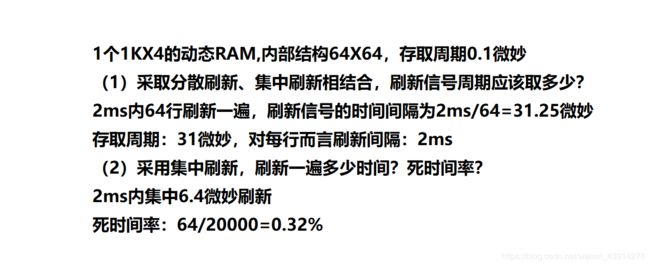

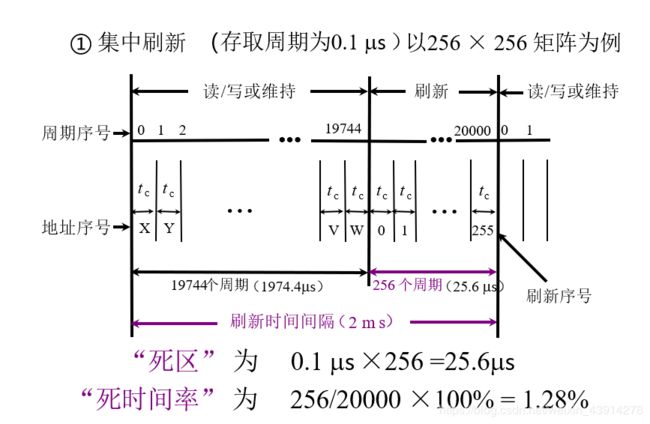

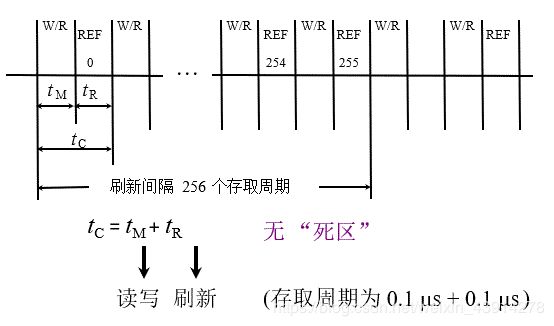

2.已知动态RAM需2ms刷新一次,8K*8位,内部结构256*256矩阵,读写周期0.1μs,试画出三种刷新时间时间分配图(参照书上)。

常用的刷新方法有三种——集中式、分散式、异步式。

解:采用集中刷新方式刷新间隔为:2ms,其中刷新死区为:256×0.1μs=25.6μs

采用分散刷新方式刷新间隔为:256×(0.1μs+0.1μs)=51.2μs

采用异步刷新方式(上述两者结合的方法)刷新间隔为:2ms

2ms内256行刷新一遍,刷新信号的时间间隔为2ms/256=7.8125微妙

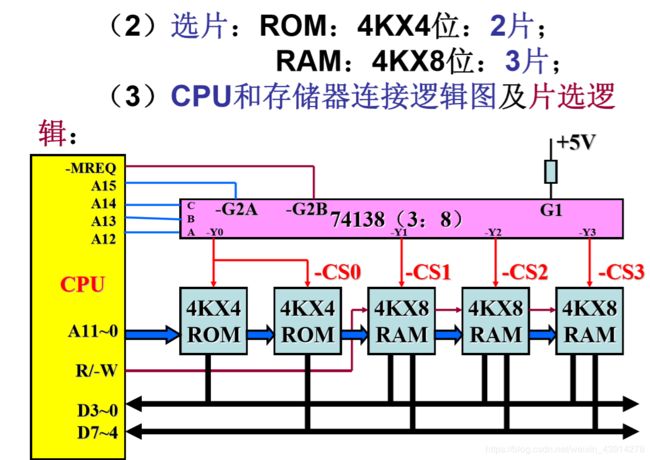

3. 设CPU共有16根地址线,8根数据线,并用(低电平有效)作访存控制信号,作读写命令信号(高电平为读,低电平为写)。现有下列存储芯片:ROM(2K×8位,4K×4位,8K×8位),RAM(1K×4位,2K×8位,4K×8位),及74138译码器和其他门电路(门电路自定)。试从上述规格中选用合适芯片,画出CPU和存储芯片的连接图。要求:

(1)最小4K地址为系统程序区,4096~16383地址范围为用户程序区。

(2)指出选用的存储芯片类型及数量。

(3)详细画出片选逻辑。

解:(1)地址空间分配图:

系统程序区(ROM共4KB):0000H-0FFFH

用户程序区(RAM共12KB):1000H-3FFFH

(2)选片:ROM:选择4K×4位芯片2片,位并联

RAM:选择4K×8位芯片3片,字串联(RAM1地址范围为:1000H-1FFFH,RAM2地址范围为2000H-2FFFH, RAM3地址范围为:3000H-3FFFH)

(3)各芯片二进制地址分配如下:

| A15 |

A14 |

A13 |

A12 |

A11 |

A10 |

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

|

| ROM1,2 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

| RAM1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

| RAM2 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

| RAM3 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |