为什么80%的码农都做不了架构师?>>> ![]()

讲师:钱晓捷

教材:计算机体系结构教程(张晨曦)

时间:2013年9月-12月每周日上午8:30-11:30

地点:郑州大学老校区计算机学院218

持续更新…

第一次课:2013年9月8日上午8:30

计算机系统结构是从更高的层面讲解硬件,包括指令集系统结构、组成和硬件。

自2002年开始,处理器性能的增长率已经降到每年20%的水平,造成这种现象的原因包括:风冷芯片的最大功耗;所剩无几的可以有效发掘的指令级并行;难以降低的存储器时延。所以处理器性能的改进不能再只依赖于指令级并行(ILP),而应更加关注线程级并行(TLP)和数据级并行(DLP)。

主流的计算机分类方式可以分为:桌面计算机、服务器和嵌入式计算机。不同的计算机的设计目标是不同的。

桌面计算机主要关注性价比,性能和价格的综合因素是消费者最关心的。

服务器首先考虑可靠性,其次是扩展性,最后是吞吐量。

嵌入式计算机设计的目标是以最低的价格满足实际的性能需求,而不是追求更高的价格来实现更高的性能。它要求实时性、最小化存储器和最小化功耗。指令集系统结构(ISA,Instruction Set Architecture)指的是程序员可见的实际指令系统。ISA的作用相当于软件和硬件之间的一个分界面。主要分为MIPS和80x86。

虚拟:利益其他部件实现的本来不存在的事物或属性。

透明:本来存在的事物,从某种角度看似不存在。

第二次课:2013年9月15日上午8:30

按指令流和数据流的多倍性对计算机可以分为四类:

SISD(Single Instruction Single Data stream,单指令流单数据流)

SIMD(Single Instruction Multiple Data stream,单指令流多数据流)

MISD(Multiple Instruction Single Data stream,多指令流单数据流)

MIMD(Multiple Instruction Stream Multiple Data stream,多指令流多数据流)定量原理

以经常性事件为重点,对经常发生的情况采用优化的方法。Amdahl(阿姆达尔定律)

定义系统的加速比,用于计算系统中的某个部分进行改进后系统总体性能可获得多大的提高。

系统加速比 = 改进前的总执行时间 / 改进后的总执行时间CPU性能公式

CPU时间 = 时钟周期数 / 时钟频率

= (IC × CPI) / 时钟频率

其中 IC表示指令条数,CPI表示每条指令的时钟周期数

CPI = 总时钟周期 / IC

所以 CPU时间 = IC × CPI ×时钟周期长度局部性原理

处理器访问存储器时,所访问的存储单元在一段时间内都趋向于一个较小的连续区域中。有两种类型的局部性原理,时间局部性说明最近访问过的内容很可能即将被再次使用,空间局部性说地址临近的内容可能在一定时间内被连续使用。性能评测

MIPS(Million Instructions Per Second) = 指令条数 / (执行时间×106),每秒百万条指令数

真实的程序执行时间 = CPU时间 +IO时间

CPU时间=用户时间+系统CPU时间摩尔定律(维基百科)

摩尔定律是由英特尔创始人之一戈登·摩尔提出来的。其内容为:集成电路上可容纳的电晶体数目,约每隔24个月便会增加一倍;经常被引用的“18个月”是由英特尔首席执行官David House所说:预计18个月会将芯片的性能提高一倍(即更多的晶体管使其更快)

尽管这种趋势已经持续了超过半个世纪,摩尔定律仍应该被认为是观测或推测,而不是一个物理或自然法。预计定律将持续到至少2015年或2020年。然而,2010年国际半导体技术发展路线图的更新增长已经放缓在2013年年底,之后的时间里晶体管数量密度预计只会每三年翻一番。并行

同时性:同一时刻发生的并行

并发性:同一时间间隔内发生的并行性

并行的等级:指令内部并行、指令级并行、过程级并行、程序级并行和系统级并行。

第三次课:2013年10月20日上午8:00 (计算机指令集结构)

早期的大多数计算机都是采用堆栈结构或累加器结构的指令集,但是自1980年以后,大多数计算机都陆续采用了通用寄存器结构,优势体现在:

1. 跟其他的CPU内部存储单元一样,寄存器的访问速度比存储器快。

2. 对编译器而言,能更加容易、有效地分配和使用寄存器。

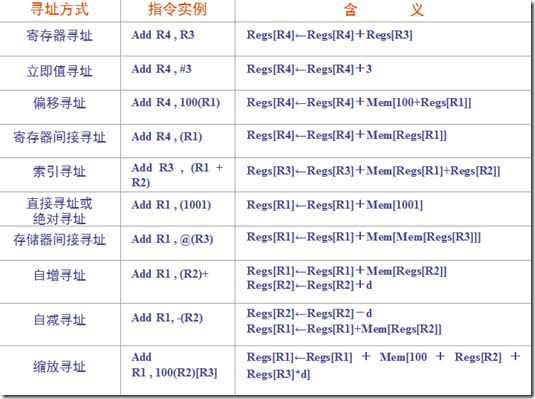

3. 寄存器可以用来存放变量。立即数寻址和偏移寻址是使用频率最高的两种寻址方式。

上图的横坐标表示立即数的位数。我们可以看出,最常用的是较小的立即数。在指令集结构设计中,至少要将立即数的大小设置为8~16位。

指令集结构的功能设计实际上就是确定软硬件的功能分配,主要考虑的因素有3个:速度、成本、灵活性。

用硬件实现的特点是速度快、成本高、灵活性差,用软件来实现的特点是速度慢、价格便宜、灵活性好,一般来说,对出现频率高的基本功能应首选硬件来实现。

对指令集的基本要求是:完整性、规整性、高效率和兼容性。

有两种不同的设计策略,CISC即复杂指令集计算机,它是增强指令功能,把越来越多的功能交由硬件来实现,并且指令的数量也是越来越多,如x86。RISC即精简指令集计算机,它是尽可能把指令集简化,不仅指令集条数少,而且指令的功能也比较简单,如MIPS。CISC指令集结构存在以下问题:

1. 各种指令使用频度相差悬殊。据统计,只有20%的指令使用频度较高,占运行时间的80%,而其余80%的指令只在20%的运行时间内才会用到。

2. 指令集庞大,指令条数多,许多指令的功能又很复杂。这使得硬件非常复杂。RISC指令集结构一般应当遵循以下原则:

1. 指令条数少而简单。

2. 采用简单而有统一的指令格式,病减少寻址方式。指令字长都为32位或64位。

3. 指令的执行在单个时钟周期内完成。

4. 只有load和store指令才能访问存储器,其他指定操作都是在寄存器之间进行。

5. 大多数指令都采用硬连逻辑来实现。

6. 强调优化编译器的作用,为高级语言程序生成优化的代码。

7. 充分利用流水线技术来提高性能。控制指令

控制指令是用来改变控制的,分为四种:分支、跳转、过程调用和过程返回,其中分支指令使用的最为频繁。

本书约定:当指令是无条件改变控制流时,称为跳转指令;而当控制指令是有条件改变控制流是,称为分支指令。

实现分支指令的三种方法为:条件码、条件寄存器、比较与分支。

在控制指令中,必须给出转移的目标地址。指定转移地址最常用的方法是在指令中提供一个偏移量,由该偏移量和程序计数器(PC)的值相加而得出目标地址。这种寻址方式称为PC相对寻址。操作数的类型和大小

计算机系统所能处理的数据类型很多,在设计和实现时,需要研究哪些用硬件实现,哪些用软件实现,并研究它们的实现方法。

数据表示是指计算机硬件能直接识别、指令集可以直接调用的数据类型,一般用硬件实现,如定点数、逻辑数、浮点数、字符、字符串等。

数据结构则不同,它是指由软件进行处理和实现的各种数据类型。数据结构是研究这些数据类型的逻辑结构与物理结构之间的关系,并给出相应的算法。

表示操作数类型的方法有两种:(1)有指令中的操作码指定操作数的类型,这是最常用的方法。(2)给数据加上标识,有数据本身给出类型。指令格式的设计

x86采用变长编码格式,这种格式可以减少目标代码的长度。

MIPS采用定长编码格式,这种格式可以提高编译性能。MIPS指令集结构

MIPS64有32个64位通用寄存器:R0,R1,...,R31。R0的值永远是0。此外还有32个64位的浮点数寄存器:F0,F1,...,F31。

MIPS的数据寻址方式只有立即数寻址和偏移量寻址两种。寄存器间接寻址是通过把0作为偏移量来实现的,16位绝对寻址是通过把R0(值永位0)作为寄存器来完成的。所有的存储器访问都必须是边界对齐的。

所有的指令都是32位的,可分为四大类:load和strore、ALU操作、分支与跳转、浮点数操作。

简单跳转很简单,就是把目标地址送入程序计数器。而跳转并链接则要比简单跳转多一个操作:把返回地址放入寄存器31。

浮点指令对浮点寄存器中的数据进行操作,并有操作码指出操作数是单精度还是双精度。在指令助记符中,用后缀S表示单精度浮点数,用D表示双精度浮点数。

第四次课:2013年11月3日上午8:00 (流水线技术)

重叠执行和先行控制

顺序执行方式的优点是控制简单、节省设备。主要缺点有两个:1. 处理机制下指令的速度慢。只有当上一条指令全部执行完毕后,下一条指令才能够开始执行;2. 功能部件的利用率很低。

一次重叠执行的时间减少了近1/3,二次重叠执行时间减少了近2/3。在一般计算机中,指令和数据混合存储在同一主存中,而且在一个存储器中只能访问一个存储单元,显然无法实现二次重叠执行,可采用以下四种方法解决:1. 设置两个独立了编址的存储器;2. 指令和数据仍然混合存储在同一主存中,但设置两个Cache,指令Cache和数据Cache;3. 指令和数据仍然混合存储在同一主存中,但主存采用多体交叉结构;在一个存储器周期中可以访问多个存储单元;4. 在主存和指令分析部件之间增设指令缓冲站。

先行控制技术实际上就是缓冲技术和预处理技术的结合。缓冲技术是在工作速度不固定的两个功能部件之间设置缓冲器,用以平滑他们的工作。预处理技术是指预取指令、对指令进行加工以及预取操作数等。在先行控制中,指令分析部件和执行部件同时处理的两条指令可以是不相邻的,实现了多条指令的重叠解释执行。因此,先行控制的并行性更高。流水线的基本概念

把一个重复的过程分解为若干子过程,每个子过程由专门的功能部件来实现。将多个处理过程在时间上错开,依次通过各功能段,这样,每个子过程就可以与其它子过程并行执行。这就是流水线技术。流水线中的每个字过程及其功能部件称为流水线的级或段,段与段相互连接形成流水线。流水线的段数称为流水线的深度。流水线有一些特点

1. 流水线吧一个处理过程分解为若干个子过程,每一个子过程有一个专门的功能部件来实现。

2. 流水线中各段的时间应尽可能相等,否则将引起流水线堵塞、断流,因为时间长的段将成为流水线的瓶颈。

3. 流水线每一个功能部件的后面都有一个缓冲寄存器,称为流水寄存器。其作用是在相邻两段之间传送数据,以保证提供后面要用到的数据,并把各段相互隔离。

4. 流水线技术时候于大量重复的时序过程。

5. 流水线需要有通过时间和排空时间。流水线的相关与冲突

一个经典的5段RISC流水线:

1. 取指令周期(IF)

2. 指令译码/读寄存器周期(ID)

3. 执行/有效地址计算周期(EX)

4. 存储器访问/分支完成周期(MEM)

5. 写回周期(WB)相关是指两条指令之间存在某种依赖关系,有3中类型:数据相关、名相关、控制相关。

数据相关就是后面的指令直接或间接地使用前面指令的结果。

名相关指两条或多条指令访问相同名称的寄存器和存储器单元。

控制相关是指由分支指令引起的相关。它需要根据分支指令的执行结果来确定后续指令释放执行。流水线冲突是指对于具体的流水线来说,由于相关的存在,使得指令流中的下一条指令不能在指定的时钟周期执行。

有三种类型的冲突:结构冲突、数据冲突、控制冲突。如果不能很好地解决冲突问题,轻则影响流水线的性能,重则导致错误的执行结果。

解决结构冲突可以引入停顿,或者设置相互独立的指令存储器和数据存储器,或者区分指令Cache和数据Cache。

数据冲突分为:写后读冲突、写后写冲突、读后写冲突。可以通过定向技术来减少数据冲突。定向技术的关键思想是:在某条指令产生技术结果之前,其他指令并不真正立即需要该计算结果,如果能够将该计算结果从其产生的地方直接送到其他指令需要的地方,那么可以避免停顿。

流水线的实现

。。。向量计算机

。。。