XILINX FPGA 高速收发器 GTP设计初探

XILINX 高速收发器GTP之配置

FPGA内嵌收发器相当于以太网中的PHY芯片,但更灵活更高效,线速率也在随着FPGA芯片的发展升级。本文对7系列FPGA内部高速收发器GTP IP核的配置和使用做些简单的总结,以备后续回顾重用。本文是我在读ug482 pg168 官方文档和一些网络资源后的一些个人见解,希望对有需要的朋友有所帮助。我们来逐页分析下IP核配置先导中内容:

1 GT Selection:

我用的是Atrix-7系列FPGA芯片,只能使用速率较低的GTP 收发器,所以类型无法选择。GTP收发器在我这个芯片中最高线速率可达6.6Gbps,具体最大数值会根据器件速度等级和封装有所不同,读者可自行查阅Data Sheet。很多Xilinx IP核都有Shared Logic,我理解是一些重用的部分,当多个地方需要用到这些资源时,将其放置在example design中可以节约硬件资源。

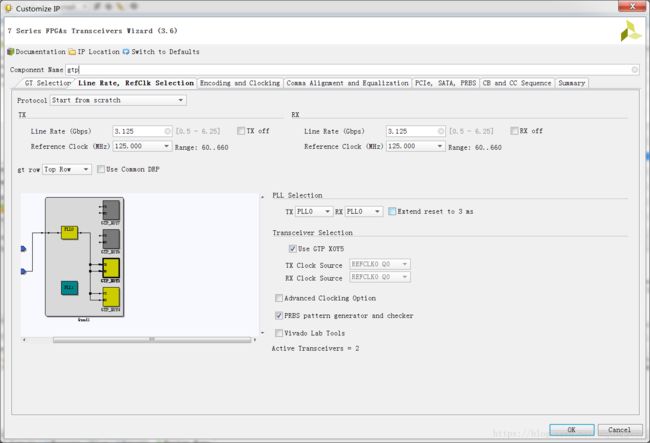

2 Line Rate,RefClk Selection

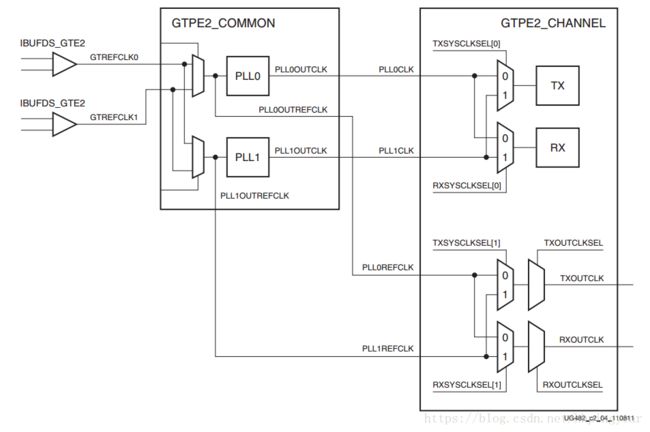

这一页比较重要。高速收发器支持多种标准协议,可以选择一个标准协议,这样后续的选项均已配置好了,然后根据自己的需求改动。此处选择Aurora 8b10b single lane 4byte。收发器发送和接收通道相互独立,可以选择不同的线速率和编码格式,此处均选择一个常见的较低速率3.125Gbps用于功能验证,参考时钟为125M。注意参考时钟为收发器输入时钟,频率必须与开发板上为GTP提供时钟的晶振一致。官方文档中关于外部参考时钟使用示意图如下:

GTP有两个参考时钟输入端口,经差分-单端转换后通过两个PLL产生收发器发送和接收时钟。若TX和RX线速率一致使用同一个PLL产生时钟,否则需要使用两个不同的PLL。开发板中差分晶振连接GTPREFCLK0,且收发速率相同,故PLL Selection TX和RX均选择PLL0,TX Clock Source选择REFCLK0。这里我使用到两个收发器,根据开发板原理图和数据手册选择GTP_X0Y4和GTP_X0Y5.最后使能收发器内部的PRBS生成器和检测器,便于测试了链路性能。

3 Encoding and Clocking

GTP收发器内部处理带宽只有2byte,而GTX等速率更高的收发器是4byte,此处外部数据接口位宽选择32bit确保后期收发器使用部分的经验也适用于GTX等收发器。编码方式采样8B/10B编码,这是个比较重要的概念。这一编码方式最主要的目的是“直流平衡”,即根据特定的编码表实现数据传输过程中比特“0”和比特“1”的数量基本一致,且减少连0和连1的情况。编码后的数据流具有较多的跳变,有助于接收端时钟数据恢复(CDR)。DRP/System Clock Frequency是动态重配置或系统工作时钟,通过DRP可以让设计者根据所选线速率和定义的协议实时调整收发器参数,本人没有用到,新手就不要碰了。系统时钟选择100MHz,可通过外部PLL IP核产生。

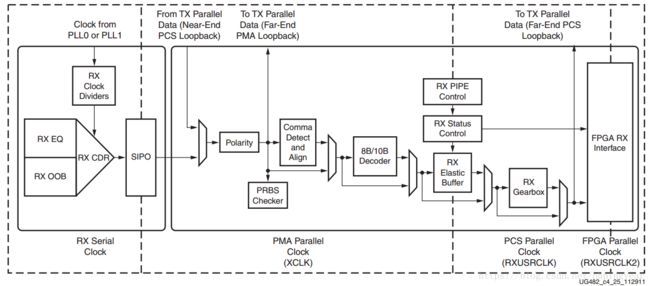

第二个重要的部分就是Synchronization and Clocking。查看ug482相关部分:

发送通道有两个并行时钟域:XCLK和TXUSRCLK。根据文档说明要保证数据正确传输,必须使用TX Buffer或者TX Phase Alignment。缺省情况下使用TX Buffer较为稳定且简单,但相比后者延迟较高。简单应用中使用Buffer即可,因此本例中TX Buffer和RX Buffer均选中。

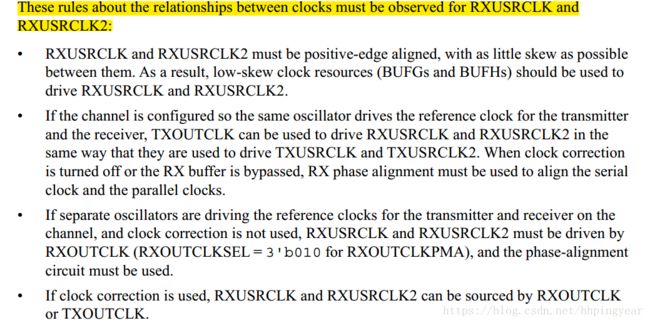

TXUSERCLK的时钟源只能是由参考时钟驱动的TXOUTCLK,而RXUSERCLK的时钟源选择根据具体情况而定:

总之就是,当使用同一个晶振作为发送器和接收器参考时钟源时,TXOUTCLK可以驱动RXUSRCLK;当使用不同晶振时,若使能clock correction才可以用TXOUTCLK驱动RXUSRCLK,否则要使用RXOUTCLK驱动。这里保持默认均使用TXOUTCLK驱动TXUSRCLK和RXUSRCLK。

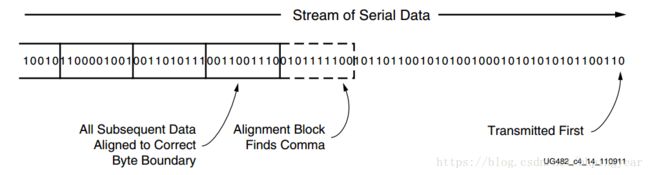

4 Comma Alignment and Equalization

这里要引入comma码的概念。8B/10B编码表中有12个控制字符,以大写字母K开头,用于一些控制功能。K码中的comma码用于接收端时钟校准和数据对齐,K28.5(对应用户数据为16’hbc)最为常见。因为数据在链路中以串行方式传输,所以接收端必须对其进行串并转换。在这一过程中,由于无法直接找到串行比特流中的每个数据的最高位或最低位比特,即使已知并行数据位宽也不能顺利转换成与发送端一致的并行数据。看下user guide中示意图你就明白了:

下边的RX Equalization是收发器自带的接收均衡器,用来补偿由于物理信道中的高频衰减引起的信号损伤,可以通过DRP动态调整,保持默认。

5 PCIE,SATA,PRBS

这一页的功能就比较高级了,说实话我不会。有需要用到PCIE的朋友可以关注下,这个虽然比较复杂,但找工作还是很有优势的,很多招聘要求中都有写!此处只把最下边的PRBS相关端口选择上,便于测试用途。

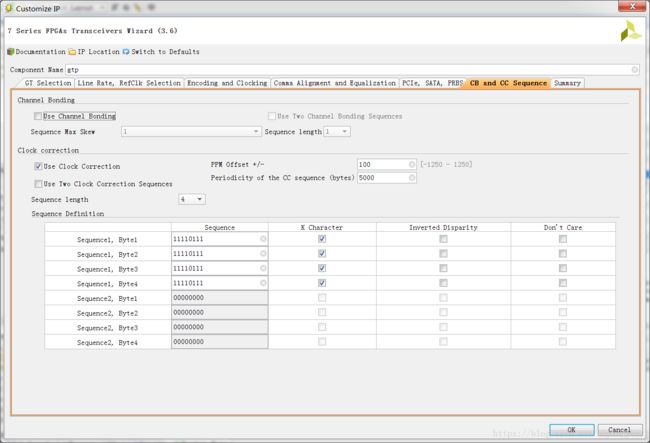

6 CB and CC Sequence

Xilinx收发器IP核支持通道绑定,将多个收发器通道“绑定”成一个速率更高的传输通道,利用FIFO消除其间的延时不确定性。Clock correction是最后一个重要的点。先来看看RX通道的结构和弹性缓存概念。

接收通道中同样有两个时钟域:从CDR恢复出的XCLK和接收通道工作时钟RXUSRCLK。RX通道使用RX Elastic Buffer来桥接两时钟域,但由于两者细微的差异会使缓存变空或溢出。为此引入时钟矫正,在发送端周期性发送一些特殊字符,接收端在弹性缓存快满时删除这些字符,快空时复制这些字符从而保证缓存内数据维持动态平衡的状态。

本例只使用一个数据通道,此页保持默认配置,不做修改。

7 Summary

看下总结页,USRCLK的时钟频率是USRCLK2的2倍,这是因为收发器内部通道数据位宽仅是外部接口位宽的二分之一,因此频率必须增大一倍才能保证数据来得及处理。可以点OK了。本文对GTP IP核的配置做了简单分析和总结,仅适用于新手。本人也在学习中,有不妥之处请在评论中指教。

XILINX 高速收发器GTP之运用

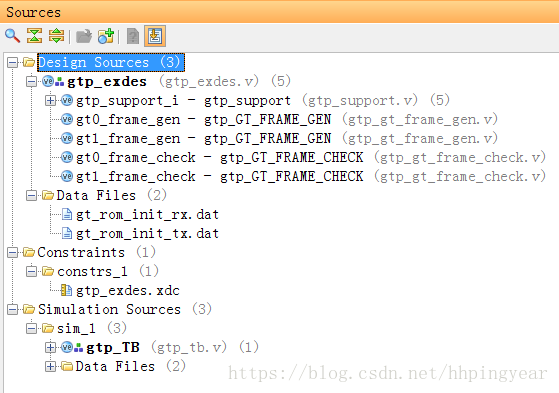

生成IP核后打开example design,先看看工程中包含的文件结构。

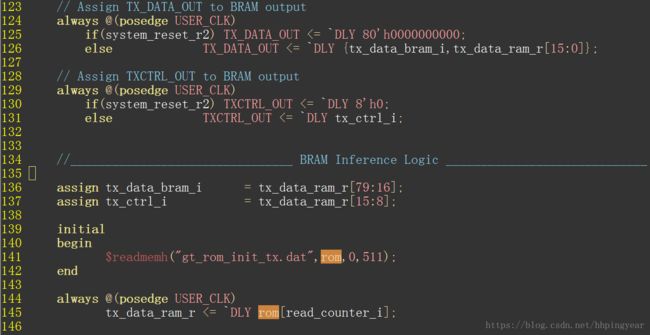

顶层文件下包含了gtp ip核系统顶层文件、frame_gen以及frame_check三类模块。frame_gen和frame_check用于测试过程中的数据包产生和接收检测(由于我在配置IP核时使能了两个通道,因此工程中有两组frame_gen和frame_check模块),gen模块读发送样式,check模块则将接收到数据与本地存储样式对比,从而判断数据传输是否正确。下面截取一段gen模块内代码:

发现gen模块是通过系统函数 readmem读取gtrominittx.dat文件来初始化rom,发送数据则直接从rom中读取。虽然 r e a d m e m 读 取 g t r o m i n i t t x . d a t 文 件 来 初 始 化 r o m , 发 送 数 据 则 直 接 从 r o m 中 读 取 。 虽 然 readmem和initial是不可综合语句,但其功能与.mif文件初始化ROM IP核是类似的。check模块与gen模块类似,但有一点比较值得借鉴。

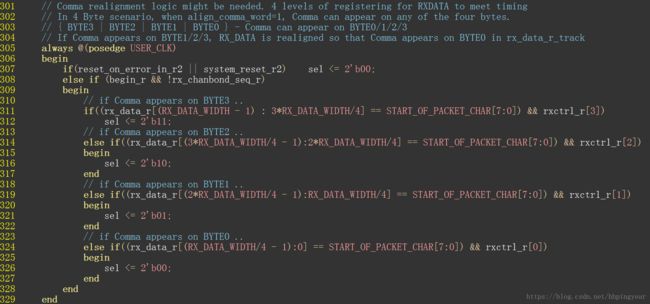

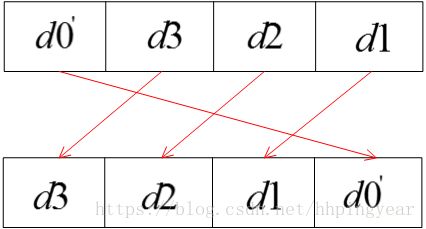

根据上边的注释可以看出,这个IP核在使用32bit用户数据位宽时,会发生错位现象。因此发送数据时所有comma码要放在32bit数据四个字节的同一字节中,最常见的是均放在最低字节,这样接收端可以根据控制字指示信号为1的位置找出错位情况,进而读数据进行重新对齐。比如当rxctrl == 4’b1000,则错误情况和重对齐方式如下:

d0’代表上一个数据的最低字节部分。其他错位情况的重对齐方式同理,现在看下check模块中根据sel信号对接收数据重对齐的逻辑。

可以看出重对齐方式与刚才讲的方法一致。因此当测试完毕后,去除frame_gen和frame_check模块并将gt数据端口开放到顶层后,接收端用户侧也要有类似的逻辑防止数据错位。

再来看下顶层文件中关于原语的使用:

IBUFDS是差分信号输入缓冲器,用来将差分信号变为单端信号。而BUFG是全局缓冲,其输出到达FPGA内部CLB IOB RAM的时钟延迟和抖动是最小的,从而使系统工作稳定。

最后,为保证最基本的通信功能,还需做三件事:

1. 去除gen和check逻辑块,并将用户数据端口开放到工程顶层;

2. 接收端用户侧例化数据重对齐模块保证接收正确;

3. 例化PLL产生100MHz时钟信号作为GTP子系统工作时钟;